传感器网络应用的低功耗实时计数器

2015-12-22张艺蒙张玉明张义门

张艺蒙,张玉明,张义门

(西安电子科技大学微电子学院,陕西西安 710071)

传感器网络应用的低功耗实时计数器

张艺蒙,张玉明,张义门

(西安电子科技大学微电子学院,陕西西安 710071)

为降低传感器网络节点的功耗,针对传感器网络应用中传感器节点休眠时间的功耗进行了分析,得出当传感器节点处于休眠状态时,其大部分功耗都是由实时计数器消耗的结论,并提出一种应用在传感器网络、采用电荷可回收逻辑电路结构的低功耗16位实时计数器.采用0.18μm的互补金属氧化物半导体工艺设计并制作了一块样片.实验结果表明,当16位实时计数器的工作频率为100 k Hz时,新结构的功耗为27 nW,而采用传统结构的实时计数器的功耗则为140 nW.

传感器网络;实时计数器;低功耗电路;电荷可回收逻辑电路

在信息化社会,传感器网络的作用越来越大,它可以帮助人们监测环境变化、气候变化和人的健康状况等[1-4].由于其特性,大部分时间传感器节点会被安置在工作人员较难达到的位置,因此其电源供给就成为一个问题.现在大多数解决方案是采用电池供电,但为了降低传感器节点的尺寸使其便于安装,电池的容量也不能太大.通常,普通家用的AAA电池可对1个传感器节点供电一至两年.因此,可通过改进算法来延长传感器的电池寿命[5].而笔者则从如何降低传感器节点的功耗进行讨论.

根据已有的研究,在大多数应用中,传感器在大部分时间都处于睡眠状态.这是因为在很多监测中,环境的变化并不是十分剧烈,数据的变化通常是以小时为单位计算的.例如在水流传感器网络中[6],传感器节点保持数小时的睡眠模式后,进入工作模式,在工作模式中运行几微秒,即监测水流速度和采集数据并发回服务器,然后又进入睡眠模式.在睡眠模式中,除了一个实时计数器来计算睡眠时间外,传感器节点中的电路均不工作.因此,实时计数器的功耗决定了传感器节点的电池寿命.

为降低实时计数器的功耗,笔者采用电荷可回收逻辑电路[7-11]来构建实时计数器,这是因为实时计数器基本上是一个时序电路,所以时钟信号同时也要作为电力驱动信号来给计数器供电.同时对时钟发生器也有要求,即它应该有足够的驱动能力来驱动计数器,同时它也应该具备回收和重复利用电荷的能力.为满足这些要求,可采用石英振荡器和电荷可回收逻辑电路技术搭建一个16位实时计数器,并用0.18μm互补金属氧化物半导体(Complementary Metal Oxide Semiconductors,CMOS)工艺进行了样片的试做.测试结果表明,相比传统静态CMOS电路搭建的实时计数器,笔者所提出的结构使传感器节点的功耗降低了81%.

1 时钟发生器

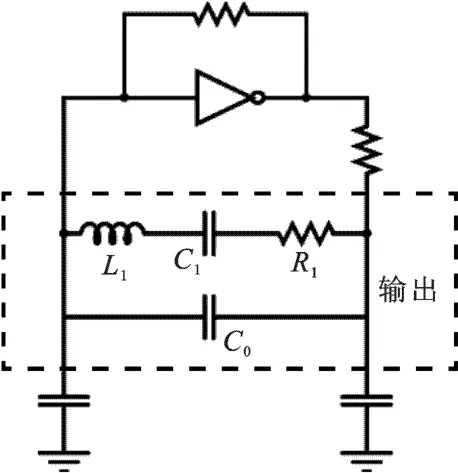

这里采用石英振荡器作为实时计数器的时钟发生器.石英振荡器是利用石英晶体(又称水晶)的压电效应,用来产生高精度振荡频率的一种电子元件,它可以等效为一个串联LCR电路.因此,该模型的阻抗可描述为s是复频率(s=jω),ωs是串联谐振角频率,ωp是并联谐振角频率.

当给石英加上电容时,会降低石英的并联谐振频率.该方法可用来调整石英振荡器的振荡频率.当只有石英的情况下,振荡器是无法起振的.因此,一些周边电路也很必要.图1给出了石英振荡器的电路结构图.为了让石英振荡器能够给电荷可回收逻辑电路供电,LCR网络必须直接与计数器相连接,从图1可知,石英振荡器的输出信号是一个正弦波,并直接和实时计数器电路相连接,满足电荷可回收逻辑电路工作的前提条件.另外,石英振荡器的品质因数Q非常高,可以达到数万,而通常在电荷可回收逻辑电路中使用的时钟发生器的Q值只有几十.因此,采用高品质因数的石英振荡器作为时钟发生器可大大提高电荷可回收逻辑电路的功耗效率.

图1 石英振荡器等效电路图

2 实时计数器

实时计数器的主要结构为二进制计数器和一些周边电路.如前所述,通常传感器节点的睡眠时间为几十分钟,因此,当工作频率为100 k Hz时,计数器至少需要28位(228/(60×100 000)约为44 min)才能达到这个量级.但28位计数器会消耗大量仿真时间,同时和16位计数器相比,其功耗并未有大幅度增长,且原理相同.因此,文中采用16位计数器作为实时计数器的主要部分,并使用了一种名为伪N沟道金属氧化物半导体(N-channel Metal Oxide Semiconductor,NMOS)增幅逻辑(pseudo NMOS Boost Logic,p NBL)的电荷[7]可回收逻辑电路来构建实时计数器.

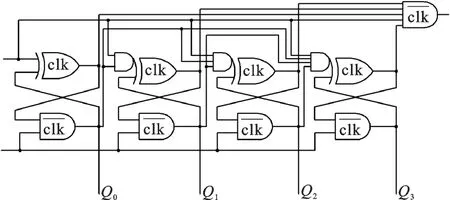

图2 pBNL搭建4位计数器结构

16位计数器由4个4位计数器组成,图2给出了由p NBL搭建的4位计数器的结构.对于通常静态CMOS搭建的计数器,当输出Q[3:0]=4’b1111时,进位输出Co=1’b1,进一步触发下一个4位计数器.但是对于电荷可回收逻辑电路p NBL,其输入和输出之间有半个时钟周期的延迟,所以要使输出Q[3:0]和Co之间没有延迟,需要对4位计数器进行重新设计,输出Co与门的输入并不是Q[3:0].在重新设计Co后,4个4位计数器被组合成一个16位计数器.

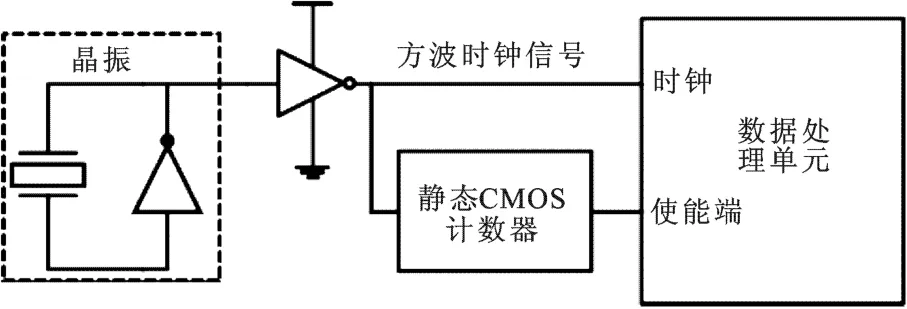

为对比所设计的实时计数器和传统结构的实时计数器之间功耗的差别,一个传统结构的实时计数器也被设计并试做出来.图3给出了一个传统结构的传感器节点的示意图,由于石英振荡器的输出信号是一个正弦波信号,无法直接作为时钟信号输入至由静态CMOS电路搭建的实时计数器,否则漏电流会十分巨大.因此,需要一个反相器将正弦波信号转换为方波信号,作为实时计数器和数据处理单元的时钟信号.当实时计数器的计数到设定值时,会产生一个启动信号使传感器节点进入工作模式;在工作模式中传感器节点开始采集周围的数据,进行数据处理并传回服务器;然后再次进入睡眠模式,工作模式持续时间非常短,相比于睡眠模式的功耗也十分小.

图3 采用传统结构的传感器节点

图4 采用新结构的传感器节点

图4为采用电荷可回收逻辑电路p NBL设计的实时计数器.新结构与传统结构不同的是,从石英振荡器中输出的正弦波信号被直接输入至实时计数器作为电源和时钟信号使用.当实时计数器计数到设定值时,会产生一个启动信号输入至数据处理单元,使传感器节点从睡眠模式进入工作模式;同时该启动信号也会打开与门,将正弦波信号转换为方波信号输入至数据处理单元作为时钟信号.和传统结构一样,在工作模式结束后,传感器节点会转入睡眠模式,实时计数器继续进行计数.

通过对比图3和图4可以发现,这两种结构有着两个最主要的不同点:①对于新结构,正弦波转方波的部件只工作在工作模式,而传统结构则需一直工作;②新结构采用了p NBL这种电荷可回收逻辑电路来构建实时计数器.通过这两点的改进,传感器节点的功耗可被大大降低.

3 仿真和测试结果

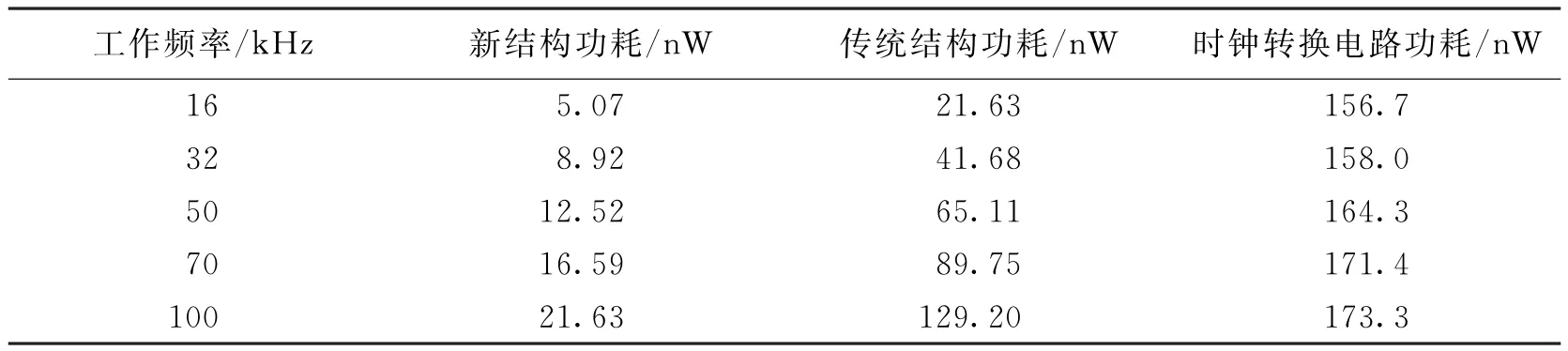

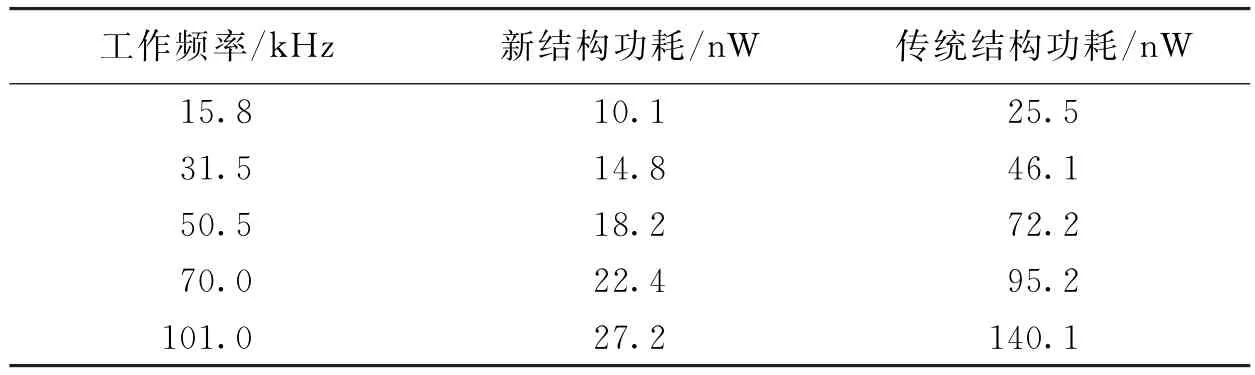

为验明文中提出的结构和传统结构相比具有所预期的低功耗效果,文中设计并制作了两种结构的芯片,并进行了仿真和测试,仿真和芯片试做均采用了0.18μm CMOS标准工艺,仿真结果如表1所示.工作频率范围在16~100 k Hz区间,传统结构包括了实时计数器和时钟信号转换电路两部分的功耗,而新结构则不需要转换电路,只包括了实时计数器的功耗.从仿真结果来看,转换电路的功耗一直在150 n W以上,这部分巨大的功耗在新结构中被成功消除了,只比较实时计数器本身.当工作频率为100 k Hz时,新结构的功耗只有传统结构的16%,如果加上时钟信号转换电路的功耗,则在工作频率为100 k Hz时,新结构能够节省280 nW的功率,将传统结构的功耗降低了92%.

表1 两种不同结构的仿真结果

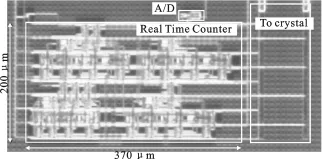

图5是试做芯片的显微镜照片.由于是手工版图布线,只对功能和功耗进行了考虑,对芯片尺寸没有优化.可以看到,芯片面积利用率不够充分,在实际应用中还可以进一步进行优化,从而降低电路的面积,表2为测试结果.为只对实时计数器本身进行比较,对传统结构的测试结果只包括实时计数器,而不包括时钟转换电路.图6给出了仿真结果和测试结果的比较,可看出测试结果和仿真结果有着很好的拟合,从而验证了所提出的新结构有着很好的低功耗性能,对传感器节点的低功耗长寿命有着十分显著的效果.

图5 试做芯片的显微镜相片

图6 仿真结果和电路测试结果的比较

表2 试做芯片的测试结果

4 结束语

文中提出了一种应用在传感器网络中的新的实时计数器的结构,通过采用这种结构,可以大幅降低传感器节点的功耗,从而延长传感器节点的电池寿命.通过对所提出电路结构的仿真和试做测试结果分析,得到所提出新结构相较于传统结构的功耗有着大幅的降低,在100 k Hz工作频率下,高达81%的功耗被降低,加上新结构所去除的时钟转换电路的功耗,则高达92%的功耗被降低.

[1]Gonzalez M,Schandy J,Wainstein N,et al.Wireless Image-sensor Network Application for Population Monitoring of Lepidopterous Insects Pest(Moths)in Fruit Crops[C]//Proceedings of IEEE International Instrumentation and Measurement Technology Conference.Piscataway:IEEE,2014:1394-1398.

[2]Munir A,Gordon-Ross A,Ranka S.Multi-core Embedded Wireless Sensor Networks:Architecture and Applications [J].IEEE Transactions on Parallel and Distributed Systems,2014,25(6):1553-1562.

[3]Singh V,Singh I P,Sud S K.Low Power Embedded Controlled Sensor Network for Agricultural Application[C]// Proceedings of IEEE Long Island Systems,Applications and Technology Conference.New York:IEEE,2014:1-4.

[4]Borges L M,Velez F J,Lebres A S.Survey on the Characterization and Classification of Wireless Sensor Network Applications[J].IEEE Communications Surveys&Tutorials,2014,16(4):1860-1890.

[5] 杨银堂,高翔,柴常春,等.一种WSN中的能耗优化动态路由算法[J].西安电子科技大学学报,2010,37(5):777-782. Yang Yintang,Gao Xiang,Chai Changchun,et al.Novel Dynamic Routing Algorithm for Energy Optimization in WSN [J].Journal of Xidian University,2010,37(5):777-782.

[6]Melani M,Bertini L,De M M,et al.Hot Wire Anemometric Mems Sensor for Water Flow Monitoring[C]// Proceedings of Design,Automation and Test in Europe.Piscataway:IEEE,2008:342-347.

[7]Zhang Y M,Huang M S,Wang N,et al.Energy Efficient Processing Engine in LDPC Application with High-speed Charge Recovery Logic[J].Journal of Semiconductor Technology and Science,2012,12(3):341-352.

[8]Wang A,Chandrakasan A.A 180 m V FFT Processor Using Subthreshold Circuit Techniques[C]//Digest of Technical Papers of the IEEE International Solid-state Circuits Conference:4.Piscataway:IEEE,2004:292-293,285,529.

[9]Kao J,Ma W H,Sathe V,et al.A Charge-recovery 600 MHz FIR Filter with 1.5-cycle Latency Overhead[C]// Proceedings of the 35th European Solid-state Circuits Conference.Piscataway:IEEE,2009:160-163.

[10]Zhang Y,Okamura L,Yoshihara T.An Energy Efficiency 4-bit Multiplier with Two-phase Non-overlap Clock Driven Charge Recovery Logic[J].IEICE Transactions on Electronics,2011,E94-C(4):605-612.

[11]Ou T C,Zhang Z Y,Papaefthymiou M C.An 821 MHz 7.9 Gb/s 7.3 pJ/b/iteration Charge-Recovery LDPC Decoder [C]//Digest of Technical Papers of the IEEE International Solid-state Circuits Conference:57.Piscataway:IEEE,2014:462-463.

(编辑:齐淑娟)

Low power dissipation real time counter for sensor network application

ZHANG Yimeng,ZHANG Yuming,ZH ANG Yimen

(School of Microelectronics,Xidian Univ.,Xi’an 710071,China)

In sensor network application,to calculate the sleeping time of the sensor nodes,the real time counter is an important part.When the sensor node is in the sleep mode,most of power dissipation is consumed by the real time counter.How to reduce the power dissipation of the real time counter becomes an important research topic to extend the battery life in senor network application.This paper presents a low power dissipation 16-bit real time counter for sensor network application.Charge recovery logic technology is adopted in the real time counter to achieve low power dissipation.To demonstrate the performance of the proposed real time counter,a test chip is designed and fabricated by 0.18μm CMOS technology.Experimental results indicate that the proposed real time counter with a charge recovery logic dissipates only 27 nW when working at the frequency of 100 k Hz,while the conventional structure of the real time counter dissipates 140 nW in total.

sensor network;real time counter;low power;charge recovery logic

TN432

A

1001-2400(2015)06-0066-04

10.3969/j.issn.1001-2400.2015.06.012

2014-12-17

时间:2015-03-13

国家自然科学基金资助项目(61372015)

张艺蒙(1982-),男,讲师,博士,E-mail:zhangyimeng@xidian.edu.cn.

http://www.cnki.net/kcms/detail/61.1076.TN.20150313.1719.012.html