基于FPGA的弹载数据回读系统设计*

2015-11-18郝晓明胡陈君石玺文

郝晓明,李 杰,2*,胡陈君,石玺文,陈 伟

(1.中北大学电子测试技术国防科技重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051;3.山西北方惠丰机电有限公司科研设计二所,山西长治 046012)

基于FPGA的弹载数据回读系统设计*

郝晓明1,李 杰1,2*,胡陈君1,石玺文1,陈 伟3

(1.中北大学电子测试技术国防科技重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051;3.山西北方惠丰机电有限公司科研设计二所,山西长治 046012)

惯性传感器在各种导弹武器中的广泛应用,使得采集存储系统成为弹体飞行参数测量中不可或缺的存储设备。基于采集存储系统数据读取的需要,设计了一种基于FPGA的弹载数据回读系统。本系统以FPGA为控制核心,FT245BL芯片为USB控制芯片,FPGA模拟的FIFO为数据缓存,从而实现数据的传输。试验验证表明,该回读系统能够很好地完成数据传输工作,且传输数据迅速、准确,无错帧与丢帧现象,具备一定的工程实用价值。

惯性导航;数据回读;FPGA;USB;FIFO

随着惯性传感器的发展,MEMS惯性导航成为各种导弹导航首选系统。例如火箭弹常采用低成本的MEMS惯性器件测量其飞行姿态[1-2]。而出于隐蔽性和安全性的考虑,炮弹飞行过程中惯性传感器所采集记录的数据信息不可能实时地传输到上位机进行处理与显示,需要先将数据存储到FLASH存储器中,回收后再将数据回读到上位机进行处理再现。

传统的数据传输系统由于传输速度低或安装不方便等问题已不能满足科研与生产过程的需求[3],而USB具有支持热插拔,使用灵活,传输速率快,易于扩展的特点,优于其它的数据传输方式[4-5]。文献[6-7]提到的 USB控制芯片CY7C68013,数据传输速度快,应用广泛,但固件程序和驱动程序的编写复杂,需要经验丰富的专业人士才能完成设计。

炮弹从上电装膛到飞行落地时间很短,FLASH存储器中记录的有效数据很少,用USB 2.0的传输速度就可以在短时间内读取。本文正是针对上述情况设计了一种简易的基于FPGA的弹载数据回读系统。

1 总体设计方案

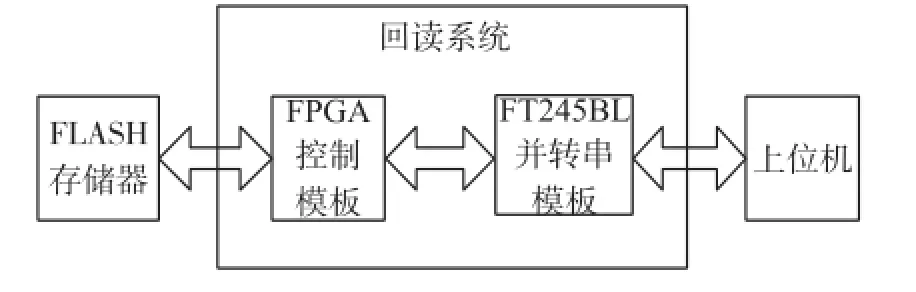

该系统主要由三个模块构成:电源模块,FPGA模块,FT245BL模块。系统设计图如图1所示。

图1 系统设计图

FPGA为控制芯片,读取上位机命令,控制FT245BL的转换和传输。上电后FPGA处于待命状态,上位机发送命令给FPGA,FPGA接到命令后,根据通讯协议判断命令内容,然后根据命令内容进行相应操作。若收到读取命令,FPGA将会从FLASH中读取数据,经过FPGA的FIFO缓存后送入FT245BL中进行并串转换,然后通过USB接口上传到上位机。

2 系统硬件设计

整个硬件电路分为三个模块:电源模块,FPGA控制模块,FT245BL转换模块。

2.1 电源模块

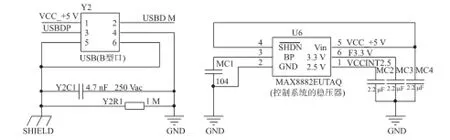

USB供电方式有总线供电和自供电两种方式。总线供电时突然加大电压会产生大电流烧毁器件,所以需要用电压转换器,MOS管等使电流缓慢增大,但电流逐渐增大会加大磁场效应,所以还要加磁珠来减小噪声和电磁干扰;而从USB口自供电设计简单,如图2所示,USB电源线电压为5 V,提供的最大电流为500 mA,不用考虑电压和磁场问题。当USB总线连接到主机时,USB主线电压变高,RESET电压变高,导致RSTOUT电压变高,所以USB DP管脚接一个1.5K的上拉电阻连到RSTOUT引脚,钳位到高电平,驱动能力增加,芯片迅速连接到主机。

所以设计整个系统的供电由USB口提供+5 V电压,由于FPGA的I/O口需要+3.3 V供电,内核需要+2.5 V供电,所以选用了一片电源转换芯片MAX8882把+5 V电压转换为+3.3 V和+2.5 V。

图2 系统供电设计图

数字电路中,如果电源线和地线上的噪声不进行滤波,就会耦合到有用信号上,形成电磁干扰,所以每一个电源都要加4个1 μF的接地电容进行滤波。

USB接口的信号地与保护地要分割开,它们之间可以用一个大电阻并联一个耐压值较高的电容来连接。如图3所示。

图3 USB供电与接地电路

2.2 FPGA模块

主控芯片选取XILINX公司的FPGA芯片XC2S30,FPGA为复杂逻辑控制提供了丰富的门阵列资源,具有高速,低功耗,高集成度的特点,设计的产品具有体积小,重量轻,集成度高,功耗低的特点,使产品具有更好的性价比和竞争力,设计周期缩短,设计费用和风险降低[8]。这款FPGA芯片内核供电电压2.5 V,I/O口供电电压3.3 V,芯片功耗低,解决了发热量大的问题;而且芯片拥有30 000个系统门,216个可编程逻辑模块,92个I/O口,内部集成6个双口RAM,共24 kbit,能够满足本次设计要求。

FPGA可以严格的控制时序,使系统高速运行,所以用FPGA内部来进行初始化,复位和判断调用各个模块单元[9]。FPGA配置主要包括时钟单元,程序下载单元,指示灯单元。时钟单元采用20M有源晶振产生主时钟,通过软件分频提供给其它器件进行工作;程序下载单元考虑到JTAG链的完整性、电源电压的设置以及CCLK信号所以采用主串模式连接;指示灯单元用两个指示灯来显示上电成功和擦除成功。

2.3 FT245模块

USB接口芯片选取的是FTDI公司的FT245BL芯片[10]。传统的USB接口设计需要对USB的标准,固件编程,驱动程序的开发等有很深入的了解,工作量大,开发周期长,有丰富设计经验的人员才能完成这项任务,而FT245BL芯片内部只有一个单独的USB 2.0串行接口引擎(SIE)和FIFO收发缓冲区,在芯片上有完整的USB协议,无需外扩程序固件,而且FTDI公司提供驱动程序,我们只需进行必要的硬件设计和简单的软件编程便可应用。所以选用FT245BL。

FTDI公司对FT245BL的设计建议使用外扩EEPROM芯片93C46来存放FT245BL芯片的设备描述符,但考虑到EEPROM只是存放原始设备制造商提供的PID,VID和设备描述符等,而在本次设计中,只使用设备默认值就可以正常使用,为了最简化设计,去除了EEPROM的设计。

3 系统软件设计

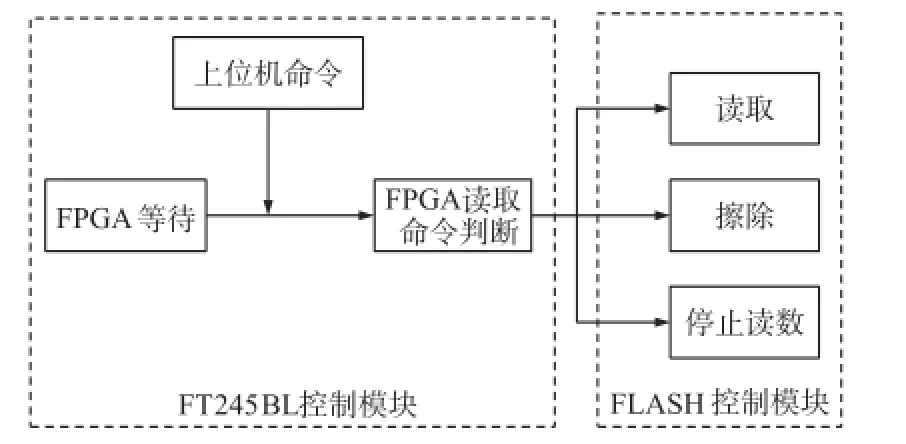

系统软件分为两个模块:FT245BL控制模块,FLASH控制模块。如图4所示。

图4 系统软件设计图

3.1 FT245BL控制模块

FT245BL控制模块主要分为两单元:通信协议判断,FIFO缓存。

3.1.1 通信协议

FPGA在与上位机通信之前,需要先与上位机规定好通信协议,根据通信协议,上位机作为主设备,FPGA作为从设备,FPGA根据通信协议响应上位机发出的命令,从而实现上位机通过USB读取FPGA内FIFO数据[11]。系统和上位机约定的命令字[12]为:

读数命令:&25&5E&77&A6

擦除命令:&25&5E&44&A3

停止读数命令:&25&5E&66&A5

命令字是以16进制数编写,当FPGA接收到命令字后将16进制转换为2进制识别。开始上电后FPGA处于等待状态,当接收到上位机传递来的命令字后,中断当前操作,然后根据命令字执行相应的操作。

3.1.2 FIFO缓存单元

这款FPGA中内置了1 kbit×8 bit的RAM可用于FIFO缓存。由于FLASH中数据需要一页一页读取,当翻页时需要重新写入控制字和地址,所以为了不发生丢失数据的情况,需要将数据在FIFO中缓存,再送入FT245中。

在进行数据缓存时,系统采用分层处理,分为两层缓冲区,分别是数据接收缓冲区和数据发送缓冲区[13]。数据接收缓存区接收从FLASH中传来的数据,接收一帧后将数据送入数据发送缓冲区。

FIFO,即先进先出,目的是对数据进行缓存,不使数据发生丢失。主要流程是:FIFO中写入一帧数据,写地址计数加一,FIFO往外送出(被读取)一帧数据,读地址计数加一;比较两个地址之间的差值,

若写地址大于读地址,则

Offset<=(wrcont-rdcont);

若读地址大于写地址,则

Offset<=("1111111110"-(rdcont-wrcont));

若写地址等于读地址,则

Offset<="0000000000";

其中,wrcont为写地址计数,rdcont为读地址计数,Offset为FIFO中数据容量。计算FIFO中数据的容量,设计一个标志位f_half,若数据容量占FIFO总容量一半以上,则标志位置1,停止向FIFO中写入数据;若数据容量不到FIFO总容量一半,则标志位置0,继续写入数据;若Offset为0,则表示当前FIFO为空,可以向FIFO中写入数据;因为若FIFO存满1K再向FT245BL中发送数据,就有可能造成系统自动掉电后,部分写入FPGA中的数据没有及时发送给FT245BL,从而造成数据丢失,所以设计只要FIFO不为空,就持续向FT245BL中发送数据[14]。

在vhdl语言中,经常要用到变量和信号两种数据对象。变量的赋值是立即发生的,很容易进行仿真,信号是进程被挂起时赋值,具有延迟特性,更符合实际的硬件特性,所以实际应用时多使用信号在电路内部进行传递,只有在描述一些用信号很难描述的算法时才会使用变量[15]。

由于wrcont,rdcont,offset,f_half都是信号,更接近硬件的实际情况,需要一定的延迟,数据因延迟传输可能在FIFO中满溢,从而造成的数据丢失。所以用"1111111110"代替"1111111111"作为FIFO总容量计算FIFO中数据的容量,而且半满就停止向FIFO中写入数据。

3.2 FLASH控制模块

FLASH控制模块主要分为三单元:读取,擦除,停止读数。

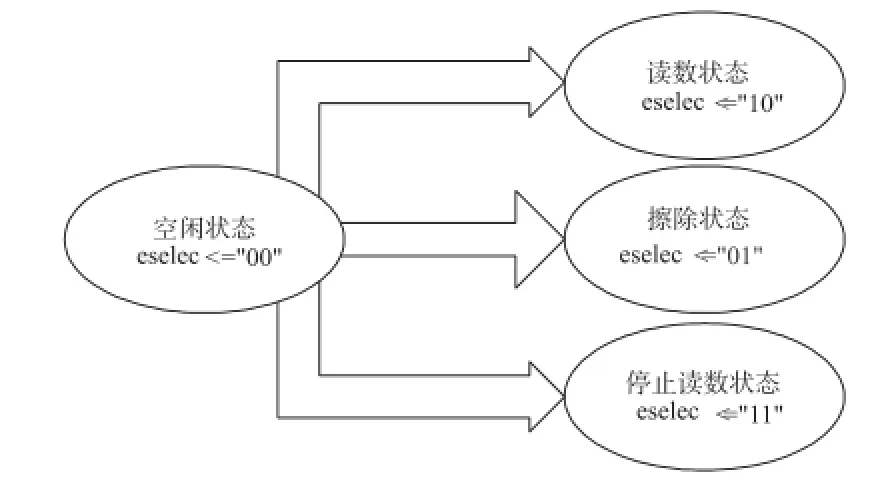

FPGA对命令字进行识别判断后,执行下相应的操作:读取,擦除,停止读数。状态转换图如图5所示,eselec为选择操作信号。

3.2.1 FLASH读取单元

当FPGA得到读取命令后,就将数据从FLASH中取出,放入其内部的FIFO中,将数据从FLASH中读取到其内部FIFO中;FPGA内部FIFO中存有数据时,会向FT245BL发送数据,使FT245BL的发送缓存器接收数据,然后通过串行接口引擎(SIE)将8位并行数据转换为串行数据,通过USB口的差分形式传输到上位机。

图5 FPGA中状态转换图

FT245BL中有128 byte的接收缓存FIFO和384 byte的发送缓存FIFO与FPGA的FIFO相连接。

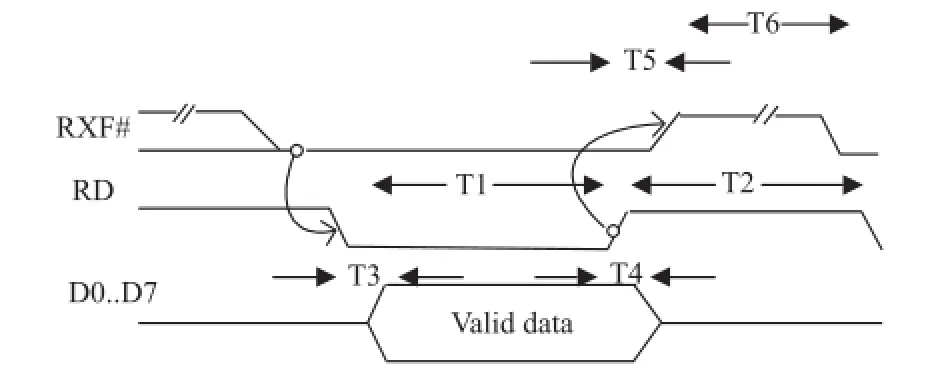

当FT245BL接收到来自上位机的命令后,写入接收FIFO,接收FIFO不为空时,接收信号RXF置低,表示接收区FIFO有数据,可以进行读取,在RD信号由高变低后,命令数据被挂在端口上,当数据被FPGA读取后,RD信号由低变高,表示一个字节读取完成,接收信号RXF有短暂的升高表示FT245BL在处理读操作,然后变为低电平表示可以读取下一字节。之后循环操作直到数据全部读取完毕,接收信号RXF置高。读时序如图6所示。

图6 FT245BL读时序图

当FT245BL接收到来自FPGA FIFO中的数据后,此时发送信号为低,表示可以向发送FIFO中写入数据,当写信号置高时,数据放置在FT245BL的端口,当写信号由高变低时,数据写入发送FIFO。当FIFO中数据写满或正在写时,TXE信号置高,停止写入数据。FT245BL写时序如图7所示。

图7 FT245BL写时序图

3.2.2 FLASH擦除单元

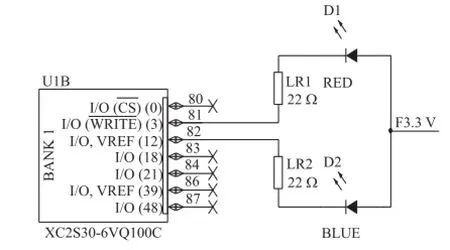

当FPGA得到擦除命令,FPGA就擦除FLASH中的所有数据,擦除完成后将信息反馈给上位机,并点亮擦除完成指示灯(电路图如图8,D1为上电指示灯,D2为擦除完成指示灯)。

图8 上电与擦除完成指示灯

3.2.3 FLASH停止读数单元

当FPGA得到停止读数命令,就停止一切操作并回到复位状态。

4 系统测试

本系统进行了实物焊接与调试。实物图如图9所示。

图9 实物图

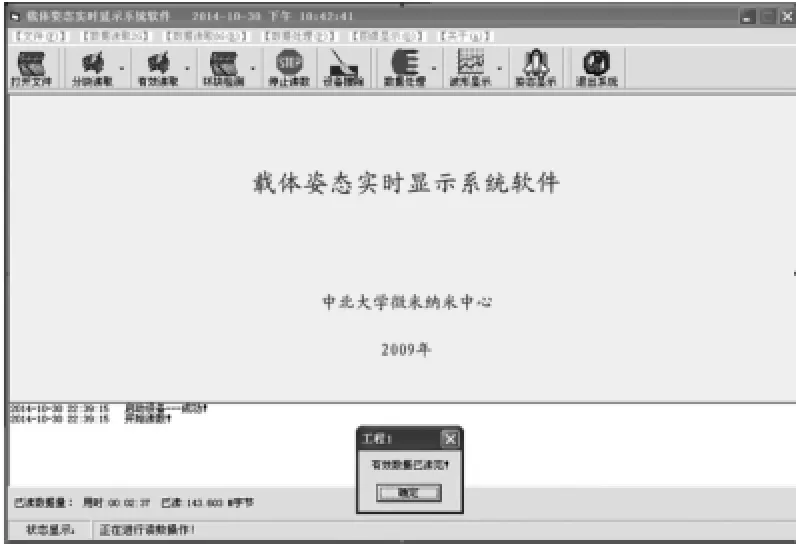

采用VB程序编写的上位机软件进行测试,测试结果如图10所示。由结果可以看出,本系统在读取143.603 Mbyte的数据时用时为157 s,读数速度为0.915 Mbyte/s左右,而FT245BL芯片规定的传输速度为1 Mbyte/s,传输速率为规定速度的91.5%。经过检验,读取的数据没有出现丢失,错误等现象,说明本系统具有很好的数据读取稳定性,可靠性,完全可以应用于弹载等需要回读的试验中。

图10 测试结果

5 结束语

本文介绍了一种基于FPGA的弹载数据回读系统,该系统采用FPGA作为核心控制器,充分发挥了FPGA可编程能力强的特点;采用FPGA内部的FIFO作为缓存,保证了数据的完整性;确定了与上位机的通信协议,保证了传输的高效性;使用FTDI公司的FT245BL芯片,不使用EEPROM,设计简单。测试表明该套系统实用性强,可以满足一般的工程型应用。

[1] 董进龙,莫波.典型弹道下的火箭弹MEMS-INS/GNSS组合导航姿态误差可观性分析[J].兵工学报,2014,3(56):850-856.

[2] 卢晓东,周军,贺元军.直接侧向力控制火箭弹的微机电系统速率陀螺滤波方法[J].兵工学报,2011,32(12):1456-1461.

[3] 吕超,张玉霞,王立欣.USB接口高速数据传输的实现[J].计算机测量与控制,2009,17(5):1003-1005.

[4] 胡亚琦,李炜,杨栋.基于USB2.0的振动监测系统的研究与设计[J].计算机测量与控制,2012,20(7):1809-1811.

[5] 代月松.USB3.0在存储测试系统中的研究[D].太原:中北大学,2013.

[6] 刘吉,杨德伟,文怀涛,等.基于USB通信的FPGA高速数据采集系统[J].现代电子技术,2011,34(10):186-192.

[7] 高贝.基于USB2.0的数据传输系统设计[D].西安:西安电子科技大学,2011.

[8] 王红亮,黄洋文.基于FPGA的可程控多路信号源设计[J].火力与指挥控制,2010,35(6):97-99.

[9] 刘双红,张海龙,靳摇鸿,等.基于FPGA和WSN的TNT爆炸时刻采集及存储系统[J].传感技术学报,2013,26(7):1009-1013.

[10]FT245BL.Datasheet [EB/OL].http://wenku.baidu.com/view/ e8b0563610661ed9ad51f39a.html.

[11]黄土琛,宫辉,邵贝贝.基于USB和FPGA的多功能数据采集系统[J].原子能科学技术,2013,47(11):2172-2176.

[12]柯艳,李杰,孔祥雷,等.基于USB 2.0的多路数据采集系统上位机软件设计[J].测试技术学报,2010,24(4):351-356.

[13]杨海波,徐元欣,徐摇文,等.水下移动平台数据采集和传输系统设计[J].传感技术学报,2014,27(3):361-367.

[14]李杰,马幸,刘俊,等.小型惯导系统数据实时采集处理与存储设计[J].中国惯性技术学报,2008,16(3):274-277.

[15]杨丹,张树林.VHDL中信号与变量的教学体会[J].电子电气教学学报,2006,28(3):30-35.

郝晓明(1988-),男,河北邢台人,现中北大学在读硕士研究生,主要从事微系统集成、惯性测量方向的研究;

李 杰(1976-),男,教授,博士生导师。现在中北大学电子测试技术国家重点实验室工作,目前的主要研究方向为微系统集成理论与技术、惯性感知与控制技术、组合导航理论、计算几何及智能信息处理等,Lijie@nuc.edu cn。

DesigningofReadoutSystemforMissile-LoadedDataBasedonFPGA*

HAO Xiaoming1,LI Jie1,2*,HU Chenjun1,ShI Xiwen1,CHEN Wei3

(1.North University of China Science and Technology on Electronic Test&Measurement Laboratory,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science&Dynamic Measurement(North University of China),Ministry of Education,Taiyuan 030051,China;3.Shanxi North Huifeng Mechanical&Electronic Co.Ltd No.2 Academic Institution,Changzhi Shanxi 046012,China)

Wide use of inertial sensors in various kinds of missile weapons makes it indispensible for data acquisition and storage system in flight parameter measurement of projectile.Based on the need for data reading of acquisition and storage system,designed a kind of FPGA-based data reading system.By adopting FPGA as the core control,FT245BL as USB control chip,FIFO simulated by FPGA as data cache,this system completes the function of data transmission.The experiment shows that this data reading system is able to complete the function of data transmission quickly and accurately without frame error or frame losing,having engineering practical value.

inertial navigation;data transmission;FPGA;USB;FIFO EEACC:1265A

TN108.7

A

1004-1699(2015)07-1023-05

10.3969/j.issn.1004-1699.2015.07.014

项目来源:武器装备探索研究项目(7131017)

2014-12-08 修改日期:2015-03-27