基于USB3.0与FPGA的多轴运动控制器开发*

2015-11-04顾定富罗福源

顾定富,罗福源

(南京航空航天大学机电学院,南京 210016)

基于USB3.0与FPGA的多轴运动控制器开发*

顾定富,罗福源

(南京航空航天大学机电学院,南京 210016)

USB3.0技术的出现使得USB串行接口不仅具有即插即用、支持热插拔等特点,而且提高了数据传输的速率,在此背景下,这里提出了基于USB3.0通信接口的运动控制器设计。文中对运动控制器的总体结构进行了设计并对主要芯片进行选型,利用USB3.0接口高达5Gbps以及全双工工作模式的特点,自定义了数据差错控制与数据双向传输的新通信协议。控制器采用FPGA作为主控芯片,采用SOPC的设计方法,运用Verilog HDL语言设计出运动控制器的精插补、编码器信号细分辨向等模块。最后的仿真验证了该运动控制器有效性与可行性,为USB3.0产品的开发提供了参考。

USB3.0;精插补器;运动控制器;FPGA

0 引言

运动控制器是现代数控系统的核心。运动控制器经历了一个漫长的发展。早先,运动控制器基于模拟器件实现,随着电力电子技术的发展,目前,基于PC的开放式运动控制器已经成为数控技术发展的主要方向[1]。早期,PC与运动控制器之间的连接主要通过PC机的串口、并口或者ISA/PCI总线等通信接口。但是,串口、并口虽然连接简单、方便,开发成本低,但是其传输速度慢,不能满足运动控制器的高实时性要求;PCI总线是目前主流的通信总线,其速度也能满足实时性,但其开发难度大,成本高,而且便携式计算机都没有PCI插槽,所以在现场使用很不方便。USB2.0虽然也具有连接方便、简单等特点,但随着存储数据的变大,USB2.0的速度存在很大的局限性。2008年推出的USB3.0技术很好的解决了之前通信总线使用便利性与传输速度的矛盾,USB3.0继承了USB2.0的特性,比如即插即用,功耗低,连接简便,价格便宜等优点,此外由于USB3.0采用了新的传输技术[2],不仅使得传输速度是USB2.0的10倍,达到5Gbps(640MB/ S),而且采用了双通道的输模式,可以实现全双工传输,使得它非常适合用于PC与控制器之间的数据传输。另一方面,随着计算机技术与半导体制造工艺的发展,FPGA芯片的性能突飞猛进,单片FPGA已经能够独立承担运动控制系统的大部分信号处理与控制运算任务。跟以往采用DSP+FPGA实现的运动控制器相比,完全基于FPGA设计的运动控制器具有成本低、速度快、结构紧凑、可靠性高的优点[3-4]。因此,利用USB3.0的高速传输与开放式,可进一步显著提升运动控制器的便携性、实时性。

1 运动控制器总体结构设计

1.1 系统总体结构

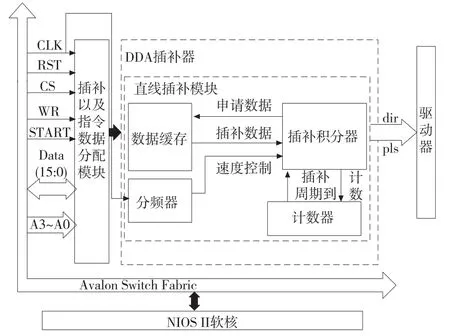

设计的插补器采用上下位机的结构形式,数据采样插补的粗插补阶段由上位机PC来实现,精插补阶段由FPGA模块实现,采用这种不同于传统的两级插补分离的设计方式,不仅充分利用了PC的资源,而且由于不再使用DSP处理器,使得下位机运动控制器的设计变得简单,方便,降低了开发的成本。PC与运动控制器的数据通信管道采用具有超速特性的USB3.0接口,粗插补数据通过USB3.0接口传到运动控制器,由FPGA完成精插补并输出驱动脉冲。运动控制器硬件电路主要由USB3.0接口芯片CYUSB3014和FPGA(型号为EP3C40F484)、EEPROM(型号为24LC256)以及外围处理电路如:位置反馈信息预处理电路、AD转换电路、PWM模拟输出电路、开关量I/O接口电路组成,整体结构如图1所示。

图1 运动控制器结构框图

1.2 重要芯片选型分析

在调研现有运动控制器功能的基础上,提出了本运动控制器所要求的主要功能,具体如下:

(1)具有超速的主机通信接口,实现PC与运动控制器的实时通信,确保运动控制器的实时性,为此选择CYUSB3014作为通信接口。CYUSB3014具有超速的传输速度5Gbps以及双通道的传输模式。CYUSB3014接口芯片负责所有与USB传输事务相关的任务,对粗插补数据和控制指令数据进行收发,以及对数据的打包和校验。

(2)具有4轴脉冲信号输出功能,实现4轴步进或伺服控制,脉冲输出可调,范围为286Hz~75MHz;4路增量式光电编码器输入信号接口,可接受2MHz的编码器信号;伺服控制周期为250μs,具有较高的伺服频率,为了能实现以上的性能,这里选择高性能FPGA(型号为EP3C40F484)作为主控芯片。EP3C40F484具有150MHz的主频,内部具有丰富的物理资源,用它获得粗插补数据,调用内部实现的DDA精插补模块[5-6]对数据精插补,并输出控制脉冲。

2 USB3.0通信接口设计

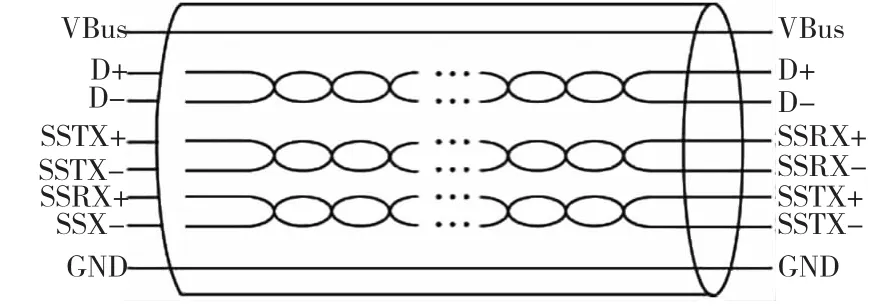

USB3.0接口芯片采用的是USB业界领头羊Cypress公司推出的CYUSB3014,该款控制器的数据传输速度达到了5Gbps,传输速度已经是USB2.0的10倍,其内部集成了200MHz的ARM9的核(ARM926EJ-S)、512K字节的RAM和USB 3.0物理层[7]。USB3.0接口相比于USB2.0在物理接口方面也有很大的调整,USB主机与从机之间采用USB线缆相连接,USB3.0中定义了8根信号线,比USB2.0多了SSTX+,SSTX-,SSRX+,SSRX-四根数据线,这使得USB3.0可以工作在全双工状态。利用USB3.0超速以及全双工的特性,进行了设计。

2.1 运动控制数据的组织规划

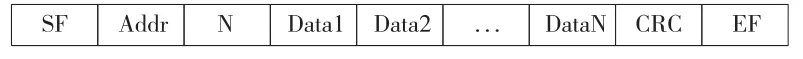

PC与运动控制器通信采用数据帧作为传输的基本单位,帧格式如图2所示。

图2 数据帧格式

·SF(8位):数据帧的起始标志,编码为01111110。

·Addr(16位):数据帧所要存放的的位置信息。

·N(16位):表示数据帧内包含用户数据的数量,默认最大传输65536个数据包。

·Data(4*32位):用户数据包,包含了运动控制所需的各种信息。

·CRC校验(16位):为了防止数据传输过程中发生错误,采用了CRC-16的差错检验,提高通信的可靠性。

·EF(8位):数据帧结束标志,编码为01111101。

2.2 数据传输差错检测与控制

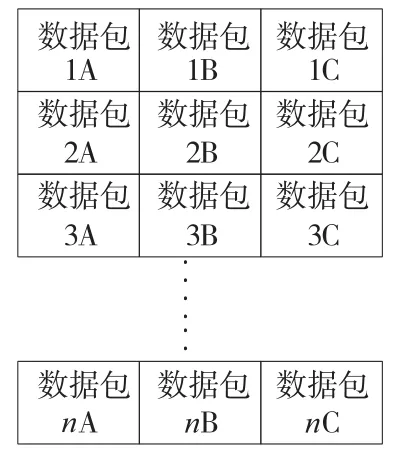

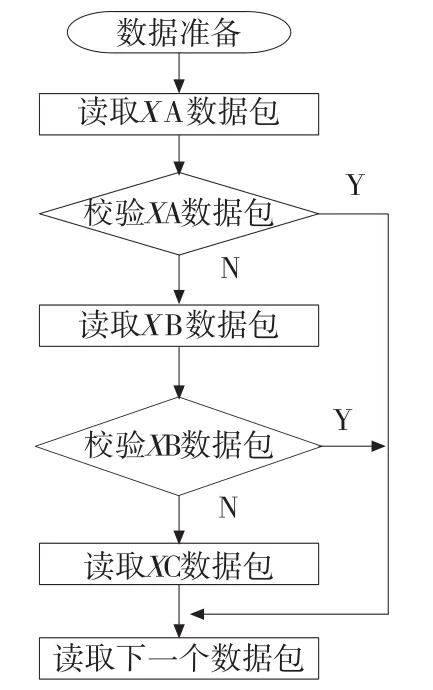

无论通信系统如何可靠,都不可能做到完美无缺,受热噪声和冲击噪声等干扰因素的影响,数据在传输过程中会发生错误或丢失,而运动控制对数据的正确性要求非常高,因此,必须考虑如何发现和纠正信号传输中的差错。USB3.0的数据传输速度已经达到5Gbps,在这样的超速传输速度下,完全可以采用数据冗余的设计方法,即将PC产生的粗插补数据进行备份式传输,每个数据包都将发送三份到运动控制器,图3表示的是数据包组织形式,其中X B、X C的数据包作为备份的数据包跟X A的数据完成一样(X为数据的序列号),正常情况下,控制器存取的都是X A的数据包,而如果X A的数据包出现错误,控制器可以读取X B或X C的数据包,不需要通知PC机进行重新发送,所以采用此数据传输协议提高了数据传输的效率,确保了运动控制的实时性,读取流程图如图4。

图3 数据包组织形式

图4 数据读取流程图

2.3 双向数据通道设计

USB3.0物理层结构模型如图 5所示。图中SSTX+,SSTX-,SSRX+,SSRX-是USB3.0相对于USB2.0新增的四根数据线,可见USB3.0可以工作在全双工的通信模式。利用这一特点,通过对运动控制数据的分析,把运动控制指令与运动控制状态反馈数据分别使用发送和接收两条通信管道进行同时传输,从而缩短通信时间开销,增强运动控制器的实时性,提高数据传输的效率。具体分配如下:

1)数据发送(SSTX+,SSTX-):主要是由PC发送到运动控制器的数据,包括粗插补数据,命令控制数据,数字量输出等。

2)数据接收(SSRX+,SSRX-):PC接收运控控制器数据的主要通道,包括外部I/O输入,编码器数据,运动控制器运行状态监控,以及控制器内寄存器数据的上传等。

图5 USB3.0物理层结构模型

3 基于FPGA的运动控制模块设计

所设计的运动控制器仅采用FPGA作为主控芯片,这与以往的DSP+FPGA有着本质的区别。USB3.0提供的超速传输速度,可以把数据采样插补的粗插补阶段放到PC实现,从而使得下位机不再需要浮点运算,涉及到的运算都是定点整数,而性能优异的FPGA(型号为EP3C40F484)即可满足定点整数的运算,运动控制器的各个功能都以模块的方式集成在FPGA中。USB3.0的传输速度很快,当有数据传输时,它会很快的将数据传给运控控制器,但由于Windows系统的弱实时性[8],数据传输很不稳定,影响运动控制器的实时性,为了解决这个问题,提出了如下两个方法:

(1)在FPGA内部添加一个双端口RAM模块作为数据缓冲区,保证粗插补数据能够被流畅地送到精插补模块。

(2)利用FPGA内部资源丰富以及生成的寄存器传输级电路具有确定的运算时间的特点,通过运算单元与门电路的复制(即增加电路面积)提升电路响应的速度,使任意的输入在确定的时间限内获得预期的输出,从而提高运动控制器的实时性。

FPGA的设计主要是三轴直线插补器的设计[9],插补器由数据缓存、插补积分器、分频器、计数器组成。本系统采用Altera公司的EP3C40F484,此型号FPGA具有逻辑单元39600个,RAM容量1134kbits,内嵌乘法器126个,锁相环4个,使用Verilog HDL语言进行程序设计,整个系统采用SOPC的设计方式,在Quartus II环境下编译、综合和下载,运用Modelsim对设计好的程序进行仿真调试,最终设计完的精插补器结构如图6。

图6 精插补器原理图

3.1 SOPC系统设计

FPGA内部功能模块的设计采用片上可编程系统设计的方式,在Quartus II环境下,通过SOPC Builder加载NIOS II内核以及自定义的IP核。NIOS软核是Altera公司推出的精简指令软核,系统中的其他子模块由NIOS处理器控制。

3.2 插补以及指令数据分配模块

插补以及指令数据分配模块主要负责将PC机发送过来的粗插补数据分配到相应的寄存器,并且对指令进行译码和选择插补方式。该模块跟Avalon总线连接,具体的信号线定义如下:

CLK:系统脉冲输入,为整个插补器提供基准脉冲。

RST:复位信号。当该信号有效时,插补器处于初始化状态,各寄存器进行复位。

CS:片选信号。该信号有效时,NIOS II软核选中插补器,使其进入待工作状态。

WR:写信号。该信号是将PC机传来的粗插补数据(X/Y/Z轴起始坐标与终止坐标)写入数据缓存。

START:插补开始信号。该信号有效时,插补器开始进行插补。

A3~A0:地址信号。处理器通过地址信号将粗插补数据分配到各轴的数据缓存器,另外,地址线的最高位A3可以选择直线插补还是圆弧插补,A3为0时,选择直线插补,A3为1时,选择圆弧插补。

Data(15:0):16位数据总线,用于传递粗插补数据。

3.3 DDA插补器模块

插补器模块是整个精插补器设计的核心,具体的工作过程为:当数据缓存器缓存有粗插补数据时,插补积分器发出申请数据的信号,缓存器接到信号后,加载数据到插补积分器,等到数据加载完毕后,插补积分器接收到START信号,积分器开始进行插补,并且分频器会给出特定频率的脉冲作为积分器的插补迭代脉冲,通过控制分频器的输出频率来改变插补器输出脉冲的频率,而此时计数器记录插补的次数,当全部完成插补时,发出插补完成的信号,通知积分器再次申请新的数据,如此循环,完成运动轨迹的插补。具体分以下4个部分:

(1)数据缓存器

本文设计的数据缓存器用来存储X/Y/Z轴的起始坐标和终止坐标,共6个16位寄存器组成,设计缓存器的目的是为了使积分器能够及时的加载到粗插补数据,使得插补的效率得到提高,并且避免因为插补数据的延迟,而使插补出现中断,甚至出现插补出错的情况。

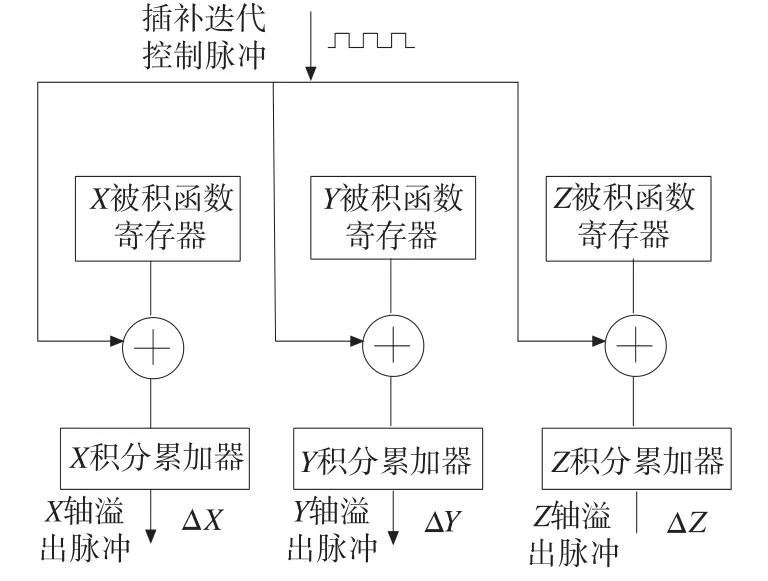

(2)插补积分器

插补积分器是直线插补模块的核心组成部分,本文设计的DDA直线插补器可以进行三轴插补,由三个数字积分器构成,每个数字积分器由积分累加器和被积函数寄存器两部分构成,插补结构原理图如图7。被积函数寄存器里存放X/Y/Z轴的终点坐标,每当来一个插补迭代脉冲,被积函数寄存器的值将会和累加器里的值累加一次,结果存于累加器中,当累积值超过216(设计的累积器为16位)时,对应的轴溢出一个增量脉冲,当经过M=216次累加后,插补器完成此次插补。使用此插补方法,在给定的时间总能够把PC发来的粗插补数据插补完,因此,就可以在粗插补阶段将需要插补的曲线段进行速度规划,形成粗插补数据,交给精插补模块,实现插补速度的控制。

图7 三轴直线插补原理图

(3)计数器

位置计数器存放要插补的脉冲次数,每插补一次,计数器的值将会减去1,直到计数器的值为0时,表示插补结束,此时计数器将会发出插补结束的信号,通知积分器进行下一次插补。

(4)分频器

粗插补数据在进入精插补之前,已经对其进行了左移规格化处理[10],因此每发出两个迭代脉冲必有一个增量脉冲输出,这样可以通过对插补迭代脉冲频率的分频控制来实现增量脉冲输出的速度,从而使DDA插补器的输出具有速度可调的功能。

设计的分频器具有对任意整数分频的功能,采用的方法是脉冲周期剔除法[11]。对于2N分频,可以方便地用模N的计数器与一个T触发器(二分频器)来简单实现50%占空比分频输出。而对于2N-1的奇数分频,为了获得50%占空比的输出,采用触发周期前移半个周期的方式,在计数器计到第N个脉冲时,只计半个周期的脉冲宽度,这样就可以得到半周期为N-0.5的时钟信号,图8为7分频(N=4)的示意图。

图8 7分频(N=4)波形示意图

具体是对150MHz系统频率,根据分频系数对其分频,为了满足步进电机的启动等特性,以两相步进电机为例,步距角1.8°,不细分的情况下200个脉冲一转,一般设置步进电机启转速设置60~200r/min,即脉冲频率200Hz~700Hz。那么设计分频器位宽为18位,那么迭代脉冲变化范围为:572Hz~150MHz,根据每两个迭代脉冲输出一个增量脉冲的关系,可以知道输出脉冲的频率变化范围为:286Hz~75MHz。

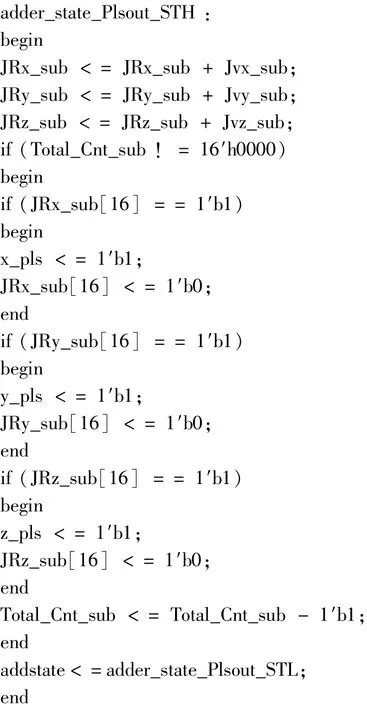

根据设计的插补模块结构,采用Verilog HDL编写的部分代码如下:

4 仿真与分析

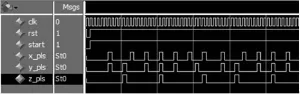

为了验证设计的正确性,对直线插补模块进行了仿真测试。

三轴直线插补,给定一段直线段,直线段的起点为(0,0,0),终点坐标为(12,11,5),对此直线段进行精插补,插补的仿真波形图如图9所示,图中clk为时钟信号;rst为复位信号,低电平有效;start为开始插补信号,高电平有效;x_pls、y_pls、z_pls为脉冲输出信号。

图9 直线插补仿真图

从仿真波形图可以看出,X轴均匀输出12个脉冲,Y轴均匀输出11个脉冲,Z轴均匀输出5个脉冲,与给定的坐标位置一致,验证了插补器设计的正确性。

5 结束语

本文研究了基于USB3.0与FPGA的多轴运动控制器,设计采用USB3.0作为PC与FPGA的通信管道,利用USB3.0超速的数据传输与全双工的工作模式,设计了数据备份式传输与双向数据通道协议,对运动控制器的各个模块采用Verilog HDL语言实现并进行仿真。由于当前市面上出售的计算机已经普遍配置了USB3.0接口,因此所设计的基于USB3.0的运动控制器应用前景广阔。仿真与实验表明,所设计的运动控制器已经能够正确实现多轴运动控制功能。今后将在此基础上针对电火花机床的控制需求改进电路,完善运动控制算法,进一步提高控制器的性能。

[1]胡细东,游有鹏,缪群华.基于USB的高速硬件精插补器设计[J].微计算机信息,2005,22(62):247-249.

[2]谢荣禧.USB3.0简介与未来发展趋势.电子与电脑,2009(7):39-44.

[3]任羿.基于预计的电子设备可靠性优化方法研究[J].电子机械工程,2004(8):19-21.

[4]黄继海.电子元器件应用手册[M].北京:人民邮电出版社,2004.

[5]张伟,王黎,郭建强,等.基于FPGA的数字积分法插补控制器设计与实现[J].现代电子技术,2011,34(22):150-153.

[6]夏长春,张建钢,吴晓光,等.精插补器在FPGA中的研究与实现[J].武汉科技学院学报,2007,20(11):16-18.

[7]刘明.基于CYUSB3014的高速实时数据采集系统[J].电子测试,2013(13):8-9.

[8]王芳,王琨琦,梅雪松.基于Windows全软件数控系统实时性的研究[J].西安工业大学学报,2009,29(3):228-233.

[9]CHEN W,Wen Z,Xu Z,et al.Implementation of 3-axis Linear Interpolation in a FPGA-based 4-axis Motion Controller.Industrial Electronics and Applications,2008.ICIEA 2008.3rd IEEEConference on.IEEE,2008:1308-1313.

[10]王细洋.机床数控技术[M].北京:国防工业出版社,2012.

[11]汪虹,李宏.基于FPGA的等占空比任意整数分频器的设计[J].仪器与仪表,2005(16):8-9.

(编辑 李秀敏)

Developm ent of M ulti-axis M otion Controller Based on USB3.0 and FPGA

GU Ding-fu,LUO Fu-yuan

(College of Mechanical and Electrical Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

The emergence of USB3.0 technologymakes the USB serial interface not only has the characteristics such as plug and play,hot swap and so on,butalso improves the rate of data transm ission.In this situation,the design ofmotion controller based on USB3.0 communication interfaceis put forward.The overall structure of themotion controller is designed and themain chip is selected in this paper,new communication protocol of data error control and bidirectional data transmission is designed using USB3.0 interface features of 5Gbps rate and full duplex mode.The controller uses FPGA as the main control chip,adopt the design method of SOPC,using Verilog HDL language to design themoduleof fine interpolation,motion controller encoder signal subdivision.Finally,the simulation validates the effectiveness and feasibility of the motion controller,which provides a reference for the development of USB3.0 products.

USB3.0;fine interpolator;motion controller;FPGA

TH165;TG659

A

1001-2265(2015)07-0064-05 DOI:10.13462/j.cnki.mmtamt.2015.07.018

2014-10-7;

2014-11-07

国家自然科学基金资助项目(51205200);江苏省自然科学基金资助项目(BK2012388);中央高校基本科研业务费资助项目(NS2012098)

顾定富(1990-),男,江苏泰州人,南京航空航天大学硕士研究生,研究方向为数控技术,(E-mail)gudingfu@163.com。