高效率并行熔丝方案的设计

2015-10-29曾祥峻

曾祥峻

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

电路设计

高效率并行熔丝方案的设计

曾祥峻

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

随着集成电路的迅速发展,熔丝在电路设计中应用普遍,测试对熔丝的要求也越来越高,需要更好的准确度和更快的效率。熔丝可以修调的参数当然也取决于该熔丝在电路中的作用,输出电压、参考电压是最为常见的修调参数,此外如基准频率、电流等也都可以通过修调做到很高的精度。简单介绍了常见的熔丝以及其作用,常用的熔丝并行测试的优势和缺陷,提出了在大于4 site测试时,进一步提高熔丝修调准确性以及修调速度的测试方法。

熔丝编程;并行测试;多site测试

1 引言

熔丝修调在传统模拟电路以及高精度要求的数字电路中,起到了越来越重要的作用,在AC-DC、DC-DC、LDO等类型的集成电路(IC)中有广泛应用。熔丝不只是修调输出电压,视乎设计而定,其主要原理是烧断电阻网络中的短路铝条以达到改变网络电阻的作用,熔丝可以修调的参数当然也取决于该电阻在电路中的作用,输出电压、参考电压是最为常见的修调参数,此外如基准频率、电流等也都可以通过修调做到很高的精度。

熔丝的过程中通常应当注意电流、电压这两项指标,用于修调的电流、电压都不能太高,否则轻则影响测试结果,严重时甚至会导致IC损毁。

电路测试产业发展至今,多管芯测试必不可少。多site测试要比单site测试效率提高2倍以上,一些不必要的串行测试的优化在多site测试的效率提升中就显得尤为重要。

2 几种熔丝的介绍

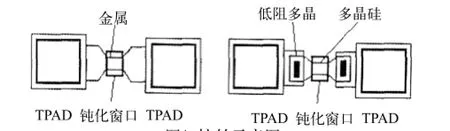

2.1传统熔丝简介

传统的熔丝方案主要有3种,以激光烧断金属熔丝,或以大电流烧断金属熔丝和多晶硅熔丝。在集成电路设计中,熔丝作为电子产品内的关键性零件,主要应用于调整其内部的电阻与电容特性,或用于射频电路之中。

普通的金属熔丝一般是由一条条金属电阻或是薄膜等其他电阻所构成。中间窄两头宽的金属导线[1],利用探针probe引接大电流(一般控制在200 mA左右)熔断,熔断之后不可恢复(由于扎针问题,可能存在烧不断的情况)。

图1 熔丝示意图

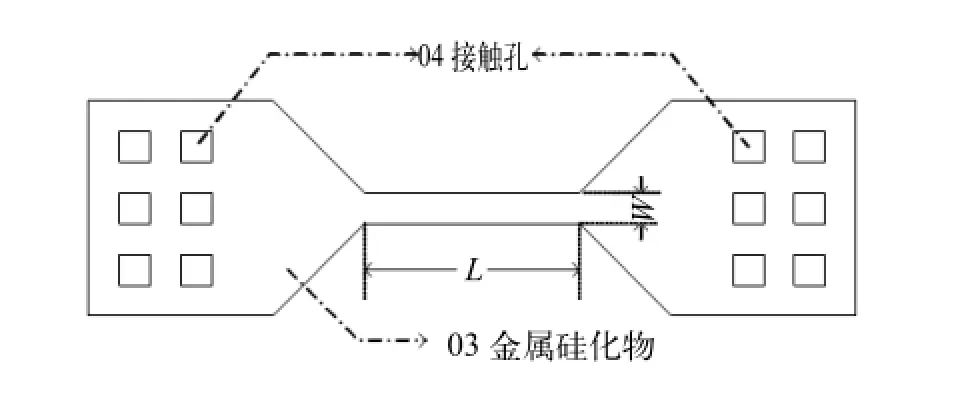

2.2硅化物熔丝

随着集成电路技术的进步,现今的熔丝工艺多采用硅化物制作。用传统的硅化物工艺形成金属硅化物,在两侧的引出区再形成接触孔,引出熔丝两端。金属硅化物的方块阻值较小,当对阳极和阴极的接触孔加高压脉冲、瞬间大电流通过金属硅化物的熔断区时,硅化物被烧断,同时瞬态大电流产生的热量也会使熔断区下面的多晶硅和杂质重新分布,使得熔丝两端之间的电阻明显增加,从而达到熔断的目的[2]。

图2 硅化物熔丝示意图

3 多site测试的熔丝分配方案

3.1普通的资源复用方式

采用资源复用的方法,给一个资源多种用途,可以有效降低多管芯测试对系统资源的需求。例如PV源既可以做被测电路的电源,而在熔丝修调时,被测电路不用上电,则可以把这部分切换为修调电源。同理,继电器控制位也可以采用复用的方式。图3是资源复用的示意图,可以看到4路PV源被分配给4颗被测管芯,通过继电器K1~K4切换到VDD或修调电源,当正常测试时,4路PV源通过继电器常闭端接入4颗被测管芯的VDD;当某一路进行修调动作时,将该路的继电器闭合,PV源接修调P提供修调电压。

图3 PV源复用原理图

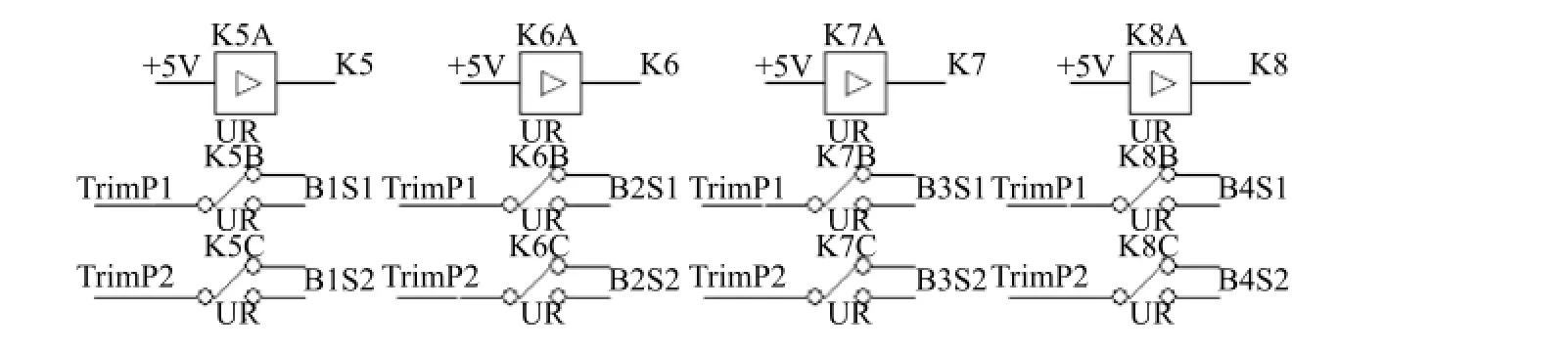

同样的,4颗被测管芯共16段熔丝,使用了4个继电器控制位进行控制,例如每个管芯的B1段熔丝,都使用K5控制。当第一颗管芯的B1需要修调时,PV源加压,K1闭合,K5闭合,管芯1的B1段熔丝被修调,而其他3颗管芯的B1段虽然也被接入各自的修调P,但此时其他3路修调P接入PV源,也就不会被烧断。当然,参数测试部分还需要一部分继电器控制位切换外围元器件,这部分不再详述。

图4 继电器控制熔丝复用

这种常用的熔丝方案,相对于单一的切继电器熔丝,只需要4路PV源和15路继电器控制位就能满足基本的参数测试和熔丝修调要求,能够方便地节省继电器控制位以及PV源的复用,但在实际熔丝过程中,必须采用串行测试来消除各个site之间熔丝的串烧现象。在熔丝段数较多,4 site以至于8 site的测试过程中,浪费的测试时间也相对较多,在竞争激烈的大环境中已经很难生存。鉴于上述缺点,优化熔丝方案,引出了串并结合的熔丝算法方案。

3.2串并结合的熔丝算法

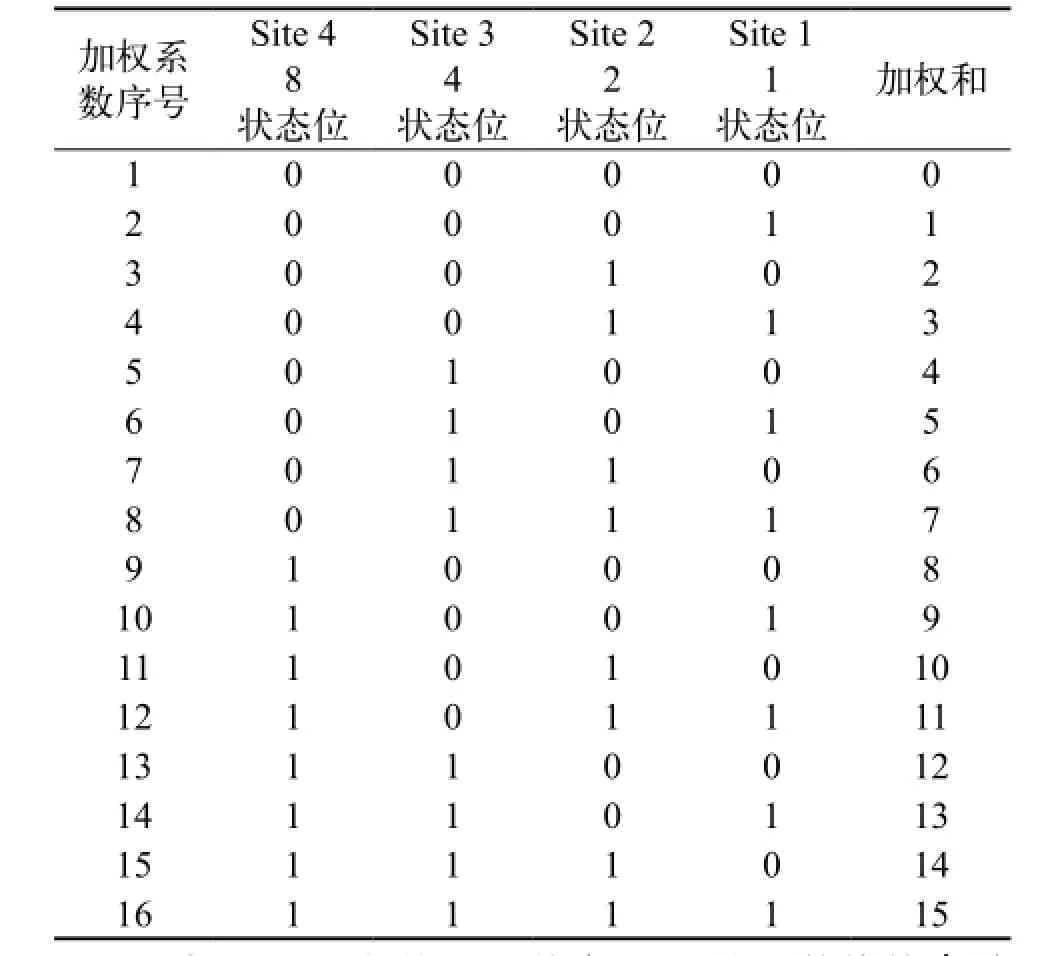

使用Fuse_x_Site_X状态标志位来表示相关site的熔丝开关状态,能够得到site1的4段熔丝位标志:Fuse_Site1、Fuse_Site2、Fuse_Site3、Fuse_Site4,同样得到其他site的标志位。完成上述工作之后,建立一张表格如表1所示。

对于设置的4个site 的fuse1,对应4个继电器控制位,变量初始值为0,熔丝熔断为1,经过加权算法处理之后得到相应的加权和,设置一个能够被ATE所识别的二维数组,用于识别继电器控制位,相对应的按照加权系数来进行继电器动作,实现继电器的第一段熔丝并行操作。

表1 同一位置熔丝段状态加权计算表

同样处理过程使用于其余Site,实现整体的串并行熔丝编程。在这种算法中,相对于普通的熔丝方案,效率提升很大,多个site的单段熔丝时间和1 site几乎没有差别,执行时间有了相当大的提升空间。

虽然熔丝效率获得很大的提升,但相对的设计和维护工作量就偏大,对于改版圆片测试需要重新计算其加权和。维护过程中,某单一熔丝接触不好也相对比较难查找,比较适用于量产产品和相对成熟的品种。

在上述串并行测试方案的基础上,利用多路通道的PV源,提出一种多site并行熔丝的测试方案,能够使得熔丝每段与程序一一对应,方便查找与分析。

3.3PV源充足的并行熔丝方案

在熔丝源充足的情况下,一路继电器能够控制6段熔丝。如图5所示,能够很明了地看出,在继电器CBIT9动作一次的情况下,能够进行2个site 的3段、一共6段熔丝的并行操作。

图5 熔丝并测最小组成单位

以此为其最小组成单位(继电器控制需要按照实际熔丝段数来设置),来设定一个二维数组,用于识别继电器控制位,以8 site熔丝方案为例,资源分配程序示例如下:

If ( 需要进行熔丝 && 1 V<初始电压<2 V)

{

B[i][0]=1;

B[i][1]=1;

B[i][2]=1;

K[3*i]=0

K[3*i+1]=1;

K[3*i+2]=2;

}

i表示从1~8 site,B[i][x]表示当前site的第x段熔丝,分别用PV源0、1、2来控制每个site的第1、2、3段熔丝,完成继电器以及PV源的分配工作。

该电路一共8 site,每个site有6段熔丝,总体分配如图6所示。

按照上述分配,把固定格式的代码整合成子程序,进一步精简程序以便于后续维护,得到的具体熔丝程序如下:

if(TrimEn==1)

{

for(i=0;i<4;i++)//此处只需要进行4次能够完成8 site的熔丝动作

{

CBIT_SRelayOn(9+2*i,10+2*i,-1);

DelaymS(5);

TRM_RelayOn(K[0+6*i],K[1+6*i],K[2+6*i],-1);

DelaymS(1);

TRM_RelayOn((K[3+6*i]+10),(K[4+6*i]+10),(K[5+6*i]+10),-1);

DelaymS(1);

}

}

TRM_RelayOn控制的是PV源给电烧熔丝,分别用继电器9、10来控制site1和site2,11、12来控制site3和site4……能够用4次完成8个site 的熔丝动作,可以提升1倍的熔丝效率。在PV源足够的情况下,完全可以用更多的继电器控制更多的site,从而实现整个熔丝的并行测试。

图 6 总体熔丝原理图

在实际生产过程中,以一种8 site的LED驱动电路为例,采用普通的熔丝复用方案,熔丝的总时间达到了1.2 s,采用串并结合的方案时间为0.4 s,已经能够和一般的双site熔丝时间相对比,而使用新的熔丝方案,熔丝时间缩短到了0.2 s附近,和单site熔丝消耗的时间相差无几,相对于最初的熔丝方案缩短了将近5倍的时间。

4 结束语

竞争日益激烈的IC行业,能够最大限度地节约测试成本至关重要。本文提出的并行测试方案,在条件允许的情况下能够极大地提升测试效率,多site测试能够媲美单site测试效率,但是也存在着相当的局限性。熔丝作为电路设计中不可或缺的一部分,各种测试方案必然存在着各自的优缺点。如何更加精准、更加高效地进行熔丝操作,需要继续进行开发和探索。

[1] Sergio Franco. Design with Operational Amplifiers and Analog Integrated Circuits[M]. McGraw-Hill Education,Inc. 2001.

[2] 李文昌,王继安,等. 修调技术在高精度集成电路中的实现[J]. 微处理机,2006.

Efficient Trimming Design of the Multi-Site Test

ZENG Xiangjun

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

With the popularization of IC design, trimming fuse is applied more generally in Circuit Design. Testing of fuse requirements are also increasing. The better accuracy and faster productivity are useful for us. The parameters of trimming depends on the role of IC. The output voltage and the reference voltage are the most common trimming parameters. In addition, such as the reference frequency, current can also be done by trimming high accuracy. This paper briefly describes common fuse as well as its role, the advantages and disadvantages of conventional parallel testing of fuses, and presents at greater than 4 site testing, to further improve the accuracy of the fuse trimming and testing methods trim speed.

fuse trimming; multi site; parallel test

TN402

A

1681-1070(2015)12-0016-04

曾祥峻(1990—),男,江苏无锡人,2013年毕业于武汉理工大学信息工程专业,助理工程师,现在中国电子科技集团第 58 研究所从事集成电路测试研发工作。

2015-7-2