一种T/R组件热场问题的研究

2015-10-29周骏,刘伟,盛重,沈亚

周 骏,刘 伟,盛 重,沈 亚

( 1. 微波毫米波单片集成和模块电路重点实验室,南京 210016;2. 空军驻江苏地区军事代表室,南京 210016;3. 南京电子器件研究所,南京 210016)

一种T/R组件热场问题的研究

周骏1,3,刘伟2,盛重3,沈亚1,3

( 1. 微波毫米波单片集成和模块电路重点实验室,南京 210016;2. 空军驻江苏地区军事代表室,南京 210016;3. 南京电子器件研究所,南京 210016)

T/R组件的热设计是有源相控阵雷达的核心技术之一。文章提出了针对高密度组件的各种散热措施,采用热仿真软件对T/R组件沟道温度进行仿真研究,并利用红外热分析仪进行测试验证,并将仿真结果与实验结果进行对比,两者结果吻合较好,满足T/R组件的使用要求。

T/R组件;热设计;高密度

1 引言

有源相控阵是近年来正在迅速发展起来的雷达新技术,是提高雷达在恶劣电磁环境下对付快速、机动及隐身目标的一项关键技术。在有源相控阵雷达的天线内部,密布着成百上千个T/R组件,每个组件都能进行信号接收与对外辐射的功能,因此每个组件都将产生热耗,成百上千个发热体聚集在一起就成为一个大的发热源,热功率较高。同时由于天线尺寸空间的限制,频率越高,空间尺寸越小,因此整个天线阵面的热功率密度也将会很大[1~2]。T/R组件作为有源相控阵雷达功能实现的重要部件之一,内部装配了数只砷化镓与硅的半导体集成电路,半导体器件对于沟道温度要求很高,结温不能超过175℃,因此对于整个T/R组件的工作温度要求同样很高,组件的热控将是相控阵设计的核心技术之一。

由于T/R组件中的功率放大器自身效率的限制(一般而言,毫米波功率放大器效率小于25%),因此,芯片工作时功放输出功率只占其消耗功率的很小一部分,大部分功率损耗都将以热能形式散发出去,长时间热能的聚集会导致芯片内部产生过高温度,一旦温度超过芯片结温,将可能导致该芯片永久失效。因此,散热技术是相控阵天线的关键技术,是系统设计不可或缺的一部分。如今的相控阵雷达中,采用了各种散热方式,主要集中在风冷和水冷。为了确保T/R组件外壳的温度达到要求,相控阵雷达设计过程中,常常使用很复杂的结构设计方案。如果能够减小T/R组件中的结壳热阻,将会有效降低散热设计的复杂性,因此T/R组件中热源芯片至外壳的传热性是研究的重点[3~5]。

2 T/R组件热设计及仿真

T/R组件体积小、集成度高、热源众多,单位平方面积上的热密度较高,在设计上必须采取一些特殊设计措施改善系统中的电热性能,热设计包括芯片级热设计以及组件级热设计两个层次。组件内最大热源是末级高功率放大器,在器件和芯片电路设计时,就要充分考虑热效应,包括增加器件栅栅间距,减小单指栅宽,减小芯片厚度等等。

组件热设计包括以下方面:(1)在安装方式上,将高热耗芯片直接安装在金属盒体上,减少芯片与金属导体之间的热阻,芯片安装可采用烧结或粘接的方式,烧结或粘接工艺关键在于控制芯片与载体间空洞率,这是减小热阻、提高功率器件可靠性最为关键的一点。(2)若高热耗芯片只能安装在LTCC基板表面而无法直接贴装到金属盒体上时,则LTCC基板需采用密集通孔的方式来提高散热效率,减少热阻。(3)版图设计上,采用热耗器件分散放置方式,防止热源过于集中。(4)提高组件外壳与整机支撑板安装面平整度,要求组件安装面的平面度小于0.1 mm/100 mm×100 mm,粗糙度小于3.2 μm,通过增加组件与散热板接触面的接触面积,以提高组件的散热效果。

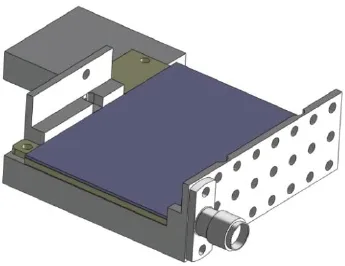

对以上设计进行仿真,通过绘图软件按照实物绘制出组件的三维模型,该T/R组件由8个收发通道组成,整体结构包括测试架、焊料、金属底板、LTCC基板、芯片等,为方便计算,同时考虑传热侧重关系,仿真时采用如下简化:首先忽略低频及控制部分热量,关注模块高热耗区域温度分布,其次认为T/R模块内芯片热耗一致,且芯片与LTCC基板间热阻一致。重点关注高热耗芯片内部沟道温度,芯片正常工作时,电流流过漏极、源极之间的沟道,因此在栅极、漏极之间的电阻最大,也就是热损耗最大的位置。建立了栅极与漏极的沟道模型,并将热损耗功率按比例平均分配到每个模型中去。模型如图1所示。将实体模型导入到热仿真软件中,通过软件的简化处理功能将复杂的结构图优化,并将软件中自带的材料属性附于每个实体。仿真时,外部环境温度设置为25℃,热台温度设置为85℃。

图1 组件测试架结构图

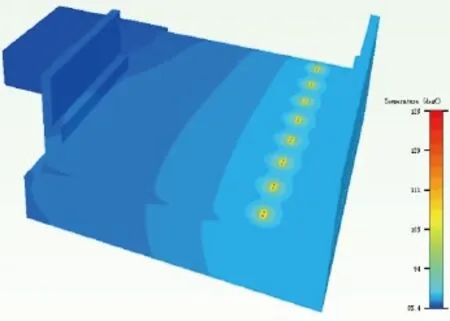

图2为该组件的温度分布云图,即组件达到热平衡状态下的温度分布情况。从图中可知,芯片管芯位置温度最高,而测试架边缘处温度最低。

图2 组件温度分布云图

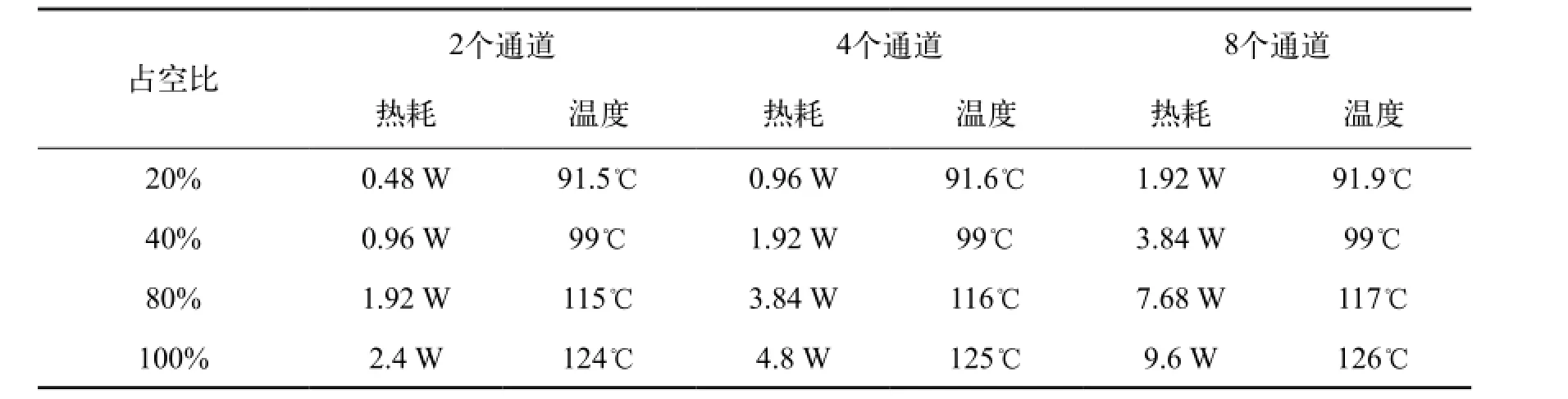

该T/R组件共有8个通道,试验分别采用2个通道、4个通道以及8个通道同时工作的方式,结合占空比20%、40%、80%和连续波的工作形式进行统计分析芯片的结温。表1表示了组件不同通道、不同占空比工作时的功放芯片结温仿真关系,其仿真的条件与表1的试验数据相互对应。从仿真的结果可知,随着组件通道工作占空比增加,组件热耗急剧增大,因此组件功放芯片结温从91.5℃急剧增大到126℃,但是组件在相同占空比的情况下,如组件每个通道均工作在40%占空比时,则每个通道的芯片结温均保持在99℃左右不变,由此可见,该多通道T/R组件散热均匀,每个通道均能将热量从芯片表面中导出,通道与通道相互间不存在干扰。

表1 组件功放芯片仿真结温

3 测试结果与分析

目前通过红外热像仪测量微电子器件的热特性越来越为行业所重视,本试验采用的显微红外热像仪为美国QFI公司生产的InfrascopeⅡ型,该热像仪由InSb面阵红外探头、显微支架、控制台、计算机、显示器、打印机几部分组成。其测温范围为70~350℃,温度灵敏度0.001℃,响应波段为2 μm~5 μm,脉冲采样频率高达200 MHz,空间分辨率达到2.5 μm。通过红外热像仪直接测量功放芯片沟道温度。

试验的测试结果如图3所示,图3(a)与图3(b)分别是红外热像仪放大5倍和25倍所测试的结果。该频段的GaAs功率放大器的栅长为深亚微米。红外热像仪的分辨率为数微米。由于红外热像仪的分辨率达不到器件结构的精细程度,测得的温度是一定范围的平均值,所以显示的温度低于最热点的实际温度。图3(a)显示的是GaAs功率放大器芯片表面管芯区域的平均温度,而图3(b)显示的是栅极与漏极之间沟道处的平均温度,即芯片可承受的温度。

图3 功放芯片温度测试图

测试时,组件同样采用与仿真实验相同的条件进行测试,分别在20%、40%、80%占空比和连续波的方式对2个通道、4个通道以及8个通道同时工作时的芯片结温进行统计分析。试验过程中,红外热像仪的台面温度设为85℃,即天线T/R组件测试架的外壳温度保持85℃,控制台对测试架起到强迫冷却的效果。

本次试验主要测试了组件T/R通道中末级功放芯片的结温,组件测试时工作电压保持5 V,工作电流随占空比变化而改变,为了提供热损耗参数,将测试的电压以及电流、输出功率进行计算,基本的计算公式为:芯片的热损耗=输入射频功率+电压×电流-输出功率。

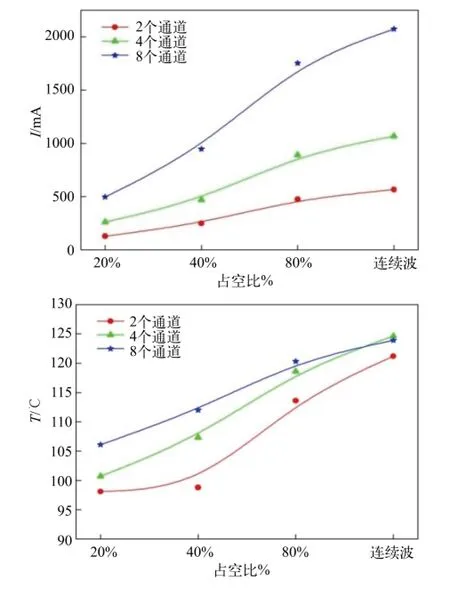

为测试方便,红外分析仪固定监测组件中间通道的功放结温,具体测试数值如表2所示。通过表2、图4可知,2个通道、4个通道及8个通道的工作电流都随着占空比的增加而增大,三者的结温也趋于线性关系逐渐增加。2个通道、4个通道、8个通道在相同占空比条件下工作时,功放芯片的结温温度相差不大。当占空比为20%,2个通道工作时,功放芯片有最低结温为91.6℃;当8个通道在连续波的状态下工作时,功放芯片的结温有120.4℃,均满足不超过结温150℃的可靠性要求,组件可以正常工作。

表2 组件功放芯片测试结温

图4 组件功放芯片工作电流及沟道温度图

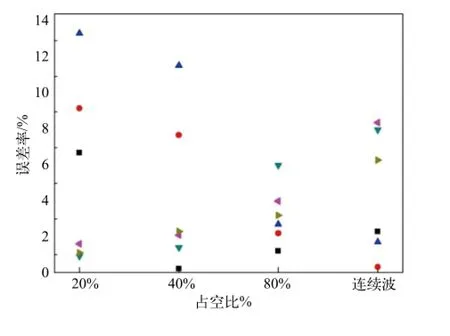

表3是组件功放芯片试验值与仿真值的对比,为了更清楚地表示误差率的大小,将表中误差率绘制成图,如图5所示。从表3及图5中可知,误差率的区间在0.2%~13.4%之间,其中误差率在1%~8%之间的分布密度较高,由此可知,该组件的热设计与实际情况符合较好。

图5 仿真与实测误差率对比图

表3 组件功放芯片试验值与仿真值的对比

4 结论

T/R组件的散热技术是有源相控阵技术的核心之一,多通道高密度T/R组件热设计尤其重要,通过热仿真软件对高密度组件进行三维热仿真,得到不同电流不同占空比情况下的沟道温度,最终实验结果表明,该种设计方法和实验较好地满足了高密度T/R组件的散热要求。

[1] 於洪标. X波段T/R组件功率放大器芯片的热设计[J]. 现代雷达,2010(4): 74-78.

[2] Li Geng, Chen Zhi-ming, Kruemmer R. A Precise Model for Simulation of Temperature Distribution in Power Modules[J]. Chinese of Journal of Semiconductors,2001,22(5): 548-553.

[3] M ital M , Pang Ying Feng, Scott E P. Evaluation of Thermal Resistance Matrix Method for an Embedded Power Electronic Module [J]. IEEE Transactions on Components and Packaging Technologies, 2008,31(2):382-387.

[4] 何倩鸿,杨平,魏巍. 二维多芯片组件的分布矩阵热设计[J]. 中国机械工程,2012,8(4): 897-899.

[5] Gilmore D G. Spacecraft thermal control handbook,Volume I:fundamental technologies[M]. California:The Aerospace Press, 2002.

Thermal Analyze and Research of High Integrated T/R Module

ZHOU Jun1,3, LIU Wei2, SHENG Zhong3, SHEN Ya1,3

(1. Science and Technology on Monolithic Integrated Circuits and Modules Laboratory, Nanjing 210016,China;2. The Air force's military representative office in Jiangsu, Nanjing 210016,China;3. Nanjing Electronic Device Institute, Nanjing 210016,China)

Thermal design of T/R module is one of the key technologies in application of active phase array radar. According to the high integrated T/R module, various methods are proposed to spread the heat in this paper. The channel temperature of PHEMT is analyzed using thermal simulator software and the temperature is tested by infrared analyze instrument. The comparison between simulated and tested results shows that the presented designs are validated to T/R modules.

T/R module; thermal design; high integrated

TN802

A

1681-1070(2015)12-0038-05

周 骏(1982—),男,安徽巢湖人,工学博士,现为中国电科集团第五十五所高级工程师,主要研究方向为微波毫米波三维立体封装及组件技术。

2015-8-12