基于训练方式的存储器时钟信号的自适应同步

2015-07-19陆辰鸿胡越黎

陆辰鸿, 胡越黎, 周 俊

(1.上海大学新型显示技术及应用集成教育部重点实验室,上海 200072; 2.上海大学机电工程与自动化学院,上海 200072)

基于训练方式的存储器时钟信号的自适应同步

陆辰鸿1,2, 胡越黎1,2, 周 俊2

(1.上海大学新型显示技术及应用集成教育部重点实验室,上海 200072; 2.上海大学机电工程与自动化学院,上海 200072)

存储器是现代电子系统的核心器件之一,常用于满足不同层次的数据交换与存储需求.然而频率提高、时钟抖动、相位漂移以及不合理的布局布线等因素,都可能导致CPU对存储器访问稳定性的下降.针对同步动态随机读写存储器(synchronous dynamic random access memory,SDRAM)接口的时钟信号提出了一种自适应同步的训练方法,即利用可控延迟链使时钟相位按照训练模式偏移到最优相位,从而保证了存储器访问的稳定性.在芯片内部硬件上提供了一个可通过CPU控制的延迟电路,用来调整SDRAM时钟信号的相位.在系统软件上设计了训练程序,并通过与延迟电路的配合来达到自适应同步的目的:当CPU访问存储器连续多次发生错误时,系统抛出异常并自动进入训练模式.该模式令CPU在SDRAM中写入测试数据并读回,比对二者是否一致.根据测试数据比对结果,按训练模式调整延迟电路的延迟时间.经过若干次迭代,得到能正确访问存储器的延迟时间范围,即“有效数据采样窗口”,取其中值即为SDRAM最优时钟相位偏移.完成训练后对系统复位,并采用新的时钟相位去访问存储器,从而保证读写的稳定性.仿真实验结果表明,本方法能迅速而准确地捕捉到有效数据采样窗口的两个端点位置,并以此计算出最佳的延迟单元数量,从而实现提高访问外部SDRAM存储器稳定性的目的.

同步动态随机读写存储器;延迟电路;训练;自适应

在嵌入式系统中,随机读写存储器占有十分重要的地位.根据其工作原理,可以分为静态随机读写存储器(static random access memory,SRAM)和动态随机读写存储器(dynamic random access memory,DRAM).由于SRAM中存储单元的静态特性,其辅助电路较少、结构简单、速度较快,既可作为片上存储器,集成于系统级芯片(system on a chip,SoC),也可用作片外存储器.同步动态随机读写存储器(synchronous dynamic random access memory, SDRAM)虽然结构相对复杂、速度较慢,但其价格远低于SRAM,且容量也更大,因此在嵌入式系统领域中被广泛使用,主要用于程序的存储、执行和数据的临时保存等.

通常,存储器数据访问错误主要有如下两种情形:判决错误和时序错误[1].前者可能是因信号线内阻造成的压降、阻抗不匹配而引起的信号畸变,因其在高速系统中采用低电压降低功耗,电压摆幅小,故受信号线内阻影响大.后者往往是因为没有满足建立与保持时间,或者采样位置错误,因此对片外高速存储器在PCB布线上有很多设计规范约束,并且需要有足够的设计冗余,以保障其在恶劣环境下也能正常工作.

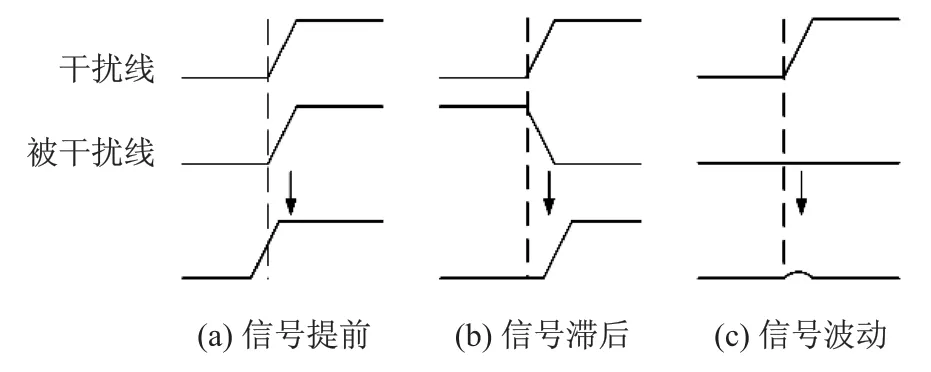

有研究表明,当SDRAM的时钟信号频率达到或超过75 MHz时,超过25.4 mm的布线长度会产生传输线效应,而线宽与内部间距的不合理会导致相邻信号线产生串扰[2].串扰是指因相邻信号线之间的耦合而引起的线上噪声.容性耦合引发耦合电流,而感性耦合引发耦合电压.图1为两个相邻信号线的串扰模型.可见,串扰现象一般分为如下3种:①干扰线和被干扰线上的信号变化相同,造成信号提前;②干扰线与被干扰线上的信号相反,造成被干扰线信号滞后;③被干扰线信号不变而干扰线信号发生变化,使得被干扰线产生波动.这是造成存储器访问不稳定的重要原因之一.

图1 相邻信号线耦合引起的串扰Fig.1 Cross-talk between the adjacent signal lines

本研究针对本课题组开发的带有片外存储器的异构多核SoC,设计了SDRAM接口时钟信号的自适应同步模块,包括位于存储控制器内的可控延迟链和CPU使用的训练程序.由于该SoC应用于汽车专用总线控制,使用环境条件复杂,对于数据的准确性要求苛刻,因此通过设计自适应同步模块可以提高数据访问的准确性与稳定性.该模块的优点是能够自主并快速地完成存储器接口时钟信号的自适应同步,不需要人为调试,从而在一定程度上提高了该SoC芯片存储器接口在各种复杂环境下的普适性.

1 提高存储器访问稳定性的相关研究

相对于CPU等高速器件性能的大幅提升,存储器的发展相对较慢.这已成为进一步提高系统整体性能的瓶颈之一,也成为了一个热门的研究方向.目前研究者们已从不同角度设法提高了存储器访问的稳定性,主要方法包括:①源同步接口动态校正(dynamic calibration for source-synchronous interface)[3-4];②延迟锁定环(delay locked loop,DLL)[5];③占空比校正(duty-cycle correction)[6-7];④自适应时钟分布网络(self-adaptive clock network)[8];⑤错误校正码(error-correction code,ECC)[9].

源同步接口的校正技术使用了动态选通掩蔽系统(dynamic strobe masking system),主要针对DDR及以上的存储器.和传统技术相比,该校正技术能够根据传入的选通信号实时动态地调整掩蔽信号的长度,并且采用了快速位抗扭斜校正引擎(fast bit-deskew calibration engine)来达到最佳的数据捕捉准确性.DLL具有快速的锁定能力,其特点是设计了延迟补偿电路,可用于抵消工艺、电压、温度(process,voltage,temperature,PVT)的影响,从而增大有效数据采样窗口.但是对于因采样点偏移较大而造成的存储器访问错误则无能为力.且DLL在时钟频率升至数GHz时,往往会产生占空比失真(duty-cycle distortion)的负面影响.因此,一种占空比校正技术便应运而生.该技术可以预防和改善占空比失真,保证了高性能存储器接口的数据捕捉正确率.自适应时钟分布网络方法是从时钟分布网络的角度来考虑.由于PVT的改变,时钟网络会随之改变,而该方法提出的控制电路能使时钟分布网络随PVT的改变而改变,形成自适应,从而改善数据捕捉能力.ECC是一种广泛用于FLASH存储器的传统方法,通过在原有数据位上增加几位校正位来进行错误检查和纠正,其中数据位每增加一倍就相应地增加一位检验位.ECC能够容许错误,并可以将错误进行纠正,使系统得以持续正常的工作,不会因错误而中断.但是这种方法的校正能力与采用的校正码类型有关.

2 存储器时钟自适应同步的机制

本研究提出的SDRAM接口时钟信号的自适应同步方法,聚焦于存储器时钟信号的训练,利用“可控延迟链”使时钟相位按照训练模式偏移到最优相位,从而减少读写错误,保证了存储器访问的稳定性.为了寻找出最优偏移相位,本研究提出了“有效数据采样窗口”的概念.在该窗口中的时钟相位能保证存储器读写的正确性,并将窗口的中值作为最佳相位.

2.1 有效数据采样窗口

在芯片的物理设计中,解决时序违例的途径之一是对时钟信号路径插入缓冲器.时钟网络分布于整个SoC内部,各条路径长度不一.在布局布线时为了让时钟树保持平衡,电子设计自动化(electronic design automation,EDA)工具会在时钟信号路径上插入适当数量的缓冲器来调节某些路径的延迟,从而保持时钟树的平衡[10].受该原理的启发,本研究在原有的存储器时钟信号的路径上增加了“可控延迟链”,使时钟信号能按照训练模式的要求产生一定的延迟.

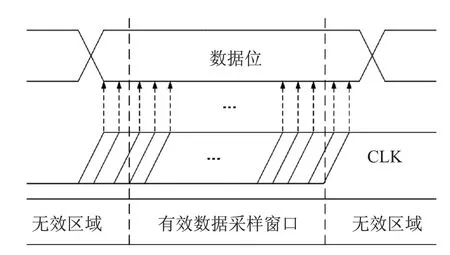

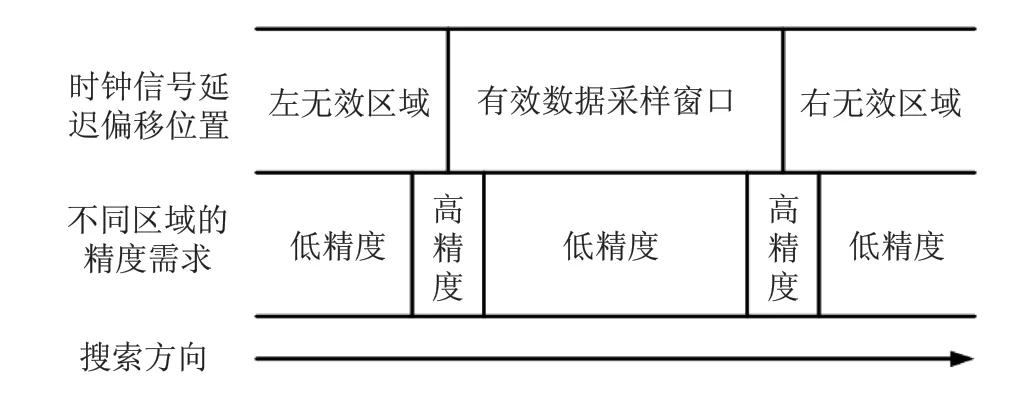

由图2可见,时钟信号经过可控延迟链后产生了延迟,使数据位的采样点也向后偏移.在数据位的起始端点与结束端点处,电平还没有完全稳定,需要一定时间去建立与保持.这里将数据位稳定区域称为“有效数据采样窗口”,而“有效数据采样窗口”的外围区域则称为“无效区域”.有效数据采样窗口两侧边缘处的数据相对于窗口中心区域不稳定,因此,最佳的采样点位于有效数据采样窗口的中间位置.通过训练,可使存储器时钟信号的延迟达到有效数据采样窗口的中间位置处,即认为完成了训练任务.

图2 有效数据采样窗口Fig.2 Valid data sampling window

2.2 自适应同步的训练模式

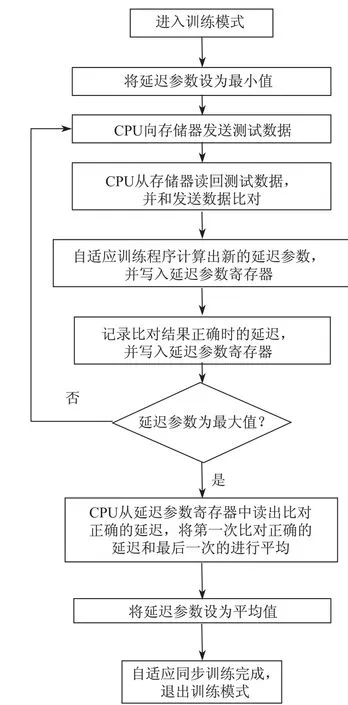

在CPU正常访问存储器的过程中,错误计数器会记录读写过程中发生错误的次数.当连续发生错误时,系统已经出现致命问题,无法再正常工作了.此时系统软件会抛出异常,调用训练模式试图改善数据读写不稳定的情况,完成训练之后对系统进行复位,重新运行.自适应同步的训练模式流程如图3所示.

图3 自适应同步的训练模式Fig.3 Training mode of self-adaptive synchronization

对时钟信号的延迟训练是一个迭代过程,每次迭代都在试图搜索有效数据采样窗口的边界.如图3所示,首先会将延迟参数寄存器的值设定为最小值,将时钟信号从零延迟位置处向最大延迟位置处逐步偏移.同时,向存储器发送测试数据并读回,比对结果是否一致.该比对结果由自适应同步训练程序分析,并计算出新的延迟参数,作为下次比对的参数.当延迟参数达到最大位置后,将第一次比对正确的延迟参数与最后一次比对正确的延迟参数进行平均,并将平均值设置为最终的延迟参数.此时退出训练模式.

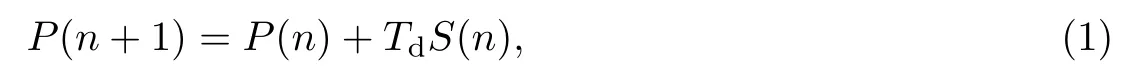

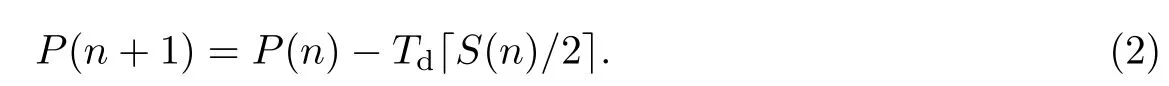

在训练模式中,时钟延迟偏移位置的计算公式如下:

式中,P表示时钟信号延迟的位置,n表示第n次训练,Td为一个基本延迟单元固有的延迟时间,S为每次迭代过程中采用的步长.S是一个变量,可根据训练模式的要求改变步长值,即时钟信号通过的不同数量的延迟单元.在不同的搜索阶段设置合理的步长值有助于迅速找到有效数据采样窗口.

由图4可知,不同的搜索区域可以采用不同的搜索精度.为了提高搜索速度,在窗口端点处使用高精度,以获得准确的窗口位置,而在其他位置可以降低精度.在低精度区域,增大步长值,以尽量快的速度“跨越”该区域,可有效地节约训练次数.在高精度区域则减小步长值,缓慢而精确地寻找端点位置.

图4 在搜索过程中,不同区域对应不同的搜索精度Fig.4 Di ff erent region with di ff erent accuracy under searching progress

本研究在低精度区域对步长值采用了二次指数增长的方法,达到向右快速“跨越”的效果(见图4).但该方法同时会导致跨过窗口端点的弊端,因此需要提高精度向左搜索端点位置.往左搜索的方法类似于二分法,即对步长值二分,若为非整数则向上取整,新的搜索位置变为

若返回的测试数据和发送的数据比对结果一致,则表明搜索位置依然在有效数据采样窗口中,可继续按二分步长的原则向左搜索;若比对结果不一致,则表明新的位置在无效区域中,应向右搜索.通过这种非线性方法可不断降低步长,提高搜索精度,从而快速准确地找到有效数据采样窗口的位置.

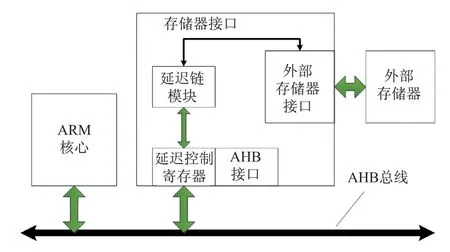

3 时钟信号可控延迟链的设计

为了实现对数据采样时钟信号训练的目的,在硬件上必须要有用于控制时钟信号延迟的模块.该模块由可控延迟链模块(delay module)和延迟控制寄存器(delay register)组成(见图5).这两个子模块都嵌入在存储器接口中,通过AHB总线把CPU和外部存储器连接起来.延迟控制寄存器的作用是由CPU来设定步长值S(n)和延迟偏移位置P(n),而可控延迟链模块则根据寄存器中的值来自动调整时钟信号经过的延迟单元的数量.

图5 嵌入在存储器接口中的延迟模块Fig.5 Delay modules embedded in memory interface

延迟链的设计方法有很多种,在专用集成电路(application speci fi c integrated circuit, ASIC)中可以简单地将反相器串联,并用多路选通器选择反相器的数量,但制造代价高昂.本研究从经济性考量,在现场可编程门阵列( fi eld-programmable gate array,FPGA)验证平台上应用了一种低成本的解决方案——基于精密时间-数字转换电路(time to digital convertor, TDC)的可控延迟链设计.TDC常应用在高精度时间测量领域,如核物理试验、雷达、激光、遥感成像等[11].采用FPGA设计的一个优势是几大厂商的产品普遍具有锁相环(phase lock loop, PLL),可用于时钟信号的倍频,即能提高时间分辨率.在此基础上进行时钟的分相,可进一步大幅提高分辨率,按照训练模式的要求更精确地调节到所需的延迟位置.

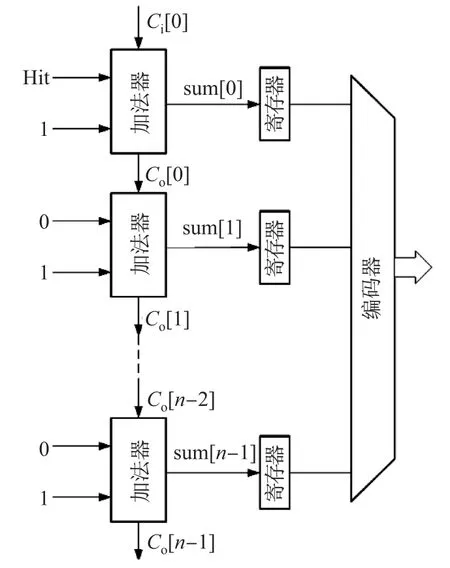

一个加法器的进位链在本研究中被用作一个基本延迟单元.若干串联的进位链组成了延迟链.在图6所示的TDC原理图中,利用FPGA中的加法器实现了进位链的串联.时钟分相的基本原理是“串行延迟、并行计数”,而不同于传统计数器的串行计数方法[12].当外部待测信号Hit输入为0时,加数的最低位输入为0,所有sum输出都为1;当外部待测信号Hit输入为1时,加数的最低位输入为1,那么加法器的最低位sum输出为0,进位输出信号Co为1.此时Co会传输到下一级加法器,sum输出为0,产生进位信号为1.依此类推,信号会在进位链上一级级传播,并可通过sum输出信号来表示.因此,需要在sum输出后接一级D触发器来锁存采集输出信号,通过译码器来分析信号传播的位置,从而计算出待测信号的延迟时间.

图6 利用加法器实现进位链串联Fig.6 Cascade carry chains connected by adders

根据该基本原理,可以设计一个基于TDC的可控延迟链结构(见图7).由控制信号控制多路选通器来选择延迟单元的数量.基本延迟单元的结构为FPGA中的进位链模块,位于一个逻辑单元(logic element,LE)中.输入的时钟信号只需要通过进位输入(LAB carry-in)和进位输出(LAB carry-out)端口.

从测量角度来看,当一个延迟单元的延迟时间与总延迟时间相差两个数量级时,认为其达到了较高的精度,因此至少要对一个时钟周期100等分,即至少需要100个基本延迟单元串联形成延迟链.

在FPGA中,通过原理图设计的方法可以直接将进位链模块连接起来,完成整个可控延迟模块的设计,也可以利用硬件描述语言、实例化全加器的方式间接调用进位链.总体而言,后者更为方便.但由于OCV(on chip variation,指在同一个芯片上,由于制造工艺等原因造成的偏差)效应的存在,无论采用何种方法,都需要在底层布局布线时将进位链按顺序安排在紧邻的逻辑单元中,以防止过长的连线延迟和严重的延迟时间非线性.

4 自适应同步机制的仿真

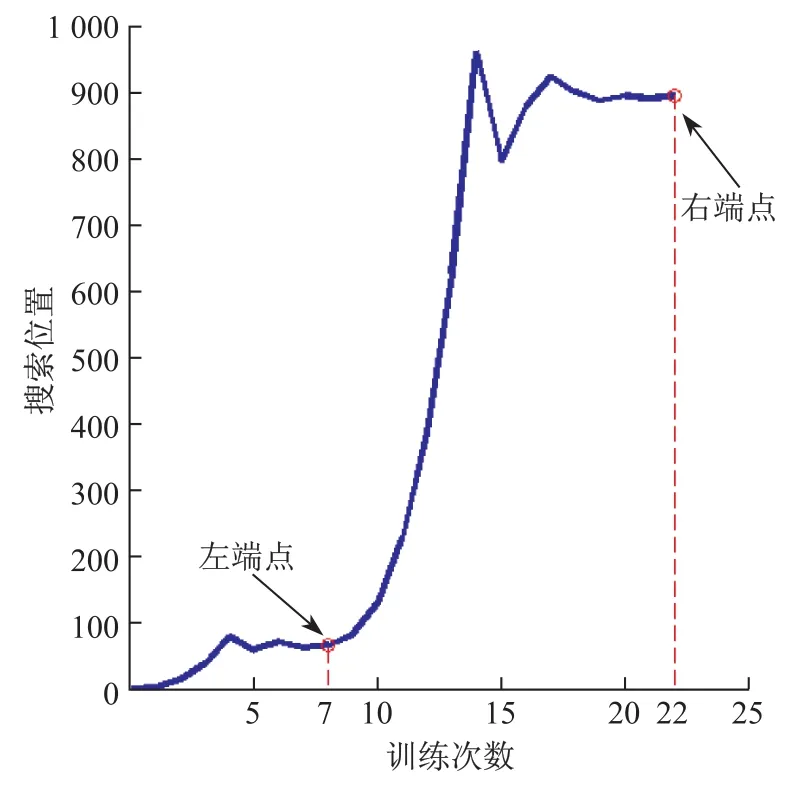

本研究将存储器接口的自适应训练模块在ALTERA Cyclone II DE1平台上进行验证.该平台具有8 MB的片外SDRAM,SDRAM时钟频率从外部50 MHz晶振经PLL倍频为100 MHz,CPU频率保持为50 MHz.训练的主要过程就是寻找有效数据采样窗口的过程.图8中横坐标代表训练次数,纵坐标代表时钟信号的搜索位置.从图中可以看出,当进行到第7次训练时,找到了有效数据采样窗口的左端点;在第22次训练时,找到了右端点.在搜索端点的过程中,还可以看到步长值逐次减小,并在端点处不断往复搜索,最终收敛于端点处.左右端点对应的延迟范围就是有效数据采样窗口.CPU此时将延迟控制寄存器的延迟位置设定为有效数据采样窗口的中点处,并从训练模式回归为正常的读写模式.此时CPU便能够稳定地访问片外SDRAM.

为了进一步了解本方法的特性,本研究将其与业界采用的方法进行了比较.NVIDIA公司是高性能图形处理单元(graphic process unit,GPU)提供商,提出了一个对高速GPU存储器接口数据采样时钟边沿训练的专利[13],采用了DLL等数模混合电路纯硬件实现.该专利文件描述的训练模式是采用固定长度的递增步长值.如果存储器的有效数据采样窗口较大,则训练次数较多,且对于不同规格的SDRAM存储器的适应性较差.因此,该方法对于集成在GPU上的存储器往往会采用经过反复测试后的最优步长值,以达到最佳的训练性能.

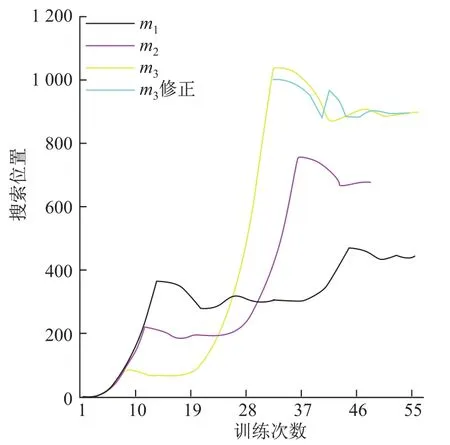

本方法中的训练环节是利用CPU实时计算出当前所需步长,对不同规格的存储器都具有很高的训练性能.在仿真环节采用了3种不同规格的SDRAM,分别记为m1,m2,m3.总的采样范围限制区间设定为0~1 000个单位时间.文献[13]中专利方法的训练次数在数值上等于有效数据采样窗口右端点的位置,而本方法的训练结果如图9所示.可以看出,这3种规格存储器的训练次数都在60次以内,远少于固定步长值的方法,其中对于存储器m3,由于在训练过程中超出了1 000个单位时间的限制,因此CPU程序对延迟位置进行了自动修正,并获得了更少的训练次数.

图8 模拟搜索有效数据采样窗口Fig.8 Simulation of searching valid data sampling window

图9 不同规格存储器的训练结果Fig.9 Training results of di ff erent memories

比较以上结果可以看出,本方法的优势在于具有很高的灵活性.用户可根据需求编写搜索程序,训练的次数远少于其他方法,在有效数据采样窗口越大的情况下能节约越多的训练次数,且硬件结构的实现比较简单.相对不足之处是延迟电路需要占用一定的芯片面积,延迟链的时间线性度需要制造工艺的配合.

5 结束语

本研究针对SDRAM接口时钟信号提供了一种自适应的训练方法,能提高CPU访问外部存储器的稳定性.在硬件上设计了一个基于TDC的可控延迟电路用以调整SDRAM时钟信号的相位.当CPU访问存储器连续多次发生错误时,系统会抛出异常,自动进入训练模式. CPU在SDRAM中写入测试数据并读回,比对二者是否一致,并以此来调整延迟电路.按照训练模式的要求不断调整延迟时间,最终得到能正确访问存储器的有效数据采样窗口,并取其中值为SDRAM最优时钟相位偏移.退出训练模式后,对系统复位,采用新的相位读写数据,能保证CPU访问存储器的稳定性.仿真实验结果表明,本方法能迅速而准确地捕捉到有效数据采样窗口的两个端点位置,并以此计算出最佳的延迟单元数量,从而实现提高访问外部SDRAM存储器稳定性的目的.

[1]KYOMIN S.A 1.2 V 30 nm 3.2 Gb/s/pin 4 Gb DDR4 SDRAM with dual-error detection and PVT-tolerant data-fetch scheme[C]//IEEE International Solid-State Circuits Conference Digest of Technical Papers.2012:38-40.

[2]LI M P.Jitter,noise,and signal integrity at high-speed[M].New Jersey:Prentice Hall,2007.

[3]PLESSAS F.Advanced calibration techniques for high-speed source-synchronous interfaces[J]. IET Computers and Digital Techniques,2011,5(5):366-374.

[4]VAN HUBEN G A.Server-class DDR3 SDRAM memory bu ff er chip[J].IBM Journal of Research and Development,2012,56(1):32-42.

[5]BO Y,LI T W,HAN X C,et al.A fast-lock digital delay-locked loop controller[C]//ASIC.2009: 809-812.

[6]LIN F.All digital duty-cycle correction circuit design and its applications in high-performance DRAM[C]//IEEE Workshop on Microelectronics and Electron Devices.2011:1-4.

[7]MIN Y J.A 0.31–1 GHz fast-corrected duty-cycle corrector with successive approximation register for DDR DRAM applications[J].Very Large Scale Integration Systems,2012,20(8):1524-1528.

[8]LIN F,KEETH B.A self-adaptive and PVT insensitive clock distribution network design for high-speed memory interfaces[C]//IEEE Workshop on Microelectronics and Electron Devices. 2009:1-4.

[9]CHEN T H,HSIAO Y Y,HSING Y T,et al.An adaptive-rate error correction scheme for NAND lf ash memory[C]//VLSI Test Symposium.2009:53-58.

[10]XIE M P.Clock data recovery based on delay chain for medium data rate transmission[C]//Real Time Conference.2009:137-140.

[11]WANG J H,LIU S B.The 10-ps multitime measurements averaging TDC implemented in an FPGA[J].Nuclear Science,2011,58(4):312-330.

[12]叶超,冯莉,欧阳艳晶.基于FPGA的精密时间间隔测量仪设计[J].信息与电子工程,2009,7(2): 159-163.

[13]KU T S,JOSE S.Data sampling clock edge placement training for high speed GPU-memory interface:US,7567104 B2[P].2009-07-28.

本文彩色版可登陆本刊网站查询:http://www.journal.shu.edu.cn

Self-adaptive synchronization of memory interface based on training

LU Chen-hong1,2,HU Yue-li1,2,ZHOU Jun2

(1.Key Laboratory of Advanced Display and System Applications,Shanghai University, Shanghai 200072,China; 2.School of Mechatronic Engineering and Automation,Shanghai University, Shanghai 200072,China)

Memory is a core device in system on a chip(SoC)and other electronic systems for data exchange and storage at di ff erent levels.However,memory access errors may occur due to factors such as raise of frequency,jitter,phase drift,unreasonable placement and routing.An adaptive synchronize method focusing on the training of clock signal is designed for synchronous dynamic random access memory(SDRAM)interface to enhance stability of memory access.A CPU-controlled delay circuit is used to shift the phase of SDRAM clock signal.A training program is designed to cooperate with the delay module hardware for memory interface tuning.In the training mode,CPU writes test data to the memory and reads them back,judging whether they are matching or not.Training program tunes the delay circuit according to the test results.A valid data sampling window is obtained rapidly and accurately after several iterations.Using the method,the middle of the window is calculated,which is the optimal phase drift for SDRAM clock signal and can improve stability of memory access.

synchronous dynamic random access memory(SDRAM);delay circuit;training;adaptive

TP 271+.5

A

1007-2861(2015)04-0393-09

10.3969/j.issn.1007-2861.2014.01.006

2013-11-27

国家自然科学基金资助项目(61376028);上海市科委基金资助项目(13111104600)

胡越黎(1959—),男,教授,博士生导师,博士,研究方向为机器视觉、汽车电子、动力电池管理、IC设计. E-mail:huyueli@shu.edu.cn