基于FPGA的AES加密算法功耗研究

2015-07-18郭正泽赵红东姚奕洋陈洁萌冯嘉鹏

郭正泽,赵红东,姚奕洋,陈洁萌,冯嘉鹏

(河北工业大学电子信息工程学院,天津 300130)

基于FPGA的AES加密算法功耗研究

郭正泽,赵红东,姚奕洋,陈洁萌,冯嘉鹏

(河北工业大学电子信息工程学院,天津 300130)

AES(Advanced Encryption Standard)是美国国家标准技术研究所NIST旨在取代DES的21世纪的加密标准.详细介绍了AES加密的算法原理,实现了基于FPGA平台AES加密算法的设计与功能仿真.从静态和动态两方面分析了功耗的产生原因,研究了基于FPGA平台的AES加密算法降低功耗的问题,以及随着时钟频率的增加,系统功耗的变化趋势.算法模块占用逻辑资源少,加密效率高,并在保证安全性,和满足应用需求的前提下,实现了平衡数据处理速度和系统功耗这两个重要参数的目的.

高级加密标准(AES);FPGA;低功耗;时钟频率;吞吐量;安全性

AES加密算法安全性好、加密效率高、设计灵活、应用范围广,可适用多种安全需求领域.由于硬件实现AES算法相对于软件来说稳定,速度快,不易受到攻击.所以用硬件实现AES加密算法成为研究热点[1-4].文献[5]使用流水线处理的方法来提高硬件速度,可得到1.94 Gbps的加密速率.但这样只考虑处理速度,忽略功耗方面的问题,成本较大;又通过对AES算法S盒和列混合变换操作的改进[6],很大程度的提高了算法速率.但这些设计占用逻辑资源过高,因此功耗大,成本也高;而面向实际,考虑在满足速度需求的情况下以最节约硬件资源的方式实现AES算法,可以达到降低功耗的目的[7].因此,研究满足一定速度需求的低功耗、低成本硬件加密芯片越来越受到重视[8].

1 AES加密算法总体描述

AES加密算法的实现框图如图1所示.在此设计中,AES算法的输入为128位数据,在操作中都是以字节为基础.按照标准,当输入为128位时,中间变量由1字节构成.中间变量State用4×4字节矩阵表示[9].

图1 AES加密算法实现框图Fig.1 AES encryption algorithm block diagram

字节替代变换(SubByte):字节替代变换是一个非线性的字节替代,使用一个S盒对State的每个字节进行独立的替换.该S盒是可逆的,由两个变换复合而成[10].

S盒按构造方式如下:

每个中间变量是一个字节(8位),将其初始化为十六进制数据.

把S盒中的每个字节映射为在有限域GF 28中的乘法逆运算,其中,元素{00}映射到它自身.

把S盒中的所有字节转换为二进制数据表示b7,b6,b5,b4,b3,b2,b1,b0,以矩阵的形式,S盒的仿射变换可以表示为

其中b'7,b'6,b'5,b'4,b'3,b'2,b'1,b'0是进行仿射变换后的字节二进制数据表示.

行位移变换(ShiftRow):中间变量的第1行维持原顺序,第2行循环向左移动一个字节,以此类推,变换如

列混合变换(M ixColumns):对一个状态的每一列去乘一个矩阵,每个列都被看成中GF 28的一个四项多项式,其乘法是在有限域GF 28内进行的,即与固定多项式aχ=03χ3+01χ2+01χ+02模χ4+1乘运算.则列混合变换后的值为S'cχ=Scχaχ.

其矩阵乘法表示如

轮密钥加变换(AddRouondKey):用比特异或将一个轮密钥作用在状态上.每一个轮密钥由通过密钥扩展算法得到的Nb个字组成,将这Nb个字异或到状态的列上,即

密钥扩展算法:密钥扩展算法中包含Rotword和Subword两个函数和.Rotword B0,B1,B2,B3类似于行位移操作,对输入的字节进行左移操作,即Rotword B0,B1,B2,B3=B1,B2,B3,B0.SubWord B0,B1,B2,B3对输入的字节使用S盒的替换操作SubBytes.

扩展密钥的前Nk个字就是外部密钥,后面的字W i是由前面的字W i 1和前第Nk个字W i Nk Subword Rotword W i 1 Rcon i/Nk异或得到.但是若i为Nk的倍数,W i=W i Nk,Rcon i=RC i =RC,'00','00','00'的所有可能值见表1.

表1 数组RC[i]的值Tab.1 The valueof thearray RC[i]

2 功耗的组成

2.1 静态功耗

静态功耗一直存在与芯片所处工作、静止状态无关.静态功耗主要是由漏电流引起.随着半导体工艺不断先进,晶体管尺寸不断减小,沟道长度逐渐减小,使得沟道阻抗变小,漏电流变大.此外静态功耗不仅与工艺有关,与温度也有很大的关系.

2.2 动态功耗

电容充放电是引起动态功耗的主要原因.很大程度上取决于电压、工作频率、负载.增大节点电容,提高工作频率,内核电压变大,都会引起动态功耗的升高.FPGA中动态功耗主要表现为内部逻辑、存储器、时钟、I/O端口的功耗[11].由于在设计中,静态功耗随着芯片的确定而确定,并且静态功耗在系统的总功耗中占有的比例比较低,所以降低动态功耗是关键.

3 加密算法的功能仿真

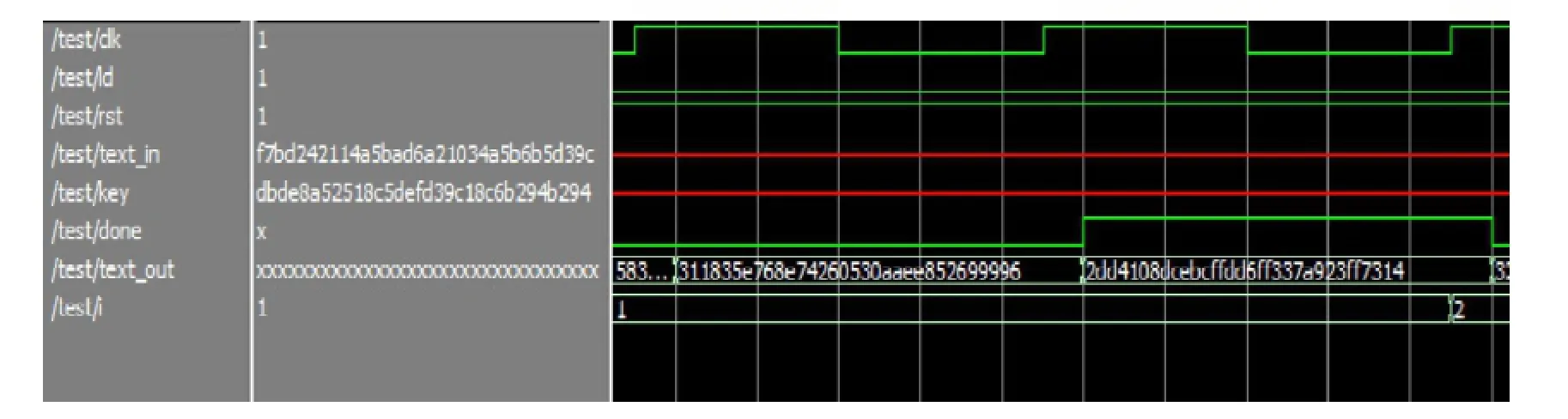

对此加密系统进行功能仿真,并将仿真所得到的结果和所给出的测试数据相比较.图2给出了该系统在加密过程中的功能仿真结果.仿真时使用的测试数据如下(十六进制表示).

明文:f7bd242114a5bad6a21034a5b6b5d39c;

密钥:dbde8a52518c5defd39c18c6B294b 294;

密文:2dd4108dcebcffdd6ff337a923ff 7314;

对比所给的测试数据和仿真结果可知,此系统仿真所得到的密文输出结果与测试数据加密结果一致,能准确的执行AES加密算法.该示例所使用的时钟频率为50MHz,在下边的步骤中,将分别设置不同的时钟频率,来进行系统的功耗分析.

4 实验结果分析

本设计选择了Altera公司的Stratix系列的EP1S10F780C6型号芯片,其在设计中的静态功耗为187.50 mW.器件型号选定以后,静态功耗不会轻易的改变.

引起FPGA动态功耗的因素诸多,文章主要研究了系统时钟造成的动态功耗.利用Quartus II的PowerPlay功耗分析工具,依据VCD文件可对系统的功耗进行分析.在设置时,选择run gate-levelsimulationautomatically after compilation选项,同时在nativelink settings选项下指定testbench.在对本设计进行综合布局布线之后自动进行门级仿真,同时执行生成VCD的tcl文件,这样就会生成门级的VCD文件,然后用PowerPlay工具加载VCD文件进行功耗的分析.

图2 功能仿真结果Fig.2 The resultof function simulation

在设计testbench文件时,可设定时钟每隔N个时间单位,高低电平翻转一次.时间单位大小可由`timescale指定,2N倍的时间单位大小即为时钟周期.因此,可通过设定数值N和时间单位大小来设定不同的时钟周期,得到不同的时钟频率.例如文章实验中通过` timescale来指定时间单位为1 ns,设定N为20,即可得到25MHz的时钟频率.可通过类似的方法得到其他需要的时钟频率.通过设定不同的时钟频率,来进行功耗分析得到的数据如图3所示.

从图可以看出,总功耗随时钟频率基本成线性变换.可以通过提高或者降低时钟的频率来增大、减小系统功耗.但时钟频率的变化,不仅会影响到系统的功耗,还会影响系统速度这个重要参数.在AES算法中,数据吞吐量是速度的重要指标.所以,设计者不能一味的为了降低功耗而降低时钟频率.需要在功耗和吞吐量之间取得一个最佳平衡点,即合适的时钟频率.使得系统在既满足吞吐量的同时,又不会有太大的功耗.如图4所示,是吞吐量随时钟频率的变化.并将功耗和吞吐量进行了对比.

图3 时钟、功耗关系图Fig.3 The relational diagram of the clock and power consumption

由于器件型号选定以后静态功耗基本固定,时钟频率在小于40MHz时,由于此时动态功耗还比较小,静态功耗占有的比例比较大.所以产生相应的吞吐量,所消耗的总功耗也就相对比较大.当时钟频率大于40MHz时,随着时钟频率的增大,动态功耗也会随着增加,静态功耗所占比例越来越小且小于30%.

总功耗随时钟频率基本成线性变换,然而当时钟频率大于100 MHz时,图3中的功耗线的斜率有较明显的增大.由此我们可以得出:当时钟频率大于100MHz时,要产生相应的吞吐量,就需要消耗较多的功耗.所以如果系统设计没有要求较高的吞吐量,应该把时钟频率控制在100MHz以下.

图4 功耗和吞吐量随时钟频率变化趋势Fig.4 The tendency of the power consumption and clock w ith the change of clock frequency

针对AES硬件实现时,不仅要研究信息处理速度,更重要的应该是注重实际应用需求.很多实际应用的数据流量都在400 Mb/s以下,所以不应追求过高的吞吐量而产生过高的功耗.应该在满足应用需求(速度和安全性)的情况下降低系统功耗.例如在本设计中,如果没有对系统速度提出过高要求,可以根据需要,在50~100MHz时钟频率之间选择合适的时钟,以满足速度和功耗的平衡.

5 结论

文章着重研究了在AES加密系统中,保证安全性和满足需求的前提下,平衡功耗和速率这两个重要参数.针对AES硬件实现主要有两个方向,一是面向信息处理速度,另一个是面向实际应用需求.为了平衡速度和功耗,本系统时钟频率应该控制在40~100MHz之间,再根据系统要求的具体速度,来确定具体的时钟频率.由图3可知,当时钟频率控制在此频段时,仍可得到600~1 300M b/s的加密速率,满足目前网络上绝大部分用户需求的千兆和百兆以太网.可见,用本文提供的方法来确定时钟频率,在满足信息处理速度的同时,减小了不必要的功耗.在满足实际应用需求的同时,实现了速度和功耗两个参数的平衡.

[1]Li Tao,W ang Yong,Zhou jian,etal.An optimal FPGA implementationofGPON-AES[J].Telecommunications Net-work Technology,2010,10(10):53-57.

[2]Daemen J,Rijmen V.The Design of Rijindael:AES the advanced encryption standard[M].Berlin:Springer-Verlag,2002:31-148.

[3]Biham E,Biryukov A,Sham ir A.Cryptanalysis of skip jack reduced to 31 rounds using impossible differentials[M].Berlin:Springer-Verlag,1997:149-165.

[4]Phan RCW.Impossible differentialcryptanalysisof 7-round Advanced Encryption Standard(AES)[J].Information Processing Letters,2004,91(1):33-38.

[5]Elbirt A j,YipW,Chetw ynd B,etal.An FPGA based performance evaluation of the AESblock cipher candidatealgorithm finalists[J].IEEE Transof VLSISystems,2011,9(4):554-557.

[6]阮晔,张学杰.一种基于FPGA的AES算法的低功耗实现[J].云南大学学报:自然科学版,2007,29(S2):254-258.

[7]张金辉,郭晓彪,符鑫.AES加密算法分析及其在信息安全中的应用[J].信息网络安全,2011(5):31-33.

[8]Huang Qian shan,JiXiao yong.Design of AESencryptionalgorithm basedon low-cost FPGA[J].Communications Technology,2010,43(9):156-158.

[9]杨军,余江,赵征鹏.基于FPGA密码技术的设计与应用[M].北京:电子工业出版社,2012:144-173.

[10]Han Shao nan,LiXiao jiang.Efficientmethodsto implementS-BOX and INVS-BOXin AESalgorith[J].Microelectronics,2010,40(1):103-107.

[11]韩雪,郭文成.FPGA的功耗概念与低功耗设计研究[J].单片机与嵌入式系统应用,2010(4):25-28.

[责任编辑 代俊秋]

The research of the power consumption of the AES encryption algorithm based on FPGA

GUO Zheng-ze,ZHAO Hong-dong,YAO Yi-yang,CHEN Jie-meng,FENG Jia-peng

(School of Electronic and Information Engineering,HebeiUversity of Technology,Tianjin 300130,China)

AES(Advanced Encryption Standard)is an Encryption Standard proposed by American national standards instituteof technology NIST to replace DESEncryption Standard in the21stcentury.Theprincipleof AESencryption algorithm was introduced in detail;the design and function simulation of the AESencryption algorithm based on FPGA platform werecomp leted.Reducing power consum ption of the AESencryption algorithm based on FPGA w asdiscussed. The causes of the power consumption were analysed from static and dynam ic aspects.W ith the increase of clock frequency,the tendency of the system pow er consum ption w as studied,too.A lgorithm module occupies less logical resources,yethashigh efficiency in encryption.Thepurposeofbalancing the tw o im portantparameters-data processing speed and power consum ption has been reached upon the preconditions of guaranteeing thesecurity andmeeting the demand ofmany applications.

advanced encryption standard(AES);FPGA;low power consumption;clock frequency;throughput;security

TP309.7

A

1007-2373(2015)01-0018-05

10.14081/j.cnki.hgdxb.2015.01.004

2014-06-20

河北省自然科学基金(F2013202256)

郭正泽(1989-),男(汉族),硕士生.通讯作者:赵红东(1968-),男(汉族),教授.