Flash存储器下的显示数据差错控制

2015-07-05周文辉邓春健官祥飞

周文辉,邓春健,官祥飞

Flash存储器下的显示数据差错控制

周文辉1,2,邓春健1,3*,官祥飞3

(1.电子科技大学中山学院,广东中山528402; 2.电子科技大学自动化工程学院,四川成都610054; 3.电子科技大学计算机科学与工程学院,四川成都611731)

Flash存储器常作为嵌入式大屏幕显示系统的显示信息存储设备,然而Flash存储器在使用时会存在诸如位反转等读写操作出错的问题,给系统的正常显示控制带来隐患。对Flash存储器存储误码率进行了分析,并结合显示数据存取的特点,设计了差错控制编码来实现Flash存储器下的显示数据差错控制。结合嵌入式控制系统的特点,设计了一种基于(31,26)循环汉明码编译码电路,在实际应用中可以将误码率降低至少1个数量级以上,提升了数据存储器抗突发干扰和随机干扰的能力,同时具有较低的设计复杂度。

嵌入式系统;误码率;Flash存储器

Key words:embedded system;bit error rate;flash memory

1 引言

LED图文显示屏是LED大屏幕显示器中最常见的一类应用,这类显示器的特点是:显示分辨率低,显示内容以显示宣传信息和即时通知为主,系统控制方案常常采用嵌入式脱机控制的方式。显示屏的显示数据一般会采用专门的只读存储器来存放,而Flash存储器因为其大容量、低成本、低功耗、高速读写等诸多优势成为了显示信息存储的最佳方案[1]。

NOR Flash和NAND Flash是当前两种主要的非易失性闪存。在显示数据较少的应用,可以采用普通的NOR Flash,而对于超大显示信息存储的高数据存储密度的应用,NAND Flash则是理想的解决方案。由于当前工艺并不能保证在Flash存储器生命周期中都保持可靠的性能,例如在对Flash存储器进行读写操作时,存储器中个别比特位可能会发生错误,例如从1变成0或从0变成1的位反转等现象,而相对NOR Flash,NAND Flash的位反转现象会更加容易发生[2],而随着Flash使用次数的增加,错误出现的机率呈上升趋势。

存储器中的数据一般存在图像文字信息和控制信息两种数据类型。由于存储器中显示图像数据一个位对应着一个像素点,显示数据一个位的变化会直接导致显示器上很明显的“花点”现象,会给接受信息的人造成非常不好的视觉反应。在单个像素点较大的显示屏的应用,这一问题会更突出。如果存储器中存储的是显示控制数据,则一个位的变化将会对控制指令造成较大的影响,其控制结果变得不可预测。现有方案在显示数据存储后将不做校验,如果Flash存储器发生了错误,远端的控制中心既不能及时察觉,也难于纠正这一问题。而传统方法常常是更换硬件来解决,这给设备后续维护带来了许多不便[3-4]。

解决或改善LED大屏幕显示器显示数据在Flash存储器下的错误问题对提高显示系统整机使用寿命、节省维护费用具有较大的意义,目前该方面的应用研究并不多。本文针对LED大屏幕显示器控制系统特点,将显示数据差错控制引入到Flash存储器下显示数据的存储中来。实验结果表明,本文提出的方法能够有效解决因为Flash存储器位反转等问题带来的显示出错问题。

2 显示数据差错控制分析

2.1显示数据存取误码率分析

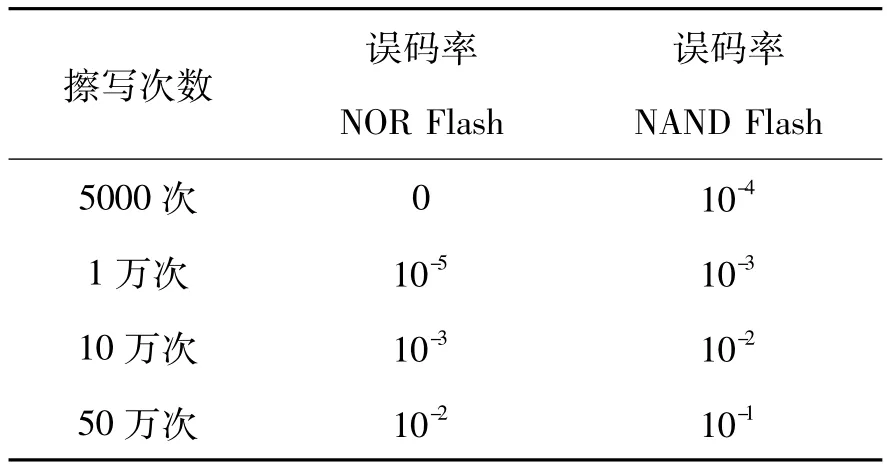

针对Flash存储器位反转等数据存储出错的问题,我们曾经通过第三方获得较为粗略的实验数据,模拟实际应用环境并保证操作时序和电路稳定的前提下,针对两种不同类型、不同品牌的Flash存储器误码率做了一个粗略的统计,方法是针对一个固定的块进行反复的读写操作,如表1所示,误码率在相应的数量级上下波动。

表1说明Flash擦写次数越多,数据误码率越高。实验结果也表明,Flash出错的时候一般不会造成整个块或是页不能读取,或是全部出错,而是其中的一个或几个比特位出错[5]。

表1 误码率统计Tab.1Statistics of error rate

2.2差错控制编码的选择

差错控制编码可以在一定程度上解决或改善Flash存储器的显示数据出错问题。选择和构造差错控制编码需要根据实际工程中数据结构特点和控制系统硬件结构特点来进行。

首先,从大屏幕显示控制系统结构来看,LED大屏幕显示器控制系统一般采用FPGA+MCU模式,MCU用来对系统管理和效果变换等处理,FPGA作为协处理器实现扫描时序及外部设备地址分配等工作[1,6]。差错控制译码过程只能放置在显示数据读取后和扫描时序形成过程中,而显示数据从存储器读取后一般通过串行移位方式输出,较低处理能力的MCU往往无法满足译码的同时与高速的扫描时序相匹配。

差错控制编码的选择既要满足纠错要求,又要与系统较好地结合。对比其他类型编码,由于循环码自身串行循环移位的特点,纠错与扫描信息的生成可以完全同步,可以方便地融入到扫描电路中,而不影响系统原有电路结构。

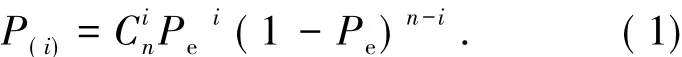

另外,从概率学来看,显示信息的差错可能出现在长为n的码字任意1位或任意多位,错误样式有2n-1种,设Pe为发生1位错误的概率,在这些可能的错误中,发生i位错误的概率为:

通过式(1)可见出现一位错误的概率最高,出现2位或2位以上错误的概率远小于1位的出错概率,纠正了1位错误即可将误码率降到较低水平。因而仅需选择能纠正1位错误的差错控制编码,并选择合适的码长即可满足应用要求。

对于任意整数m≥3,当循环码(n,k)使式(2)汉明限式等号成立时即为循环汉明码,可以纠正1位错误,由于监督位相对少,往往比BCH码、RS码具有更高的编码效率[6]:

式中n表示码长,k表示信息位长,当m=5时即(31,26)码。由式(1)可知,通过(31,26)码纠错后误码率低于10-3,降低至少1个数量级以上。另外,(31,26)编码后监督位仅5位,编码效率能达到83.8%。一般的,在大屏幕显示器的使用周期内已经能够满足数据存储抗突发干扰和随机干扰的需求[6-8]。

3 差错控制电路设计

3.1编码电路的设计

首先设计编码电路。在编码时,首先获得(31,26)系统循环码的本原多项式g(x),用来作为生成编码的生成多项式。

然后待编码信息m(x)与生成多项式相乘后即可获得编码信息c(x)。

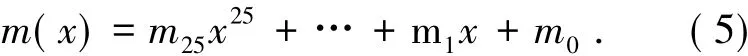

在编码前所有待编码信息位都准备完毕,26个信息位m=(m25m24,……,m0),用式(5)的多项式形式来表示。

设经过编码运算后获得31位码字c=(c30,c29,……,c1,c0),多项式形式为:

图1 编码电路Fig.1Coding circuit

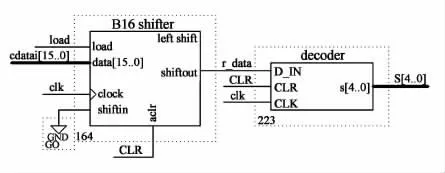

具体编码实现电路如图1所示,电路由16位并串转换电路B16_shifter和除法电路cyc_31_26_ coder构成,除法电路内部实现见图2。假设Flash存储器是按16位存储方式存储,则26位信息位需要装载2次。图1中,编码电路工作前,首先通过CLR将并串转换电路B16_shifter和除法电路cyc_31_26_coder清0。然后令装载信号load有效(高电平),将16位数datai[15..0]装载进入B16_ shifter。随着load变成低电平,数据在移位时钟clk的作用下左移,高位首先通过shiftout移入除法电路cyc_31_26_coder。在完成第一次数据装载后,经过16个时钟,产生下一个装载信号。接着,再经过10个clk时钟周期后编码完成,即在第27个clk时钟,编码结果出现在c[4..0]上。3.2译码电路的设计

图2 除法电路Fig.2Division circuit

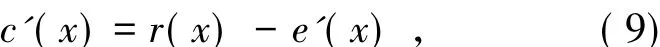

编码后存储在Flash中的数据信息用多项式c(x)来表示,从Flash中实际读取的信息用多项式r(x)来表示。如果数据在存储过程中发生错误,则错误图样多项式用e(x)来表示。如式(7),r(x)相当于在信息c(x)叠加了错误e(x)。

若(31,26)系统循环码的错误图样多项式e(x)为:

译码器的任务就是从读取信息r(x)中找到出错误图样多项式e'(x)来估计信息码多项式c'(x)

进而得到信息组m'(x)。循环码的错误图样一般是通过伴随多项式s(x)来获得,循环码的伴随式及错误图样与接收码关系为

具体译码实现电路如图3所示,译码电路主要包括数据装载及伴随式计算电路、伴随式计算完成指示电路、纠错电路3部分。编码数据共31位,在16位存储器中需要占用2个存储单元。当load信号有效时,存储在Flash中的编码数据装载进入16位并串转换电路B16_shifter,在移位时钟的作用下,并串转换结果raw_data移入伴随式计算电路,在第16个时钟时产生下一个装载信号,完成伴随式计算共需要31个时钟。

图3 数据装载及伴随式计算电路Fig.3Dataloadingandsyndromepolynomial computing circuit

与此同时raw_data移入纠错电路,对从Flash读取数据进行纠错处理。

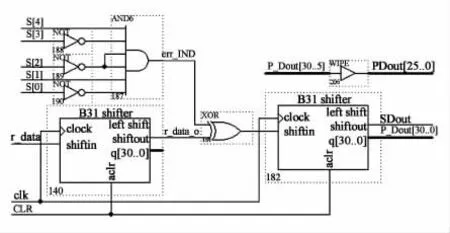

由于伴随式需要在伴随式计算电路中移位31次才能获得,因而raw_data移入31位移位寄存器B31_shifter进行暂存,以此与伴随式计算电路运算同步。

在实现对错误位的纠正时,译码电路被设计成纠正最高阶位x30上的错误,错误图样x30的伴随式为:

错误图样检测电路由与门构成,如图4所示。当伴随式计算完毕后,且当伴随式计算电路输出状态为10010时,与门输出err_IND为1,此时经过移位寄存器输出raw_data_o错误位通过异或门纠正后送入下一级移位寄存器B31_shifter。图中SDout为纠错后的串行输出,P_Dout[30..0]为纠错后的并行输出结果。

此时数据获得了纠正,低5位监督位可以丢弃,图中PDout[25..0]即为获得纠错后的信息数据位。

图4 纠错电路Fig.4Experiment of scale establishment

电路采用伴随式计算及纠错完成指示电路来指示译码电路的执行情况。该电路主要模块是通过模32计数器来,如图5所示[7-9]。

图5 伴随式计算及纠错完成指示电路Fig.5Experiment of scale establishment

4 仿真及应用分析

假设对1500H进行编码,则编码时按1次16比特位,分2次进行装载进入编码电路,分别为0005 H、4000 H,在第27个时钟周期完成编码运算。如图6所示,在第27个clk时钟周期Code_ok信号有效时(高电平),对应输出结果为10 H。加上校验位数据,1500H经过编码后共31位,编码数据分别为0005H、4020H,分别存储在2个存储单元中。

如果读取数据中有一位错误,该错误可能是这31位中的任意一位。在仿真验证时,可以假设错误出现在任意位置,然后分析经过译码器译码后的仿真时序情况。假设数据0005H、4020H在存储过程发生1比特位错误,读出结果为4005H、 4020H,将4005H、4020H载入译码器后的仿真时序如图7(a)所示,在C_OK高电平有效时,伴随式计算完毕。图7(b)为数据纠错部分时序,当伴随式为10010即err_IND信号为高电平时指示错误发生的位置,同时将纠错后的结果输出到移位寄存器中,在C_OK为高电平时即为纠错后的输出结果,读出Pout[25..0]为0001500H,说明发生错误的位被纠正。

图7 译码器仿真时序Fig.7The decoder simulation timing

5 结论

本文根据LED大屏幕显示器显示信息特点,设计了一套基于(31,26)循环纠错系统的软硬件实现方案。实验证明,论文设计方案可以有效降低Flash存储器存储误码率,对提高系统稳定性具有积极意义,论文设计电路具有较好的扩展性和代表性,并具有很好的实用价值。

参考文献:

[1]尹柱霞,郑喜凤,于洪涛.ARM+FPGA控制的LED脱机屏系统设计[J].液晶与显示,2010,25(2):262-267.

Yin Z X,Zheng X F,Yu H T.Design of LED off-line screen system based on ARM+FPGA control[J].Chinese Journal of Liquid Crystals and Displays,2010,25(2):262-267.(in Chinese)

[2]刘卫.NAND Flash控制器的设计与验证[D].长沙:国防科学技术大学,2008.

Liu W.Design and verification of NAND Flash controller[D].Changsha:National University of Defense Technology,2008.(in Chinese).

[3]郭宝增,邓淳苗.基于FPGA的LED显示屏控制系统设计[J].液晶与显示,2010,25(3):424-429.

Guo B Z,Deng CM.Design of LED display control system based on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2010,25(3):424-429.(in Chinese)

[4]朱云芳,靳桅,邬芝权.LED条形显示屏直通连接的数据组织方式[J].液晶与显示,2011,26(6):796-799.

Zhu Y F,Jin W,Wu Z Q.Data Organization of LED bar display panel with shoot-through connection[J].Chinese Journal of Liquid Crystals and Displays,2011,26(6):796-799.(in Chinese)

[5]Mielke N.Marquart T.Ning W.Bit error rate in NAND Flash memories[J].Reliability Physics Symposium,2008.IRPS 2008.IEEE International,2008:9-19.

[6]邓春健,安源,吕燚.显示信息高速串行传输的差错控制[J].光学精密工程,2012,20(3):632-642.

Deng C J,An Y,Lv Y.Error control of high speed serial display data transmission[J].Optics and Precision Engineering,2012,20(3):632-642.(in Chinese)

[7]孙科林,周维超,吴钦章.高速实时光纤图像传输系统的实现[J].光学精密工程,2011,19(9):2228-2231.

Sun K L,Zhou W C,Wu Q Z.Realization of high-speed real-time optical filber image transmission system[J].Optics and Precision Engineering,2011,19(9):2228-2231.(in Chinese).

[8]孙卓,权笑,王文博.采用分组纠错编码的多接入传输分集方法[J].北京邮电大学学报,2009,32(5):6-9.

Sun Z,Quan X,Wang W B.A Method of multi radio transmission diversity with packet level forward error correction[J].Journal of Beijing University of Posts and Telecommunications,2009,32(5):6-9.(in Chinese).

[9]柴先明,彭耿,师栋锋.基于匹配搜索的伪随机序列生成多项式估计[J].光学精密工程,2011,19(9):2223-2228.

Chai X M,Peng G,Shi D F.Generator polynomial estimation of pseudo-random sequence based on match-searching[J].Optics and Precision Engineering,2011,19(9):2223-2228.(in Chinese).

Error control of display data based on flash memory

ZHOU Wen-hui1,2,DENG Chun-jian1,3*,GUAN Xiang-fei3

(1.Zhongshan Institute,University of Electronic Science and Technology of China,Zhongshan 528402,China; 2.School of Automation Engineering,University of Electronic Science and Technology of China,Chengdu 610054,China; 3.School of Computer Science&Engineering,University of Electronic Science and Technology of China,Chengdu 611731,China)

Flash memory is often used as display information storage devices of embedded large screen display system,however flash memory exists errors such as bit upset in reading or writing operation,that will bring the hidden dangers to normal display of system.Flash memory error rate and display data access characteristics are analyzed to design the display data error control under flash memory.Considering the characteristics of embedded control system,a(31,26)cyclic Hamming encoding and decoding circuit is designed,which can reduce the error rate of an order of magnitude,and enhance the ability of anti burst interference and anti random interference,at the same time have the design of low complexity.

TP79

A

10.3788/YJYXS20153004.0660

周文辉(1972-),男,广东中山人,博士研究生,副教授,研究方向为控制理论与控制工程、控制技术应用。E-mail:386722335@qq.com

1007-2780(2015)04-0660-06

2015-01-04;

2015-03-07.

国家自然科学基金项目(No.61302115);广东省自然科学基金(No.S2013010015764);广东省高等学校优秀青年教师培养计划项目(No.Yq2013204);中山市产学研结合项目(No.2013C2FC0014);电子薄膜与集成器件国家重点实验室中山分实验室开放基金(No.412S0605)

*通信联系人,E-mail:dengcj80@126.com