高速数字PCB板的信号完整性仿真与验证

2015-03-30张召宾程建军

张召宾,宋 宝,程建军

(1.华中科技大学 机械科学与工程学院,湖北 武汉 430074;2.广州深圳市浩能科技有限公司,广东 深圳 518172)

随着电子设计的快速发展,由IC芯片构成的电子系统朝着大规模、小体积、高速度的方向飞速发展。PCB(printed circuit board)上的微处理器和逻辑电路中的时钟频率越来越高,信号的边沿越来越陡峭,由此带来的信号完整性(signal in-tegrity,SI)问题也越来越凸显[1]。信号完整性广义上是针对在高速产品中由于互连线引起的所有问题,它主要研究互连线与数字信号相互作用时其电气特性参数如何影响高速产品的性能[2]。信号具有良好的完整性是指当在需要的时候具有所必需达到的电压电平数值。差的信号完整性不是由某单一因素导致的,而是板级设计中多种因素共同引起的。在过去的低速时代,电平跳变时信号上升时间[3](一般为信号幅度从10%上升到90%所用的时间)较长,器件间的互连线不至于影响电路的功能,不需要关心信号完整性问题;但如今高速时代来临,随着IC信号的上升时间不断减小,很多都在ps级别,无论信号频率如何,信号沿互连线上的电气特性已不可忽略,互连线必须作为传输线来对待,从而产生了很多以前没有的信号完整性问题[4]。在高速数字电路中,时钟信号是芯片工作的基准频率,数据的传输一般通过时钟进行有序的收发控制,如果时钟信号不准确,芯片就无法正常工作[5]。因此,在高速电路设计中必须考虑整个传导系统对于输入信号的响应时间,这在很大程度上取决于信号在介质中的传输速度和信号的上升时间。实际应用中判断信号是否为高速信号的依据是信号的上升或下降时间而不是信号的时钟速率[6]。

在实际中,反射和串扰是2种最常见的信号完整性问题,其产生的根源均为阻抗。因此,可以采取终端匹配的方法来改善高速时钟信号的传输质量。

1 传输线对信号传输延时的影响

在SI分析中,许多互连的电气模型都被当做传输线。传输线是一种理想的传输模型,用于将信号从一端传输到另一端。常见的传输线有同轴电缆、平行双绞线、微带线、带状线等[7]。传输线通常用2根导线来表示传输线模型,一条称为信号线,另一条称为返回路径。

传输线与电阻、电容和电感这3种理想电路元件的特性大不相同,它有2个非常重要的特性:特性阻抗和传输延时。PCB设计中的传输线分为微带线(microstrip)和带状线(stripline)。微带线是由1根带状导线与地平面构成,中间是电介质。带状线是一条置于2层导电平面之间的电介质中间的铜带。FR-4(大多数PCB板所用的材质)板上信号在微带线和带状线中的传输速度分别为15cm/ns和12cm/ns。

由大量实践得出的经验法则表明,当传输线延时小于信号上升时间的20%时,反射噪声很小,不会影响到电路功能,传输线不需要进行阻抗匹配;当传输延时大于信号上升时间的20%时,传输线上由于阻抗不匹配而产生的反射噪声就会影响到电路功能,必须采取阻抗匹配措施加以控制,否则它将是造成信号完整性问题的隐患。传输线的阻抗也使得传输线之间存在感性和容性阻抗,在高速电路的设计中,具有快速上升时间的器件即使其信号频率不高,布线时也应认真对待以防止过大的串扰。

2 时钟信号的干扰分析

嵌入式运动控制平台CPU(AM335x)采用24MHz外部时钟,内部通过PRCM(power、reset and clock management)模块对时钟进行管理,输出可调节的时钟信号供SDRAM、USB使用。本文采取的DDR和USB时钟信号频率分别为200MHz和48MHz,仿真环境为Allegro PCB SI。Allegro PCB SI是Cadence SPB系列EDA工具之一,针对电路板级的信号完整性和电源完整性提供了一套完善、成熟而强大的分析和仿真方案,并且和Cadence SPB的其他工具一起,实现了从前端到后端、约束驱动的高速PCB设计流程。

2.1 时钟信号的反射现象和解决方案

当信号沿互连线传输时所受的瞬态阻抗发生变化时,就会产生反射。一般低阻抗的源端驱动器和高阻抗的终端接收器不完全和传输线的特性阻抗匹配,信号将在驱动器和接收器之间来回反弹,造成过冲、下冲及振铃现象。当导线大于临界长度(传输线延时等于信号上升时间的20%)时,反射信号就会叠加在高电平处,引起信号完整性问题[8]。定义信号驱动源内阻为R0,传输线特性阻抗为Z0,负载阻抗为RL,信号反射示意图如图1所示。

图1 信号反射示意图

信号从特性阻抗Z0向特性阻抗RL传输的过程中,最佳情况是当R0=Z0=RL时,传输线上阻抗连续,没有反射。当RL≠Z0时,会发生信号反射:当RL>Z0时,多余的能量会反射回源端,反射波极性为正;当RL<Z0时,负载通过反射通知源端输送更多的能量,反射波极性为负。信号在驱动端和负载之间多次反射,还会造成振铃。一个典型的信号振铃如图2所示。

DDR是一类非常特殊的信号,因为其越来越高的工作频率,使得高速硬件设计中,减少其产生的干扰是一个很大的挑战。为了避免传输线效应,按照工作频率达到或超过75MHz时布线就必须按照长度25.4mm以内、线宽0.254mm以上、内部间距0.127mm以上、外部间距0.762mm以上等规则进行设计。对于200MHz的工作频率,必须有更大的冗余度。对SDRAM时钟信号进行仿真的结果如图3所示。

图2 信号振铃

图3 SDRAM时钟信号

由图3可见,经过长距离的微带线传输后,信号由传输线到接收芯片引脚时,由于芯片引脚阻抗很小,信号由高阻抗进入低阻抗介质,出现明显的反射和振铃现象。

减小反射的有效措施是对传输线进行阻抗匹配,在靠近驱动端或负载端加上拉电阻或下拉电阻。从原理上主要分为2类——并行端接和串行端接,同时,每一类又有不同的实现方法。

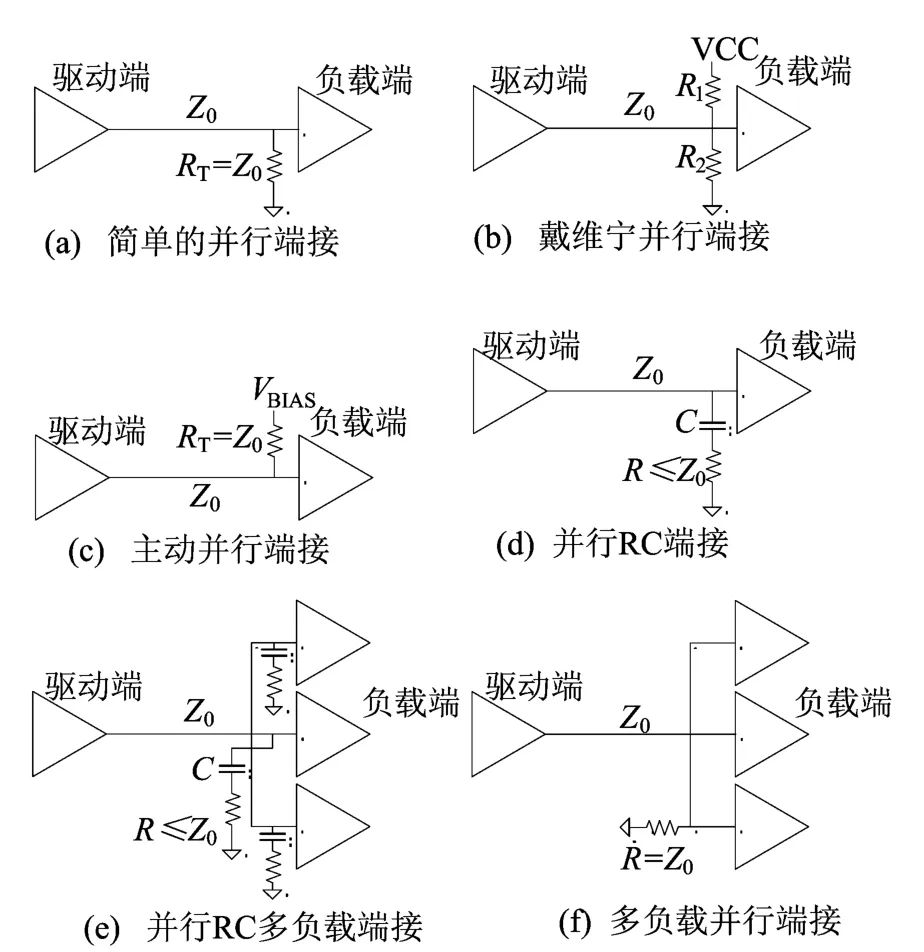

并行端接是在尽量靠近负载的位置加上上拉和(或)下拉阻抗以实现终端的匹配,根据不同的环境,并行端接又分为简单的并行端接、戴维宁并行端接、主动并行端接、并行RC端接和多负载并行端接,如图4所示。

简单的并行端接即在负载端加入1个下拉电阻RT(RT=Z0)来实现匹配,但输出为高电平时这种端接消耗的电流过大,一般器件很难达到驱动要求;戴维宁并行端接是采用上拉电阻R1和下拉电阻R2构成端接电阻,其等效电阻为RT=R1R2/(R1+R2);主动并行端接是用RT将负载信号拉至一偏移电压VBIAS,VBIAS的选取依据是使输出驱动源具有对高、低电平信号汲取电流的能力;并行RC端接是用串联RC作为端接阻抗。多个负载时需要在每个负载端都进行端接,才能更好地达到阻抗匹配的效果。

图4 不同方式的并行端接

串行端接是在尽量靠近源端的位置串行插入一个电阻RS(10~75Ω)到传输线中来匹配信号源阻抗,条件为RS+R0≥Z,多负载时同样采取多负载串行端接,如图5所示。

图5 不同方式的串行端接

2.2 时钟信号的串扰现象和解决方案

信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为串扰,其耦合机制主要分为容性耦合与感性耦合。容性耦合是由于干扰源上的电压变化在被干扰对象上引起感应电流从而导致的电磁干扰,而感性耦合则是由于干扰源上的电流变化而导致的电磁干扰[9]。用C12表示两线间耦合电容,当入侵网络变化时,就会产生容性耦合电流,减小容性耦合一个有效的方法就是增大线间距;用M12表示2线间产生的互感,当入侵网络电流变化时,就会产生感性耦合电压[10]。减小串扰的措施可以考虑以下4个方面:① 增大传输线间的距离;② 相邻的信号层走线方向应该相互垂直;③ 在满足特性阻抗的条件下,使布线层与参考平面层间的介质层尽可能薄;④ 根据阻抗匹配原理进行端接。

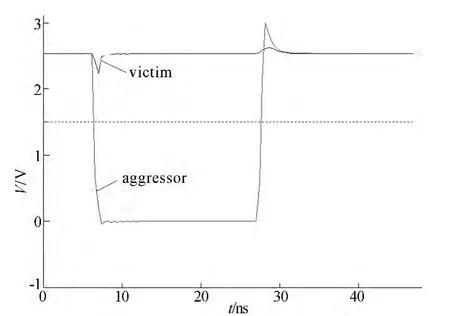

根据串扰产生的条件,在Allegro PCB SI中模拟USB时钟信号受到相邻传输信号的串扰干扰。仿真串扰波形如图6所示,其中aggressor波形是干扰源,victim波形是被干扰信号。由图6可知,相邻的微带线信号对USB时钟信号产生了幅值约为0.3V的周期性串扰。

图6 USB时钟对相邻信号的串扰

3 方案的仿真与验证

3.1 反射的解决方案

采取并行端接的方法减小反射,在SDRAM时钟信号的接收端并联匹配电阻。微带线的传输距离约为30mm,PCB厂商提供的铜微带线的传导率按3.75Ω/cm 计算,微带线的阻抗约为114.3Ω。接收端并联匹配电阻R分别取50、100、150、200Ω进行试验,仿真波形如图7所示。

图7与图3对比分析可知,R=50Ω和R=100Ω对接收端的反射现象改进较明显,但R=50Ω时接收端约有0.2V的压降,对于信号的损失严重,综合比较,R=100Ω的改进效果最优。

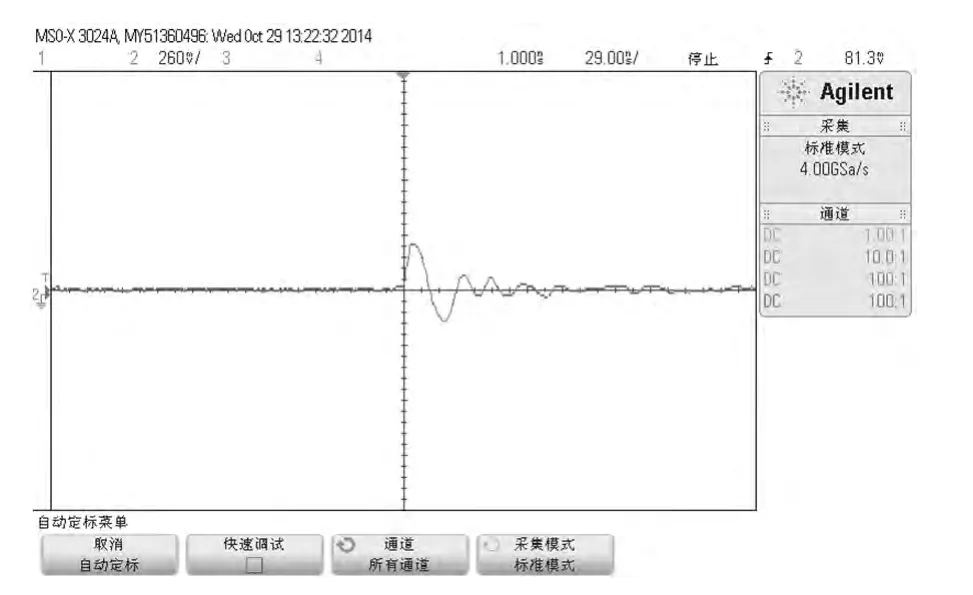

在以ARM+FPGA架构的试验平台进行验证,示波器采用的是Agilent MSO-X 3024A(200MHz,4GSa/s)。原始SDRAM时钟信号波形和在信号末端并行端接100Ω电阻后测得的波形如图8所示。

由图8可以看出,并行端接100Ω电阻后的反射峰值从1.2V下降至0.6V,减少了50%,综合采取其他措施,还可以进一步减小。根据阻抗匹配原理,匹配电阻应与传输线阻抗相等,接收端阻抗无突变,可以保证信号的完整性,所以本实验也验证了阻抗匹配原理。

图7 不同并联匹配电阻的仿真波形

图8 原始SDRAM时钟信号和接100Ω电阻后的信号

3.2 串扰的解决方案

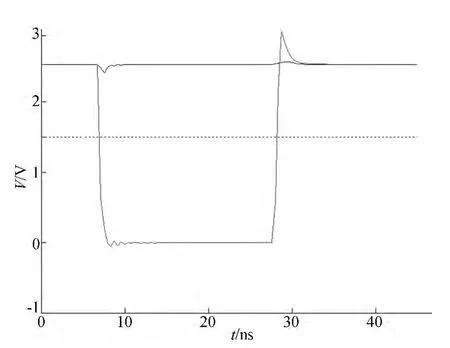

通过调整线间距来减小串扰。将原来的0.127mm增大到0.381mm,结果如图9所示。

图9 线间距为0.318mm时串扰仿真波形

图9与图6对比可以看出,串扰产生的干扰电压已降至0.15V左右。但多数情况下受PCB上的布线空间的限制,加大布线间距难以实现,可以采取阻抗匹配的方法对信号进行优化。在源端并行端接120Ω(等于传输线的阻抗)的电阻后的仿真波形如图10所示。

由图10可以看出,经过阻抗匹配的串扰基本消除,但是同时也使信号产生了很大的损耗,实际设计中应该权衡串扰的程度与因采取阻抗匹配而带来的信号衰减的幅度,选取合适的改进措施。

图11所示为高速信号对相邻信号产生的串扰干扰,原始间距为0.127mm,干扰源信号频率为10MHz,幅值为5V,可见其产生了约1 000mV的串扰干扰,因此,该干扰脉冲的快速边沿在被干扰线上产生了约20%的串扰。

图10 阻抗匹配后串扰仿真

图11 原始的串扰信号

根据布局布线的3W原则,可将线距加大至0.609 6mm(线宽为0.203 2mm),为了使效果更明显,同时PCB的空间足够大,所以试验时将线间距调整到0.762mm,并端接120Ω电阻。测得的信号如图12所示。

图12 加大线间距并端接后测得的串扰信号

由图12可知,尽管串扰一定程度上还存在,但已经从原始的1 000mV降到了200mV左右,对于5V的干扰源而言,取得了明显的改善。高密度复杂PCB设计中的信号完整性是一个复杂的系统工程,完全避免串扰是不可能的,单一的改进措施对串扰的改善也并不明显,串扰与其他信号完整性问题需要综合措施来改善和避免。

4 结束语

本文首先基于阻抗匹配的理论基础,研究了反射和串扰等信号完整性问题产生的原因,利用Cadence的Allegro PCB SI工具对反射与串扰现象进行了仿真再现。其次,探索了能够提高系统信号完整性,减小反射、串扰的措施,并在Cadence环境下仿真出通过并行端接改善后的信号波形,验证了其理论可行性。最后,通过一款ARM+FPGA架构的试验平台进行实际测试,验证了该方法是减小串扰和反射、提高系统信号完整性的有效方法。

[1]周 萍.高速PCB板的信号完整性设计[J].电子质量,2009(1):32-36.

[2]王 娟,杨明武.传输线上反射与串扰的仿真分析[J].合肥工业大学学报:自然科学版,2012,35(2):197-200.

[3]周 路,贾宝富.信号上升或下降时间对高速电路信号完整性影响的研究[J].现代电子技术,2011,34(6):69-73.

[4]Ren G,Zhou R.The signal integrity analysis of differential signal based on hyperLynx[C]//International Conference on Computer,Mechatronics,Control and Electronic Engineering.IEEE,2010:269-272.

[5]李英丹,郑 拓,钱新平.基于IBIS模型的高速Loadboard设计信号完整性仿真研究[J].现代电信科技,2012(1):43-48.

[6]姜 樟,齐剑锋.嵌入式系统电磁兼容性综述[J].科技广场,2010(5):240-242.

[7]Zhou Xiquan,Hui Pengfei,Miao Fengjuan,et al.Highspeed signal transmission on signal integrity analysis[C]//Advances in Biomedical Engineering,Vol 11,2012International Conference on Electrical and Computer Engineering.Elsevier Science,2012:11.

[8]李 健.基于Cadence的信号完整性研究[D].西安:西安电子科技大学,2009.

[9]王雪坤.高速电路设计中的信号完整性分析[D].苏州:苏州大学,2013.

[10]许凯华,董淑云,刘玉华,等.基于S3C2440嵌入式系统主板的电磁兼容性设计[J].现代电子技术,2010,33(20):29-32.