运载火箭时序仿真测试系统设计

2015-02-21马雪松姚静波解维奇裴珊珊装备学院研究生院北京046装备学院航天装备系北京046东北财经大学工商管理学院辽宁大连602

马雪松,姚静波,解维奇,裴珊珊(.装备学院研究生院,北京046;2.装备学院航天装备系,北京046;.东北财经大学工商管理学院,辽宁大连602)

运载火箭时序仿真测试系统设计

马雪松1,姚静波2*,解维奇1,裴珊珊3

(1.装备学院研究生院,北京101416;2.装备学院航天装备系,北京101416;3.东北财经大学工商管理学院,辽宁大连116023)

摘要:检测运载火箭地面测试设备的方法种类繁多,方法复杂,测试周期较长。设计一种运载火箭时序仿真测试系统,采用FPGA芯片的SOPC(可编程片上系统)技术,基于全双工USB 3.0控制芯片(CYUSB3014)完成上位机通信,单板模拟运载火箭飞行过程中64路时序系统发出的时序信号和时串信号,对不同测试需求的地面测试设备进行功能检测和故障诊断。具有方法简单,通用性好、精度等级高、通道数多的优点,能有效提高地面测试设备在测试任务中的测试效率。

关键词:运载火箭;测试; USB 3.0; CYUSB3014; SOPC

地面测试设备进行检测时,传统的方法存在以下几点不足:

(1)测试方法复杂传统箭机等效器只能输出关键时序信号,时串信号需要各功能模块配合箭机时序信号发出,且时间修改难度大,对测试系统检测不具有通用性。各型号地面设备配套的测试仪器种类繁多,通用性差[3]。

(2)测试性能低采用分立的仪器或设备对各通道进行测试,存在维护性差,人为误差大等特点[4]。

(3)测试周期长通过设计独立等效器[5]或其他检定装置进行测试,往往测试通道数少,对于具有百路以上多通道地面设备的测试,工作量大,测试周期长。

(4)研发成本高不同型号运载火箭存在不同地面测试设备,单独设计配套测试仪器通用性较差,仅能满足对应地面测试设备的测试需求,导致当前地面测试设备存在大量不同种类的检测设备和仪器。

本文设计时序仿真测试系统对地面测试设备进行检测,具有测试方法简单,通用性好,精度等级高,通道数多的优点。

一直到四月一日,孙山才来电话,说:“小说家这样写,S决定先离开果城,得摆脱一切可能的盯梢者,吃过大亏了,不能重蹈覆辙。他找了一个清静之所,闭关修炼——在云南香格里拉的建唐镇隐居,那时还不叫香格里拉,叫中甸。他购买了十几本如何成为一位私家侦探的书籍,潜心研读,甚至旁涉了法学、心理学、刑侦学等相关学科,对擒拿格斗及枪械也略有兴趣,还去散打俱乐部训练了三个月。一年多之后,他自信远非吴下阿蒙,萌生了开一家私家侦探社的想法。那个年月,以抓小三、讨欠薪、刺探商业机密等为主要业务的私家侦探社游走于灰色地带,在大城市像雨后春笋冒出来——”

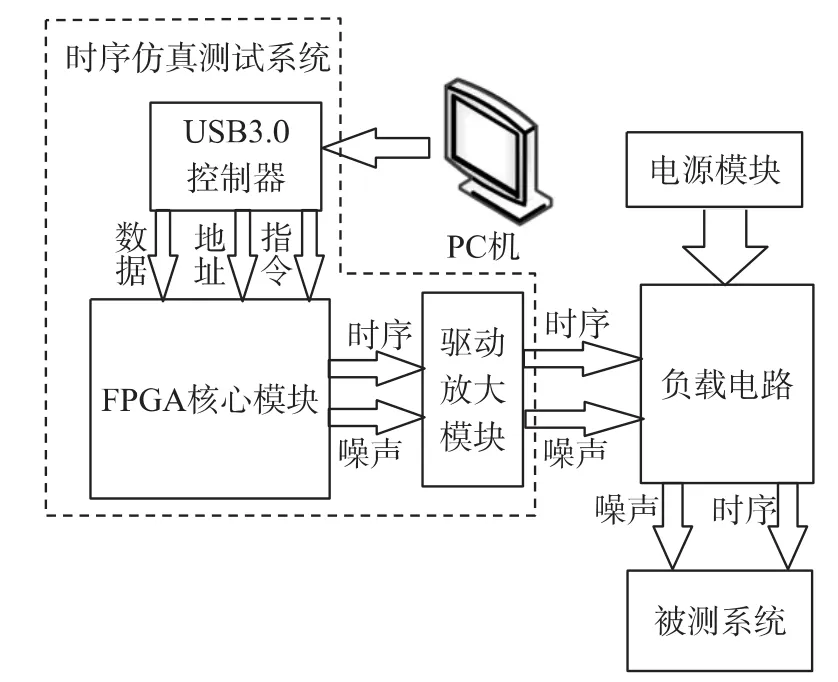

1 设计框架和结构

时序仿真测试系统模拟运载火箭时序系统,发出64路时序信号和时串信号,同时可模拟噪声时序信号,对地面测试设备进行检测。上位机可根据不同型号火箭灵活配置时序信息,通过USB 3.0接口传送至下位机FPGA,经驱动放大模块输出,增加系统通用性。USB 3.0具有SS(Super-speed)传输模式,增加时序信号分辨率,提高了时间精度。FPGA采用SOPC(可编程片上系统)技术进行逻辑设计。FPGA根据所接收的指令和数据信号,发出被测系统所需时序信号,同时可模拟发出噪声时序信号,由DAC和驱动放大模块将信号功率放大后输出到负载电路。驱动放大模块主要采用ULN2803集成IC作为驱动。外部单独设计电源模块,用于控制输出的时序信号电压幅值,满足不同电压等级时序信号的输出,即可得到被测系统所需的时序信号和噪声时序信号。设计总体框架如图1所示。

图1 时序仿真测试系统框架图

1.1 USB 3.0控制器设计

1.1.1 USB 3.0芯片简介

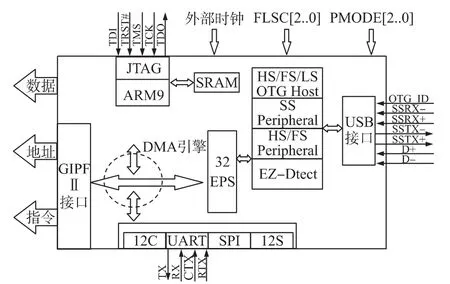

USB 3.0控制器采用Cypress公司的EZ-USB FX3 (CYUSB3014)控制芯片,可工作于SS模式,实现5 Gbit/s的理论传输速度。芯片内嵌32 bit的ARM9处理器,最高工作频率可达200 MHz。芯片内嵌512 kbyte/256 kbyte SRAM用于存储代码、配置参数以及DMA通道数据缓存,USB接口含有32个EPS(16个输入端点和16个输出端点),同时可配置I2C、UART、SPI、I2S接口外设[6]。USB 3.0接口设计具有灵活性、可扩展性等特点,其目的均是实现高速、可靠的数据传输,增加时序信号分辨率,提高时间精度。

1.1.2芯片外围设计

系统所用USB接口采用Micro type B接口,该接口支持OTG(On-The-Go)功能,支持HNP(主机通令协议)和SRP(对话请求协议)以及ID引脚的检测,设备可配置工作于A设备(主机)或B设备(从机)。

通过配置PMODE[2: 0]引脚为F11,配置EZFX3固件启动方式为USB boot模式[7]。外部接口关闭I2C、SPI、I2S接口,配置JTAG接口和UART接口。JTAG接口用于对EZ-FX3进行测试和固件程序调试; UART接口输出调试信息,如波特率设置、停止位奇偶校验设置等信息。EZ-FX3时钟源通过配置FSLC[2: 0]为000,采用19.2MHz的无源晶振提供时钟信号。数据传输模式通过固件配置设置为SS传输。

GPIFⅡ为高性能可编程接口,其设计工程采用Cypress公司提供的GPIFⅡDesigner软件完成设计,最后实现GPIFⅡ接口和FPGA的数据。指令、地址等信号的通信。EZ-FX3硬件结构设计框图如图2所示。

图2 EZ-FX3结构框图

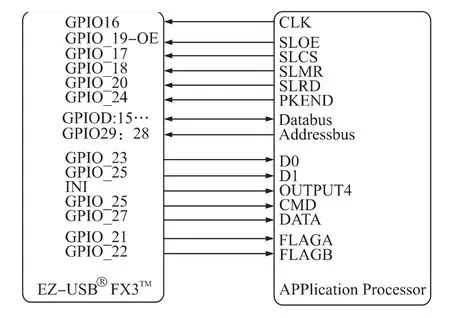

GPIFⅡ通道为高性能的通用可编程接口,可实现256种编程状态,接口频率可达100 MHz[6],采用GPIFⅡDesigner软件实现接口状态机的快速开发,通过GPIFⅡ接口实现数据交互。

为更好模拟运载火箭飞行时序信号,设计运载火箭飞行过程中的故障噪声信号用于对地面测试设备故障诊断能力进行检测。为了保证PC对FPGA噪声模块的配置不影响PC机时序信号信息的传输,GPIFⅡ接口设计两组数据传输通道进行数据传输,用于提高数据传输效率和数据可靠性。第1组通道设计为Slavefifo传输模式,该模式用于时序信息的传输,数据传输位宽设计为32 bit,CLK为时钟信号,SLOE、SLCS、SLWR、SLRD、PKTEND为EZ-FX的控制信号。2 bit地址总线是线程地址,该总线可根据所用线程数目也可配置为5 bit。标志位FLAGA配置为DMA通道线程0溢出标志位,FLAGB配置为线程1溢出标出位。第2组信号为D[1: 0]、CMD、DATA信号。D[1: 0]通道为实现数据/指令复用通道,CMD、DATA为控制信号,控制D[1: 0]复用通道的输出信号。采用GPIFⅡDesigner软件设计GPIFⅡ硬件接口设计图如图3所示。

图3 GPIFⅡ硬件接口设计图

Slavefifo模式数据传输选用同步数据传输,同步时钟信号通过PCLK管脚由FPGA内部锁相环输出80 MHz时钟信号。结合Slavefifo模式同步数据读写时序逻辑图,采用GPIFⅡDesigner软件平台设计状态转换图,结合状态转换图设计对应的时序逻辑图,GPIFⅡDesigner编译通过后生成的、C文件,该文件为固件程序开发中不可缺少的文件[8]。GPIFⅡ接口写状态的状态时序逻辑图如图4所示,将SLOE、SLRD、SLCS置于有效位时开始数据读取状态,Databus总线的数据信号滞后于地址总线3个周期,滞后与SLRD信号两个周期。FLAGA、FLAGB配置为线程0线程1的标志位,可根据需求配置为“full”、“not full”、“empty”、“not empty”等工作状态。此处配置为“empty”、“not empty”。当线程为空,FLGAA或FLAGB输出标志位为0,此时EZ-FX3不能向外读出数据,当线程存在数据,FLAGA或FLAGB输出标志位为1,此时外部处理器可读出EZ-FX3内部数据。

图4 GPIFⅡ写状态时序逻辑图

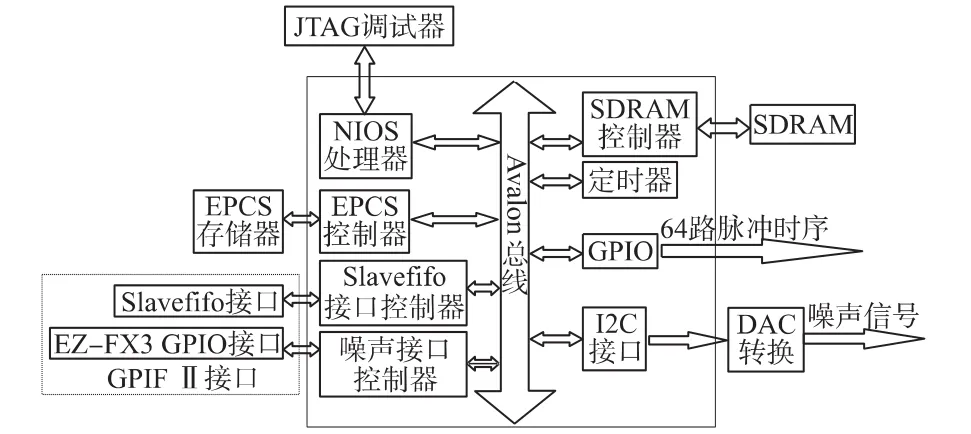

2.2 FPGA核心模块设计

2.2.1 FPGA设计框图

FPGA选用Altera公司的CycloneⅢ系列,型号为EP3C16F484N的芯片,基于SOPC(可编程片上系统)技术设计,采用NIOS处理器,通过Avalon总线完成各外设及内部模块之间的数据交互。Quartus 9.0软件平台完成IP硬核调用和自定义内部逻辑设计,实现64路时序信号输出,同时可模拟含有噪声的时序信号,对设备进行故障诊断测试。SDRAM存储器选用K4S641632芯片,EPCS存储器用EPCS64I18N,EPCS芯片可存储FPGA配置数据和NIOS处理器软件程序,同时将程序引导到SDRAM中运行。DAC芯片采用DAC5571,该芯片有高速I2C输入的8 bit DAC,采用I2C接口进行数据传输,DAC内部完成串并转换和数模转换,可将噪声数字编码转换为模拟量输出。FPGA核心模块设计图如图5所示。

图5 FPGA核心模块设计

2.2.2 FPGA组件逻辑设计

采用SOPC技术进行设计,其中一个主要优势就是Altera公司SOPC Bulider提供了丰富的IP核,通过IP核的调用使得系统的设计变得简单。时序仿真测试系统中SDRAM、EPCS、GPIO(通用接口)均可调用IP核完成组件设计,实现同NIOS处理器的通信。DAC数模转换芯片和EZ-FX3结合其接口通信协议设计逻辑组件,并将组件封装,通过Avalon总线实现和处理器及其他逻辑组件的通信。

(1) I2C接口IP核设计

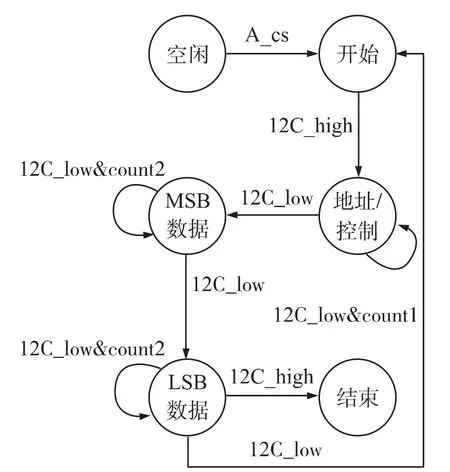

DAC5571芯片采用I2C接口进行数模通信,该接口可减少硬件资源消耗,节约FPGA的IO管脚等优点。I2C接口硬件设计逻辑组件状态转换图如图6所示。逻辑模块存在6个状态,空闲状态下通过Avalon总线片选信号选通后,由I2C_ high信号控制状态机开始工作,同时该信号也可以控制状态机的停止,使状态进入Stop状态。DAC芯片一次数模转换需要I2C接口3 byte的数据写入,状态机采用3个状态来实现,3个状态间通过I2C_low触发过渡。地址/控制状态通过计数器1完成第1个字字节的写入,该字节包含地址位和读写控制位; MSB数据状态通过计数器2完成第2个字节的写入,该字节包含控制位和数模装换数据的高四位; LSB数据状态通过计数器2完成第3个字节的写入,该字节高四位为数模转换数据低四位。3个字节写完后由I2C_low和I2C_high决定是否继续写入数据。

图6 FPGA核心模块设计

(2) GPIFⅡ接口IP核设计

EZ-FX3外设的FPGA接口组件包含两部分,用于完成两个通道数据的传输,通道①为大量时序信号数据的传输,通道②为控制信号和噪声编码信号的传输。GPIFⅡ接口通道一采用Slavefifo工作模式配置,FPGA内部设计对应Slavefifo硬件逻辑组件用于控制EZ-FX3和FPGA时序信号的数据传输。Slavefifo工作模式包括同步和异步的读写模式,每种模式下各管脚的时序逻辑均不同。要提高数据传输速率,增加时序信息的分辨率,采用同步时序接口数据传输。硬件组件逻辑设计严格按照EZFX3接口时序图和时序参数进行设计[9]。硬件逻辑组件通过Verilog实现,利用Modelsim 6.3软件平台进行时序仿真,仿真时序图如图7所示。Reset重置后,逻辑组件处于空闲状态,通过Avalon总线片选信号启动和读信号启动Slavefifo硬件逻辑组件,模块内设计32 bit的FIFO缓存EZ-FX3的数据,通过状态机设计完成数据写入FIFO以及读出。PCLK为写入时钟,时钟周期频率为80 MHz,即GPIFⅡ接口Slavefifo模式在80 MHz下数据传输速率可达2.56 Gbit/s,CLK1为Avalon总线数据读取时钟,该时钟可以控制数据读取分辨率,在CLK1时钟下,即可实现32 bit时序信号数据的读取,数据通过Avalon总线经GPIO接口输出。同步时序读数据工作模式下,32 bit接口数据信号比FIFOADDR[1: 0]地址信号延迟3个周期,比SLRD信号延迟两个周期,故输出信号dataout比datain信号延迟两个周期。通过FLAGA和FLAGB为线程溢出标志位,1为“not empty”,0为“empty”,当FLAGA读取空后,地址线0数据读完,切换到线程1,开始读取线程1数据。

通道二组件模块噪声控制器的主要作用是完成EZ-FX3和FPGA第2通道数据的传输,该通道的搭建目的是不影响通道一的数据传输速率,该通道具有数据量小、逻辑设计简单的特点,输入控制信号CMD、DATA控制输入为控制信号还是噪声数据信号,内部设计FIFO,通过Avalon总线完成同处理器和I2C接口模块的数据通信。

图7 Slavefifo接口控制器时序仿真图

2 软件设计

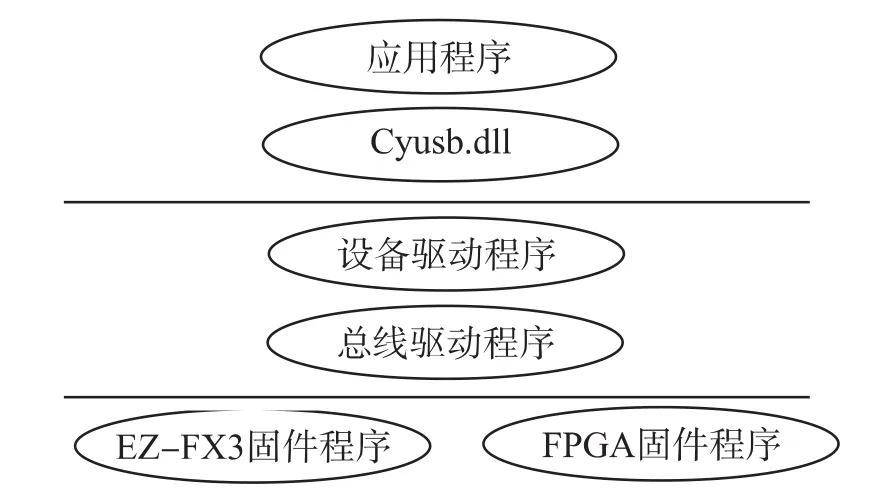

时序仿真测试系统的软件设计主要包括应用程序、驱动程序、固件程序设计[10],其软件设计模型如图8所示。

图8 软件模型

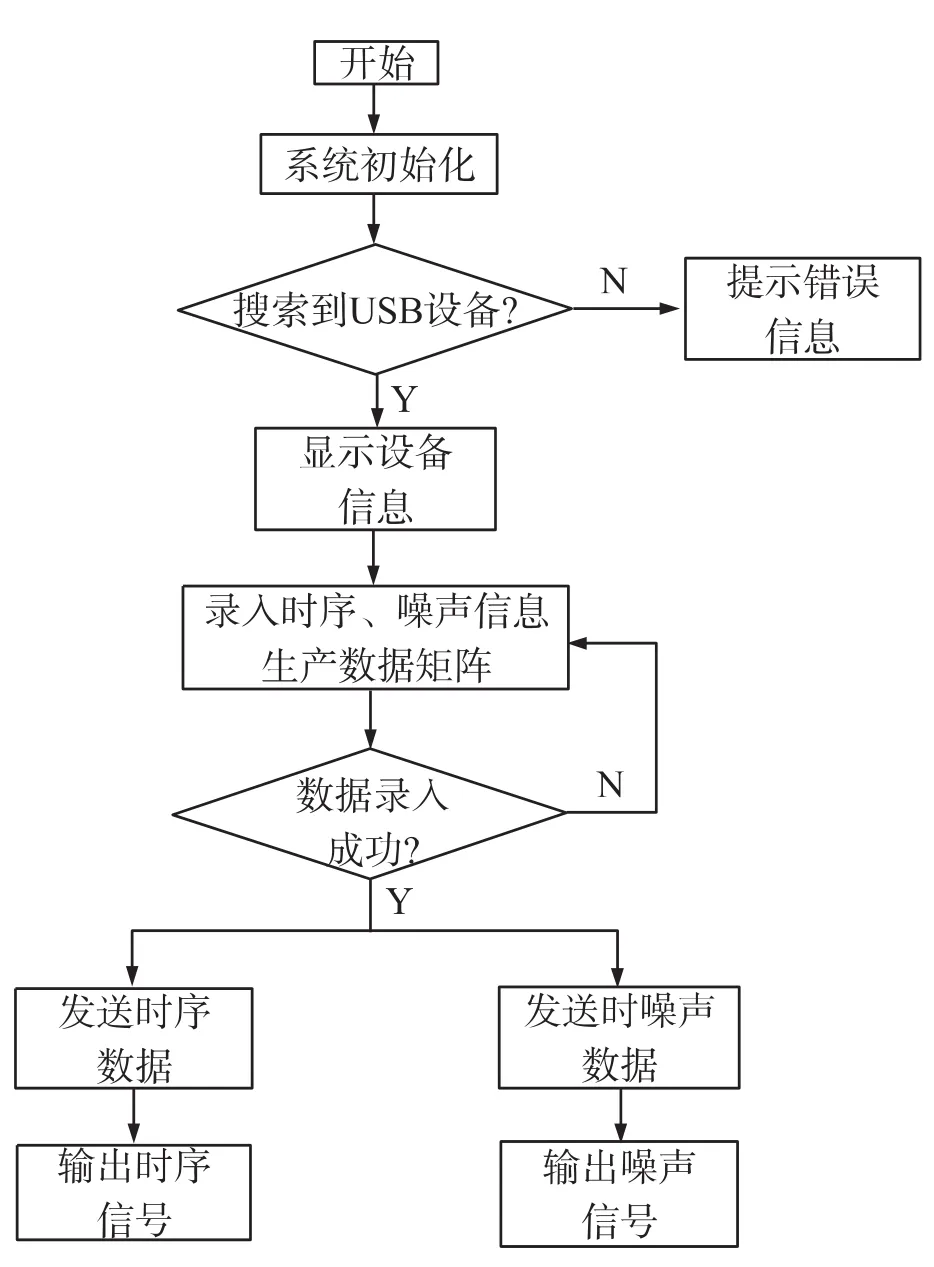

应用程序采用Visual studio设计,通过Cyusb.dll库文件与操作系统通信,设备驱动用于应用程序和总线驱动之间的数据交互,总线驱动则是包含在计算机操作系统内的驱动,负责管理计算机和底层硬件设备的通信。硬件固件程序包含两部分,EZ-FX3固件程序用于配置FX3芯片,FX3内部的ARM芯片是基于Thread实时操作系统[5],对FX3固件程序的开发采用Cypress的SKD开发包,开发环境用Ecliplse。FPGA固件程序有两部分,配置FPGA内部SOPC系统的硬件平台配置文件和系统嵌入式应用软件,前者采用Quartus软件开发,后者采用Nios IDE软件进行开发,之后将两部分文件配置到EPCS芯片进行固化。系统上电后进行初始化,根据VID和PID搜索系统中的INI文件,通过INI文件实现设备驱动程序的安装。设备添加失败则提示相应错误信息,添加成功则通过应用程序对时序信息和噪声信息进行参数配置,完成配置后即可通过应用程序开始对时序信号进行输出。系统工作流程图如图9所示。

3 结果

通过通用计数器E312A对时序仿真测试系统时序信号的时间精度等级进行结果检定,E312A时间间隔测量范围为0.25 μs至10 s,晶振精度达±5×10-8,精度等级较高。假定时序仿真测试系统通道1时序信号第1次高电平触发时间节点为火箭点火信号时间节点,对各个通道时序的时间间隔进行检定,检定结果精度等级可达到0.1 μs,由此可得时序仿真测试系统具有较高的时间精度。

4 结束语

运载火箭时序仿真测试系统设计,可实现单板输出64路时序脉冲信号和含有噪声的脉冲信号对被测系统进行功能检测和故障诊断测试,输出时序信息分辨率高,提高了时序信息精度,通过配置外接电源模块控制信号输出幅值,可实现不同电压等级时序信号的输出,满足不同火箭型号对应不同地面测试设备的测试需求。利用该测试系统,实现“即插即测”,具有测试速度快、测试方法简单、通用性好、时序精度高等特点,对后续运载火箭测试任务的顺利进行具有重要意义。

图9 系统工作流程图

参考文献:

[1]穆山,毛万标.运载火箭控制系统[M].北京:国防工业出版社,2003: 160-185.

[2]冉隆燧.运载火箭测试发控工程学[M].宇航出版社,1989: 73-91.

[3]程龙,姚静波,解维齐,等.运载火箭控制系统信号综合测试方法[J].兵工自动化,2012,31(8) : 10-13.

[4]王建政,李云峰.基于PXI总线的运载火箭地面测试设备计量检定系统设计[J].计量与测试技术,2013,40(7) : 7-8.

[5]苏虎平,沈三民,刘文怡,等.基于USB和FPGA的多功能等效器设计[J].电视技术,2012,36(23) : 50-53.

[6]Cypress Semiconductor.EZ-USB FX3 Super Speed USB Controller.Revision 1[C]/ /2011: 3-9.

[7]Cypress Semiconductor.EZ-USB FX3 Boot Options,Revision C [C]/ /2013: 3-11.

[8]Cypress Semiconductor.Cypress GPIFⅡDesigner Guide[C]/ / 2011:5-18.

[9]Cypress Semiconductor.Designing with the EZ-USB FX3 Slave FIFO Interface,Revision I[C]/ /2013: 3-19.

[10]Cypress Semiconductor.FX3 Programmers Manual,Revision G [C]/ /2013: 51-78.

马雪松(1989-),男,四川冕宁人,硕士研究生,主要从事飞行器测试方向的研究,1071150758@ qq.com;

姚静波(1969-),男,甘肃甘谷人,副教授,主要从事测试技术方向的研究。

Design of Data Acquisition System Based on C/S Structure for High-Speed Railways Earthquake Early Warning*

TAN Chao*,SU Chao,ZHANG Haibin

(College of Electrical Engineering and New Energy,China Three Gorges University,Yichang Hubei 443002,China)

Abstract:24-bit data acquisition system is designed based on C/S structure for High-speed Railways earthquake early warning,the hardware of system contains control board and detachable data acquisition board.Control board is composed of STM32F407 microcontroller,SD memory card and Ethernet interface,the main function of control board contains data sampling control,storage and transmission; data acquisition board is composed of FPGA control board and 6-ch 24-bit sampling card,which functions include data sampling,packing and transmission.The C/S structure software is achieved by transplanting LwIP in server,implementing network function by LabVIEW in client,which function include remote parameter setting and data waveform display.The test result shows that: the acquisition system channel consistency is good,and the SNR is better than 140dB on the condition of 200 sample/s sampling rate.

Key words:high-speed Railways earthquake early warning; C/S structure; data acquisition system; synchronization sampling; FPGA

doi:EEACC: 7210G10.3969/j.issn.1005-9490.2015.02.042

收稿日期:2014-04-27修改日期: 2014-05-27

中图分类号:TN79.1; TP206.1

文献标识码:A

文章编号:1005-9490(2015) 02-0436-06