基于Verilog HDL数字式竞赛抢答器的制作

2015-01-22□程琼

□程 琼

一、引言

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),于1995年成为IEEE标准(即IEEE Std 1364-1995)。它是以文本形式来描述数字系统硬件的结构和行为的语言,可用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。作为业界使用最广泛的硬件描述语言之一,有大量的电子设计自动化工具对它予以支持。通过使用集成开发环境,设计人员可以在常见的Windows或其它图形化系统中进行设计、仿真、验证。

现代数字系统的设计多采用自顶向下(TOP-DOWN)的设计方法,自顶向下的设计方式有利于系统级别层次的划分和管理,提高效率、降低成本。基于Verilog HDL设计并实现的数字式竞赛抢答器,自顶层设计各个阶层,成本低,操作简便、可靠性高,有着广泛的应用前景。

二、系统设计原理及总体模块设计

数字式竞赛抢答器要求具有四路抢答输入,能够识别最先抢答的信号,对回答问题所用的时间进行计时、显示,能进行抢答报警及超时报警,可以预置回答问题的时间,同时具有记分和复位功能。

(一)系统设计原理及开发平台。采用自顶向下的设计方法,把系统划分为几个基本模块,再把每个基本单元划分为下一层次的基本单元,一直下去,直到划分为一个个简单的功能模块为止。设计的实现采用的是EDA Pro2K实验开发系统,所用芯片为ALTERA的FLEX10K系列中的EPF10K10LC84-4,系统设计所用软件为MAX+plus2 10.0。

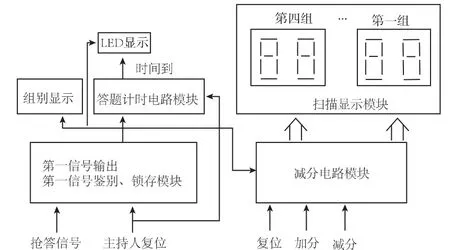

图1 系统总体结构图

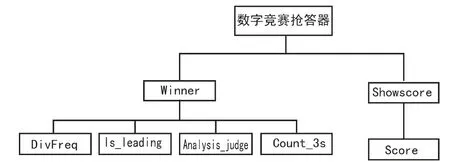

(二)系统总体模块设计。根据系统的功能要求,构造系统总体结构图,如图1。根据系统总体结构图,再结合自顶向下的设计思想,系统基本模块可分为Winner(锁定抢答胜出者模块)和Showscore(各选手的分数显示模块)。设计系统总体模块树如图2。

图2 系统总体模块设计

三、系统各模块设计及其仿真实现

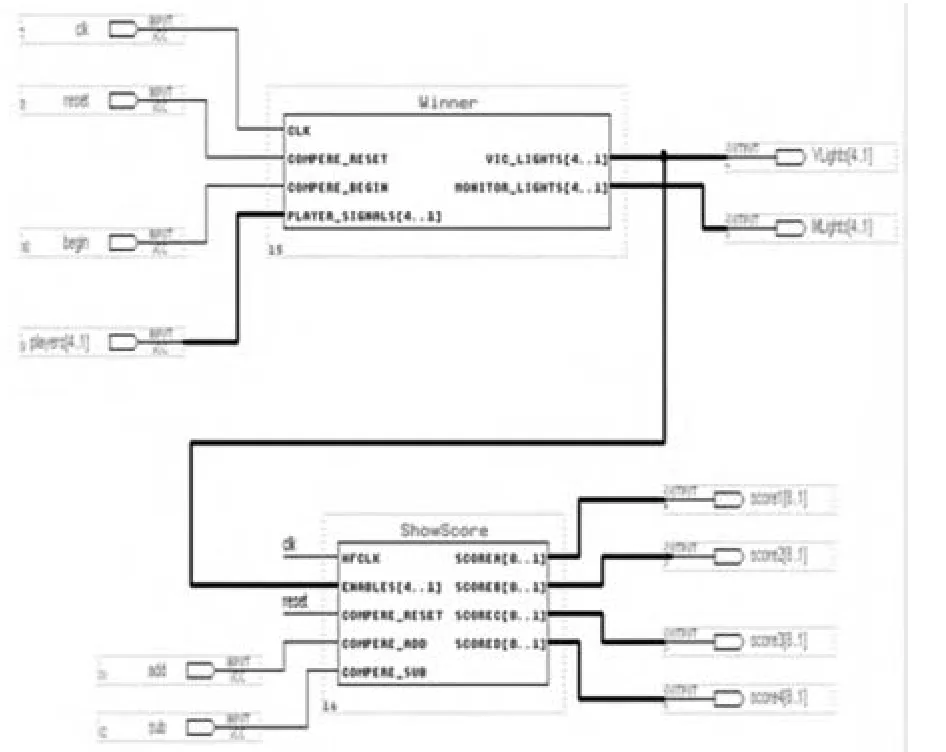

(一)系统总模块。系统总模块即是将两个独立的基本模块Winner和Showscore连接起来,使其实现完整的系统功能,其连接图如图3。

图3 Winner和Showscore连接图

(二)Winner模块。此基本模块的功能是选出4位选手中的抢答胜出者,并对超前抢答的选手予以犯规提示;选出优胜者后,若此选手在规定的时间内未回答出来问题,同样也予以提示。该模块的主要代码及注释如下:

module Winner(clk,compere_reset,compere_begin,player_signals,Vic_Lights,Monitor_Lights);

input clk,compere_reset,compere_begin;//输入信号:时钟脉冲、主持人复位和开始信号

input[4:1]player_signals;//输入信号:4位选手的抢答信号

output[4:1]Vic_Lights,Monitor_Lights;//输出信号:提示成功抢答和犯规抢答的信号灯

reg[4:1]Vic_Lights,Monitor_Lights;

reg[1:0]judgeA,judgeB,judgeC,judgeD;//中间变量:标识4位选手的抢答动作是否犯规的编码

wire ok;//中间变量:标识是否已有选手成功抢答

reg time_up;//中间变量:从成功抢答开始计时到3秒钟的标志信号

reg clk_256,clk_512;//中间变量:分频信号,用于计时和提供不同的监督提示信号

divFreq divF_0(clk,compere_reset,clk_256,clk_512);

//对1kHz的时钟脉冲进行分频

is_leading is_leading_1(clk,clk_256,player_signals[1],compere_reset,compere_begin,judgeA),

is_leading_2(clk,clk_256,player_signals[2],compere_reset,compere_begin,judgeB),

is_leading_3(clk,clk_256,player_signals[3],compere_reset,compere_begin,judgeC),

is_leading_4(clk,clk_256,player_signals[4],compere_reset,compere_begin,judgeD);

//对各选手抢答行为进行编码

Analysis_judge analysis_1(clk,clk_256,clk_512,compere_reset,time_up,judgeA,ok,Vic_Lights[1],Monitor_Lights[1]),

analysis_2(clk,clk_256,clk_512,compere_reset,time_up,judgeB,ok,Vic_Lights[2],Monitor_Lights[2]),

analysis_3(clk,clk_256,clk_512,compere_reset,time_up,judgeC,ok,Vic_Lights[3],Monitor_Lights[3]),

analysis_4(clk,clk_256,clk_512,compere_reset,time_up,judgeD,ok,Vic_Lights[4],Monitor_Lights[4]);

//对各选手抢答行为的编码进行解码,并驱动各提示灯

assign ok=Vic_Lights[1]||Vic_Lights[2]||Vic_Lights[3]||Vic_Lights[4];

//判断是否产生了最先抢答成功选手

count_3s count_3s0(clk,clk_256,compere_reset,ok,time_up);

//产生了最先抢答成功选手后,开始计时3秒

采用自顶向下的设计方法,将Winner模块进一步分层,Winner模块可分为divFreq子模块、is_leading子模块、Analysis_judge子模块、count_3s子模块等,对应功能及实现如下:

1.divFreq子模块。实现对1kHz的输入脉冲进行分频,得到4Hz和2Hz的脉冲,这些分频脉冲用于计时和提供不同的监督提示信号。

2.is_leading子模块。用于判断选手是否有超前犯规动作,输出一个两位的用于判断选手是否超前抢答犯规的编码。

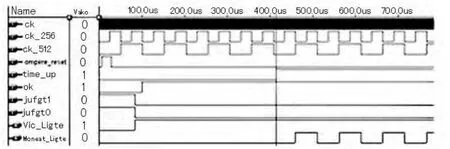

3.Analysis_judge子模块。用于对标识选手是否犯规的标识码进行解码,若选手成功抢答且之前无其它选手成功抢答,则通过成功抢答灯(Vic_Light)予以提示,如图4;若选手超前犯规抢答,则通过监督灯(Monitor_Light)予以提示,闪烁频率为4Hz;若选手在规定时间内(3秒)未答对,则通过监督灯(Monitor_Light)予以提示,闪烁频率2Hz。

图4 此选手抢答成功仿真图

4.count_3s子模块。用于计时,在得到最先抢答选手时,启动此计时器,当过了3秒后此计时器输出一个高电平信号time_up,即相当于一个3秒计时器。

(三)Showscore模块。此基本模块为在每次抢答决出优胜者后,主持人可根据其回答问题的对错,对其分数进行加减,并予以显示,即记分模块。

module ShowScore(HFclk,Enables,compere_reset,compere_add,compere_sub,

scoreA,scoreB,scoreC,scoreD);

input HFclk,compere_reset,compere_add,compere_sub;//输入信号:1kHz脉冲、主持人的复位信号、加信号、减信号

input[4:1]Enables;//输入信号:4个使能信号,只有当此选手为优胜者时主持人才可对其分数进行操作

output[8:1]scoreA,scoreB,scoreC,scoreD;//输出信号:4位选手的分数

reg[8:1]scoreA,scoreB,scoreC,scoreD;

Score score1A(HFclk,Enables[1],compere_reset,compere_add,compere_sub,scoreA),

score1B(HFclk,Enables[2],compere_reset,compere_add,compere_sub,scoreB),

score1C(HFclk,Enables[3],compere_reset,compere_add,compere_sub,scoreC),

score1D(HFclk,Enables[4],compere_reset,compere_add,compere_sub,scoreD);

//在使能端的控制下,主持人对优胜者的分数进行操作

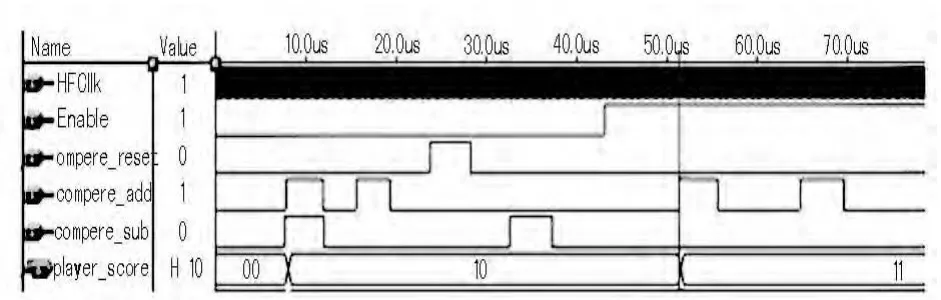

采用自顶向下的设计方法,将Showscore模块进一步分层,Showscore模块还包括Score子模块,Score子模块实现对选手的分数进行初始化,主持人可以对选手的分数进行加和减,如图5。

图5 选手记分模块仿真

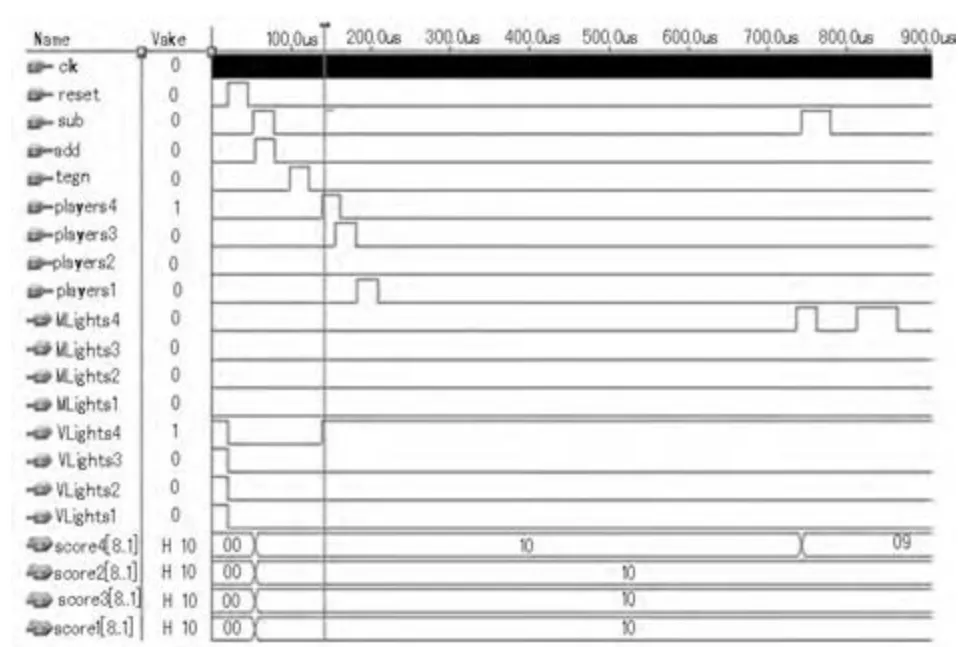

(四)系统仿真测试。在各位选手均无犯规行为如超前抢答的情况下,实现的效果如图6。

图6 抢答正常情况仿真图

其中,clk为周期为200ns的脉冲;reset为主持人复位信号;sub和add为主持人加减分信号;begin为开始信号;player分别为4位选手的抢答信号;MLight分别为4位选手的监督提示灯信号;VLight为4位选手的胜出抢答信号灯;Score为4位选手的成绩显示。以上信号均为高电平有效。

可见,在本轮抢答中,在主持人按下add和sub后,选手的分数得到初始化;在主持人按下开始键后,4号选手最先抢答成功,所以其成功抢答指示灯VLight4亮,并且过了3秒钟后其监督指示灯(MLight4)低速闪烁。假如本轮比赛4号选手答错,则主持人可以将4号分数减少,变为9分。

另外,系统设计在每轮比赛中,只给每位选手一次抢答机会,选手一旦按键后,以后按键将会无效,这是为了防止有选手不停按键以骗取答题机会。

四、结语

本系统采用自顶向下的设计思想,即先要对系统功能进行分析和划分,即分为选出抢答胜出者模块和记分模块。系统设计要求四路抢答输入,故选出抢答胜出者模块可以分为4个相同的小模块。Verilog HDL设计中模块之间为并行执行,可以根据各位选手的抢答情况判断整轮比赛的抢答情况。同样,对于记分模块,也可细化到一位选手的记分情况。这样,不同的选手都可以套用同一个模块,提高了模块的利用率,也使系统更简单明了。

[1]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009

[2]王思淼,陈战胜,胡正坤.数字竞赛抢答器的设计与实现[J].齐齐哈尔大学学报,2013

[3]http://baike.baidu.com/linkurl=Q0mT90ZQ1eUteVwTOH wUMVqhsmEFejasUiOKelkpQY66GQGbNy1Y3XW4RpkQKJrHb CpqjurArFqHgWE0Or1bJq