基于FPGA的视频转换器的设计及其IP核实现*

2014-11-23胡捃云利军石俊生高银雷连莎

胡捃, 云利军, 石俊生, 高银, 雷连莎

(1.云南师范大学 颜色与图像视觉实验室,云南 昆明650500;2.云南师范大学 信息学院,云南 昆明650500)

1 引 言

随着科学技术的飞跃发展,视频图像已成为人们生活必不可缺的信息载体.LVDS低压差分信号传输是20世纪90年代产生的一种数据传输和接口转换技术,因其具有高速、低噪声、低EMI、低电源、低损耗等特点,因而成为高速视频的首选接口标准[1].由于不同显示设备的接口标准不同,因此需要视频转换器对视频信号进行转换从而使其在不同设备上显示.本文应某航空研究所对高速视频传输系统的要求,基于FPGA技术,设计一个将通用PAL制模拟视频信号转换成XGA格式的LVDS信号的视频转换器,其中将视频处理的相关算法——去隔行、帧频提升制成IP核形式,以便后来开发者的复用.

2 PAL-LVDS视频转换器硬件设计

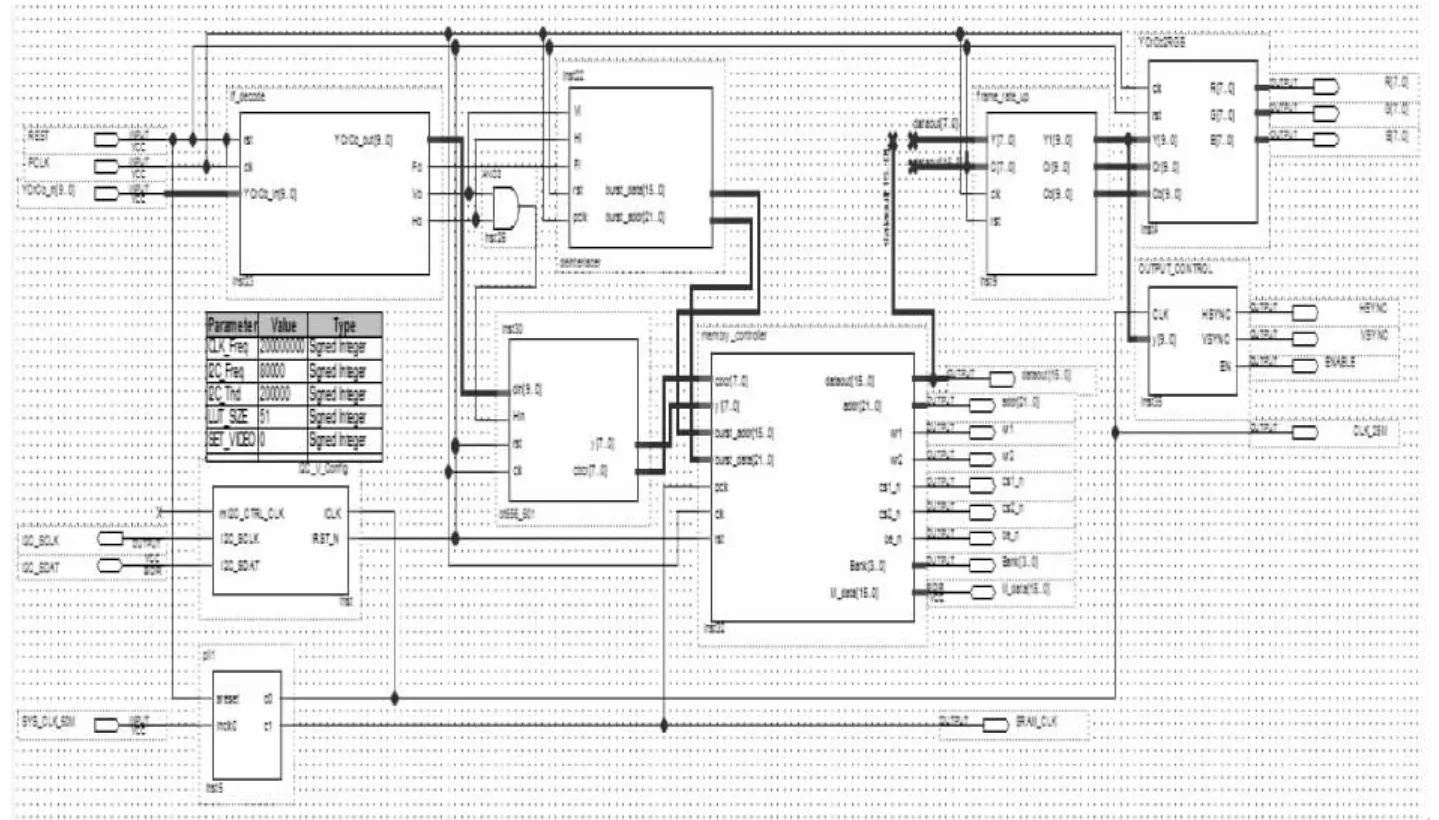

本设计以FPGA为平台,将原始的隔行扫描的PAL制模拟视频信号转换为逐行扫描的XGA形式的LVDS视频信号,并使图像的分辨率由720×576提高到1 024×768.即PAL-LVDS视频转换器主要完成的功能包括视频信号的采集、分配、存储以及显示,其中包括去隔行技术、分辨率转换、帧频转换、色度空间转换等视频处理.系统的总体结构及其功能框图如图1所示.其中,FPGA依靠像素时钟和行、场同步信号采集SAA7111A解码器输出的视频数据YUV信号,并利用双SRAM模块进行视频图像处理,最后通过编码器(DS90C383)对信号进行编码输出LVDS视频信号.

图1 PAL-LVDS视频转换器结构框图Fig.1 The structure diagram of PAL-LVDS video converter board

2.1 解码模块

解码芯片选用Philips公司生产的SAA7111A芯片,它由主控芯片FPGA(EP2C8F256I6)通过IIC串行总线对其进行初始化配置.SAA7111A 芯片具有如下优点[2]:①它有4路输入视频模拟信号 AI11、AI12、AI21、AI22,其视频输入信号可以是复合视频信号(CVBS)或2路S-Video模拟输入信号;②能自动识别NTSC和PAL输入视频信号;③支持YUV的输出格式有4:2:2(16Bit)、4:2:2(8Bit)、4:1:1(12Bit)或RGB输出格式有8:8:8(24Bit)、5:6:6(16Bit);④通过IIC配置能调节信号的亮度、对比度和饱和度[3].

2.2 存储模块

系统需要将分辨率为720×576@25帧/秒、隔行扫描的PAL制模拟视频信号转换成分辨率为1 024×768@60帧/秒、逐行扫描的XGA格式信号,这需要一系列视频图像算法来完成.区别于普通静态图像处理,在视频图像处理过程中要求视频显示输出的流畅性和实时性.考虑到这一点,系统选用两块大容量SRAM用于FPGA外围存储视频图像.在这次设计中,SRAM芯片选用的是Cypress公司的高速、大容量存储器CY7C1061AV33(1M×16bits).两块 SRAM 与FPGA芯片在进行通信时,通过乒乓操作和相关算法来完成视频格式转换.

2.3 编码模块

编码模块选用的是国际半导体公司生产的编码芯片DS90C383.该芯片是一款功能强大的串行传输芯片,它可以将24位的并行视频数据转换为标准的串行差分接口信号(LVDS)来输出.DS90C383支持像素时钟为20~65MHz,传输的数据量可高达1.8Gbps,符合TIA/EIA-644LVDS标准[4].

3 PAL-LVDS视频转换器软件设计及相关IP核生成

PAL-LVDS视频转换器软件设计主要包括解码器的配置、隔行扫描转逐行扫描的设计、分辨率转换的设计、帧频变换的设计等,其中本文把隔行扫描转逐行扫描的设计和帧频变换的设计制成IP核,以便后来开发者的复用.视频转换器的软件设计及相关IP核生成框图如图2所示.

图2 视频转换器的软件设计及相关IP核生成框图Fig.2The video interface converter for software design and generate relate IP cores

3.1 隔行扫描转逐行扫描IP核的生成与验证

将PAL模拟视频信号由隔行扫描变为逐行扫描,目前主要有场内插值法、场间插值法、基于运动估计的自适应插补法[5],基于这几种方法的优缺点,本文选用场间插值法来实现去隔行.

场间插值方法在硬件上实现是通过两片SRAM在FPGA的控制下进行乒乓操作完成的.首先SAA7111A解码器输出的隔行扫描视频信号的第一帧的奇数场数据流缓存到SRAM1中,这意味着每写一行地址需要空出一行地址给偶数场数据流,然后在实际操作中将偶场数据流插入SRAM1中的奇数场数据流中.在操作完成后,一幅完整的图像就存储到SRAM1存储器中.然后第二帧视频信号按相同的方法依次存入到SRAM2中.与此同时,FPGA将已经存入到SRAM1中的第一帧视频数据顺序读出.乒乓操作使得SRAM1和SRAM2一直处于读写的状态中,完成隔行扫描到逐行扫描的转换.

首先,在 Quartus9.0中用硬件描述语言Verilog HDL将PAL制模拟视频信号由隔行扫描变逐行扫描进行描述,并对其进行编译、综合、验证成功后,则可转化为IP核形式,即创建一个design partion输出网表文件(.qxp文件).

按照这样的开发流程,在建立新的工程时可以直接调用该网表文件,在新建工程中根据提供的端口信息实例化这个设计模块,与其他模块进行逻辑连接,即可缩短开发周期.调用生成的去隔行IP核的RTL框图,俗称黑盒子,如图3所示,单击该框图即可察看到该IP的端口信息,但无逻辑关系.

图3 调用IP核RTL图Fig.3 Call the RTL map of IP core

最后,在QuartusII 9.0中利用硬件描述语言Verilog HDL对其进行调用、编译并进行仿真验证,其仿真波形如图4所示.

图4 去隔行仿真波形Fig.4 The simulation waveform of de-interlacing

图4 中的pixel_clk、key依次为像素时钟27 Mhz、复位信号,Fi、Vi、Hi依次为PAL信号的奇偶场信号、行消隐信号和场同步消隐信号,中间变量 wr_burst_address和 wr_burst_data依次为写入SRAM的地址和数据,rd_burst_address和rd_burst_data依次为从SRAM中读出的地址和数据.从图中可知,经去隔行处理后,输出数据的形式为奇偶行交错输出,继而验证了该去隔行技术的可行性.

3.2 分辨率转换的设计

本文实现的功能之一为实现分辨率增大,即视频信号的分辨率由720×576扩大到1 024×768.分辨率的放大,使得行同步频率和每场行数都得到增加,这样每场就会有新数据产生,则像素的时钟频率和每行像素量均有相应的增加,每行就需有新像素值生成.采用均匀插值方式,即对存放原始信号数据的SRAM产生有重复的地址计数值作为SRAM的读取地址,实现对某些行的某些像素进行重复读取.为了保证变换后图像拉伸均匀,对写入的视频数据的分辨率实现3∶4的放大,读出的视频数据的分辨率变为960×768.

上面还没有达到设计的需要,此时根据人眼对黑点的识别度不高,在各帧图像的每行两边各加32个黑点,分辨率即达到1 024×768.根据分辨率变换值累加法,分辨放大后为1 024×768的XGA格式的LVDS信号,此时像素时钟为50 Mhz.分辨放大前后每行像素数量变换比值为720∶1 024.用像素时钟从0开始计数,并从初值0开始每20ns进行模720累加1 024计算.加法器在每个时钟上升沿时,将初值(一开始为0)加720,若结果小于1024,则直接作为下次的累加初值;若结果大于等于1 024,则结果减去720作为下次累加初值.像素时钟的计数通过累加结果进行使能控制:若累加结果小于1 024时,则不允许计数;当累加结果大于等于1 024时,允许计数,这样每1 024次累加中会有720次允许计数,即每1 024个时钟均匀产生了720个有重复的计数值,该计数值就作为读取RAM的像素地址.

行数变换同上,分辨率放大后对其进行行同步计数,使能控制由累加去模计算的结果来决定,而RAM的读取行地址为计数值.

3.3 帧频变换IP核的生成与验证

本设计采用帧复制法[6],将视频信号的帧频由隔行扫描的25帧(每写入5帧50Hz信号)变为逐行扫描的60帧(输出6帧60Hz信号).在选择的乒乓操作中,每输入一帧原始信号进行一次乒乓操作.在一个操作的周期内,在向写SRAM中写入原始数据的一帧后,由另一个SRAM读出该信号,当前的帧就完成了输出,接着,开始读取写RAM的首行数据,从而开始输出新的一帧.即读SRAM行地址计数器从原值继续计至最大值后再从0开始计数,共完成约1.2个计数周期,即每经过5次乒乓工作切换,读SRAM的行地址计数器计满6个周期[7].其中每5帧图像中第1帧图像传输两遍,即可达到最后输出的图像帧频为60帧.

首先,利用Quartus II 9.0用硬件描述语言Verilog描述该模块,编译综合成功后,对其进行仿真,若满足帧频提升的目的,再将源文件导出成一个网表文件(.qxp)和布局布线信息,制成IP核.调用该IP核的RLT框图如图5所示,单击该框图即可察看到该IP的端口信息,但无逻辑关系.

图5 调用帧频提升IP核RTL图Fig.5 The RTL map of frame rate up-conversion IP core

其中,在Quartus II 9.0中采用Testbench结合Modelsim对其进行仿真验证,其仿真波形如图6所示.图中,中间变量 wr_pic_number、rd_pic_numeber分别为存入SRAM中视频信号的图片数、从SRAM中读出的视频信号的图片数.波形显示写入图片数5张,读出图片数6张,说明输出信号每隔5帧重复一帧,满足系统设计需求.后来开发者在建立新的工程时根据提供的器件名,可以直接调用该IP核,与其他模块进行逻辑连接、例化,从而可以缩短开发周期.

图6 帧频提升仿真波形Fig.6 The simulation waveform of frame rate up-conversion

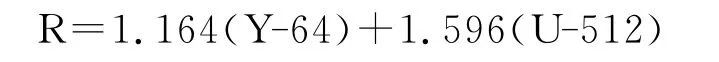

3.4 YUV-RGB转换设计

PAL视频信号的主要特性之一为其颜色模型YUV,本系统图像传感器输出格式为4∶2∶2的YUV信号,需要将其进行RGB信号转换,转换后的格式为8∶8∶8,然后通过自行设计的XGA转DVI视频转换器来观察显示效果.根据ITU-RBT.656视频标准接口,对于位宽为10比特的视频数据,PAL的RGB颜色空间与YUV颜色空间的转换关系如下[8]:

在Quartus 9.0中,使用Verilog HDL对其进行描述,因为我们输入的PAL制视频数据位宽为10,而YUV的比例为4∶2∶2,所以其仿真的值依次为 Y-64、U-258、U-258,并满足 Y 分量取值为 16-235,U 和 V 分量的取值为 6-240.用Modelsim对YUV_RGB.v程序进行仿真后的结果如图7所示.

图7 YUV_RGB仿真程序图Fig.7 The simulation waveform of YUV_RGB

4 实验结果及分析

搭建调试硬件平台和软件平台,通过配置SAA7111A各个寄存器后,数字视频信号的每个像素时钟、水平频率和垂直频率均满足设计要求,并在带DVI接口的显示器上观察到显示效果.图8所示为硬件电路的开发和实验结果,其中图8(a)为视频信号硬件电路板,图8(b)为调试后的显示效果.

图8 测试平台和实验结果:(a)视频转换接口板;(b)调试后的显示效果Fig.8 Test platform and the experimental results:(a)The video adapter plate;(b)The display after debugging

5 结 论

本文设计的是基于FPGA技术上实现的视频转换器PAL-LVDS,并将视频处理方法中的隔行转逐行技术、帧频提升分别生成IP核形式.根据自顶向下的设计思想,将其进行层次功能划分,并对各子模块进行仿真验证,实现了视频信号的采集、分配、存储、去隔行、分辨率放大、帧频放大及色度空间的转换.本文生成的IP核具有很好的可移植性,便于再次复用,缩短设计周期.

[1]张光烈,郑南宁,吴勇,等.面向格式转换的数字视频处理方法及其实现硬件实现[J].中国工程科学,2001,3(6):41-47.

[2]胡海英,胡冰,赵新田,等.用SAA7111A设计模拟视频转换接口[J].电子技术应用,2003,29(1):52-54.

[3]王前,吴淑泉,刘喜英.基于FPGA的IIC总线接口实现方法[J].微电子技术,2002(3):21-26.

[4]CEA-861-D 1-176,2006SCEA Standard A DTV Profile for Uncompressed High Speed Digital Interfaces[S].Arlington:Consumer Electronics Association,2006.

[5]张旭.基于FPGA的PAL-XGA图像转换控制器设计[D].哈尔滨:哈尔滨工业大学,2007.

[6]张旭,王彬.一种基于FPGA的实时图像转换控制器设计[J].图像与多媒体技术,2007(10):66-68.

[7]郑永进.视频格式转换算法研究及FPGA实现-去隔行、帧频转换、分辨率变换[D].东南大学硕士学位论文,2007.

[8]PILLAI LATHER.Color Space Converter[EB/OL].http://courses. cs. washington. edu/courses/cse567/03au/homework/color.pdf.