基于双口RAM实现双核通信模块的驱动设计

2014-09-28潘必超

潘必超,曹 彪

(1.广东机电职业技术学院信息工程学院,广州510515;2.华南理工大学机械与汽车工程学院,广州510640)

基于双口RAM实现双核通信模块的驱动设计

潘必超1,曹 彪2*

(1.广东机电职业技术学院信息工程学院,广州510515;2.华南理工大学机械与汽车工程学院,广州510640)

传统单核心控制器受制于硬件结构相对封闭,可控参数有限,一定程度上影响了工艺过程控制的灵活性。设计一种开放式的控制器,实现过程控制网络化是当今物联网发展的趋势。文章基于嵌入式Linux系统平台,使用高速双端口RAM芯片CY7C024AV2,提出一种模块化的DSP与ARM的双核通信模块方案及其驱动程序的设计,实现了控制器的双核数据通信功能,为控制器的网络智能控制建立了软件基础。实验证明,该驱动程序的支持下控制器的双核数据通信性能满意。

嵌入式;双核;物联网;驱动程序

随着物联网产业的发展,工业控制智能化需求日渐提高。控制器除了要肩负自身过程控制的基本功能外,还应该具备一定的对外界环境的感控功能,从而实现物物相连。这就要求控制器必须具有开放的接口并实现高效的数据交互技术。就电源控制器领域来说,近年来以DSP、ARM为数字化控制核心的焊接电源成为了研究的热点,由于其高性能高可靠性得到了广泛的应用[1-2]。配合嵌入式Linux操作系统的开放性,控制器将具有更高的控制灵活性。但过去的控制器硬件架构相对比较封闭。若在控制器中实现开放的网络接口,实现控制器网络互连,过去传统面向焊接工艺过程控制具有单一处理器架构的控制器则难以满足需求。为了满足电源控制器联网而产生的复杂多任务需求,ARM与DSP构成的双核控制器架构日趋普及。目前双核控制器的工业解决方案常见两种:单芯双核与双芯双核。考虑到尽量保留已有产品硬件结构基础上,并结合控制器成本、模块化设计以及并行开发问题,本文采用双芯双核的松耦合架构实现控制器。对于该种架构,包含双核通信协议IPC的驱动程序设计则成为了设计的关键点和难点[3-5]。本文提出了一种基于双端口芯片CY7C024AV2实现控制器双向异步通信的方案,并在Linux下实现了ARM与双端口RAM的驱动程序。实验结果证明,该通信架构具有较高的可靠性。

1 核间通信的硬件电路连接

CY7C024AV2是由Cypress公司专门为多核通信而推出的一款双端口异步存储芯片。该芯片可作为RAM芯片独立使用,也能同时与两种不同速率的MCU相连接实现传输速率匹配。且内置了多种防止数据访问冲突的保护机制。该存储芯片的存取周期达到20 ns,理论带宽可以达到50 Mbit/s×16 bit/s。图1给出了ARM芯片AM1808以及C2000系列DSP与双端口RAM接口互连电路模块的电路原理图。AM1808使用EMIFA(External Memory Interface A)与CY7C024AV2其中一个端口相连接。EMIFA是AM1808用于与外部存储器连接访问的控制器[6],其主要用途是提供一种通用的连接方法,使CPU能与多种不同的外部存储设备相连接。这些外部设备可以是SDRAM、Flash与SRAM。在本设计方案中,线路连接的时候需要注意的是EMIFA的数据位宽是32位的,而CY7C024AV2是16位存储器[7],在地址总线上,采用了EMA_BA_1引脚连接到了CY7C024AV2的最低地址线。这样就使得通信双方地址空间相匹配,均为16位数据存储单元地址。而DSP端的数据位宽是16位[8],与CY7C024AV2相一致,所以无需做特别处理。

图1 控制器内双核间通信接口原理

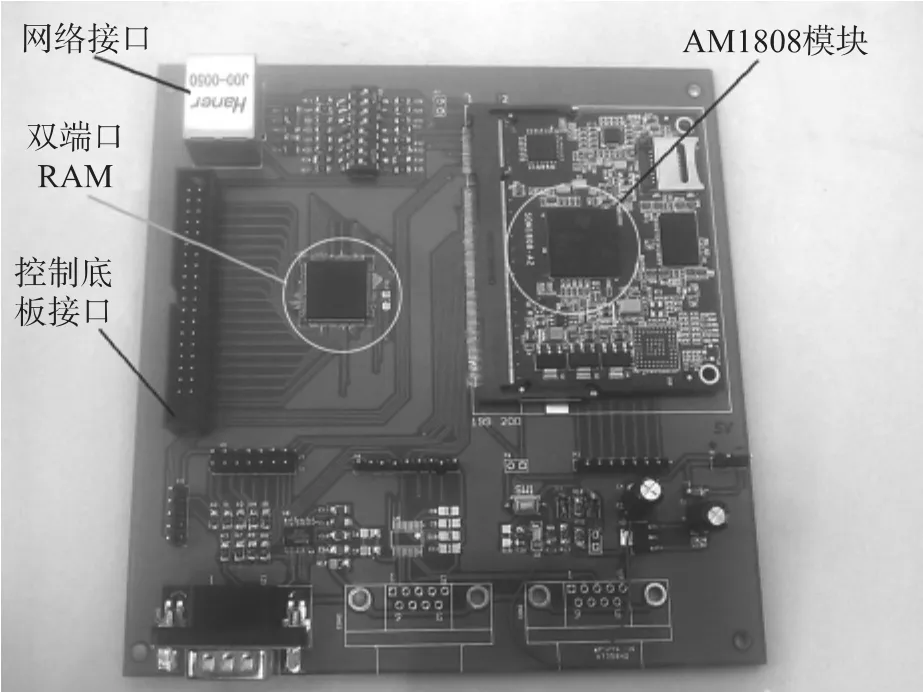

硬件设计上,基于本文双核通信方案网络扩展模块(后面简称为模块)的电路板实物如图2所示。模块上集成了调试COM口、以太网口、IP地址拨码器、双端口RAM以及基于DDR2接口封装可拆卸AM1808模块。模块与逆变焊机控制底板使用图示模块左边缘排线接口相连。模块化的设计更有利于整机成本的控制。

图2 控制器双核通信电路扩展模块

2 驱动程序设计与实现

嵌入式Linux系统主要通过驱动程序来驾驭硬件设备。驱动硬件是操作系统最基本的功能,并且提供统一的操作方式。嵌入式Linux驱动的一个重要特点就是将所有的设备都当作是文件进行处理[9]。因此,嵌入式Linux下的设备驱动程序设计主要需要完成3个任务,分别是硬件板级初始化、驱动程序初始化以及驱动程序文件接口的实现[10]。驱动程序整体结构如图3所示。

图3 通信模块驱动程序结构

2.1 板级初始化工作

本控制器ARM采用的AM1808,Linux在加载驱动程序前,ARM访问双端口RAM所使用的EMIFA接口的数据IO、地址IO和控制IO引脚必须处于正常的工作模式。工作模式由相应的MUX寄存器决定的,可以通过宏MUX_CFG实现工作模式的切换,使用代码如下:

上述代码中,MUX_CFG宏的第6个参数为关键参数,该参数的取值则为该IO引脚的实际工作模式。

其次,板级初始化还需要配置EMIFA访问时序参数,该参数设置了总线接口中的访问控制线在一次读动作以及一次写动作中的逻辑时序,该参数的取值主要由被访问芯片的推荐工作参数决定[6-7]:

static struct davinci_aemif_timing da850_evm_sram_timing=

在BSP源码包中,结构体davinci_aemif_timing定义了EMIFA总线访问读、写时序的6个重要参数。上述代码中相应时间参数的单位是EMIFA总线时钟周期。默认情况下,总线时钟周期是系统时钟周期的2分频。

2.2 设备的文件接口的实现

Linux驱动程序将设备视为文件。除了网络设备之外,字符设备和块设备都被映射到Linux文件系统的文件和目录。可以采用访问文件的方式访问物理设备[11-12],见图3所示字符设备驱动结构。但前提是在驱动中需要实现若干文件访问接口。通过文件系统的系统调用接口open()、write()、read()、close()等函数即可访问设备。

本文驱动程序中访问双端口 RAM芯片CY7C024AV2需要实现的文件访问接口包括:

(1)打开芯片(文件)接口 这里主要负责EMIFA接口工作模式的初始化;在内核空间中申请足够的缓冲空间;分配填写至于filp->private_data的数据结构;检查双端口RAM芯片是否就绪等。

(2)释放芯片(文件)接口 释放已申请的缓冲区空间以及系统分配的内存空间。这里包括打开芯片时候分配的 filp->private_data所指向的内存空间。

(3)读取芯片(文件)接口 该接口的主要作用是将双端口RAM中的数据通过调用copy_to_user ()函数实现从内核空间向用户空间复制数据;从而实现读取双端口RAM的功能。

(4)写入芯片(文件)接口 该接口的主要作用是调用copy_from_user()函数实现从用户空间将数据复制到内核空间,从而实现写入双端口RAM的功能。

(5)索引芯片(文件)接口 EMIFA功过在16bit异步数据收发模式,在RAM芯片寻址时候相应地也要实现基于双字节为单位的偏移量计算。从而才能正确定位数据收发的起始地址。

本驱动程序中,file_operations结构体的配置代码如下:

文件访问接口中比较关键的是两个操作。第一是实现从内核空间到用户空间的数据传递。copy_ from_user函数,主要实现从用户空间向内核空间传递数据。而copy_to_user函数实现从内核空间向用户空间发送数据。第二是实现物理地址向内核地址的映射,即ioremap()函数的调用。

2.3 驱动程序初始化

从AM1808参考手册可以查到EMIFA接口的物理地址是0x60000000,需要在驱动程序头文件中声明双口RAM的物理地址常量SRAM0_PHYADDR。同时双端口RAM覆盖2 kbyte地址空间,需要声明内存容量MEMDEV_SIZE。代码如下:

#define SRAM0_PHYADDR 0x60000000

#define MEMDEV_SIZE 0x2000

驱动程序初始化,其关键任务主要有两个:完成驱动程序注册以及建立物理内存空间和内核内存空间的地址映射关系。初始化流程如图4所示,驱动程序首先通过调用register_chrdev_region函数向内核注册一字符型驱动程序。注册成功后,通过调用cdev_init函数实现注册访问双端口RAM芯片的文件访问接口。这里面包括了本文3.2节中指出的芯片读、芯片写、芯片打开、芯片释放以及片内地址定位等5个常用的文件访问接口。

图4 驱动程序初始化流程图

建立芯片内存地址到内核空间地址的映射关系,是Linux驱动程序最为关键的一步。首先,调用了kmalloc函数,在内核空间中申请一个设备结构体变量空间。该结构体主要用以记录双端口RAM的实际物理地址以及内核空间地址。第2步,使用request_ mem_region函数登记物理地址空间SRAM0_PHYADDR开始的2 kbyte空间被占用。最后,调用ioremap函数,建立物理地址空间到内核地址空间的映射关系。这样,驱动程序可以通过访问内核空间地址来实现对双端口RAM芯片物理地址的访问。

3 驱动程序测试

3.1 读写控制线时序的验证

为了验证驱动程序访问双端口RAM时序,实验采用示波器测试ARM芯片AM1808EMIFA接口上的片选信号(CS)和输出使能信号(OE)。图5所示,信道1为EMIFA片选信号,该信号为低有效。信道2为DRAM输出使能信号信号。在一次读操作中,由于AM1808总线工作在32 bit模式,而EMIFA配置成了16 bit异步模式,因此EMIFA需要完成2次读请求动作。因此图3中CS控制信号与OE信号分别依次输出2次有效信号。从读写访问周期上,单次16位读写周期为180 ns,符合2.1节中预期的设计要求。

图5 AM1808读操作控制线时序波形

3.2 连续读写性能测试

在3.1节访问控制时序正确的前提下,进一步进行双核通信连续读写测试。这里使用32通逻辑分析仪,如图 6所示,CH1~CH11分别挂接在AM1808与DRAM的数据总线上,CH17挂接在输出使能OE引脚上。采用测试逻辑是DSP先向DRAM 2 kbyte字节顺序写满20~210,由AM1808执行进行连续读请求。由图上可见数据总线能呈现出20~210的数据返回值。在2.1节中,由于当前驱动参数设置了一次读写周期为180 ns,图4下方时间坐标轴时间单位为μs,本次测试在35μs时间内完成了192次读操作,因此在该驱动参数下控制器双核通信带宽达到双向88 Mbit/s。这个通信带宽能完全满足正常控制采样数据的高速上传。

图6 逻辑分析仪记录AM1808连续读双端口RAM信号

4 结语

本文在嵌入式Linux系统之上采用双端口型高速RAM芯片CY7C024AV2开发控制器双核扩展模块及其驱动程序,实现了控制器ARM+DSP的双核通信架构,从而在原电源控制器基础上实现了网络接口的扩展。这将大大提高了控制器对于过程工艺控制开放性,为控制器互联及其物联网控制提供了硬件基础和软件基础。在示波器和逻辑分析仪的辅助下,本文所设计的驱动程序的正确性得到了验证,同时基于该驱动程序之上的双核通信模块也具备了较高的通信性能。

[1]郝小江.基于DSP逆变焊接电源数字控制[J].电焊机,2010,40(9):40-42.

[2]霍明.基于ARM控制的多功能数字化逆变焊接电源[J].焊接技术,2009,38(2):5-8.

[3]刘玉珍,张晔.双端口RAM在ARM与DSP通信系统中的应用[J].计算机系统应用,2011,20(11):213-216.

[4]安剑奇,廖丽清,温兴清.高速双端口共享存储器IDT7025及其应用[J].电子工艺技术,2006,27(5):291-293.

[5]朱欣华.多机系统中双口RAM的构成方法及应用[J].测控技术,2006,15(2):44-46.

[6]AM1808/AM1810 ARM Microprocessor Technical Reference Manual[M].Texas Instruments,December 2011.

[7]CY7C024AV Technical Reference Manual(Document38-06052)[S].Cypress Semiconductor Corporation,March 30,2011.

[8]TMS320F28335 Digital Signal Controllers(DSCs)Data Manual (Literature Number:SPRS439I)[M].Texas Instruments,March 2011.

[9]章坚武,许晓荣,李波.基于嵌入式Linux的双口异步RAM驱动开发[J].电子器件,2006,29(2):536-538.

[10]屈克文,石奋苏.基于ARM-Linux的旋转编码器接口与驱动程序的设计[J].计算机应用,2011,31(12S):156-163.

[11]Ju Jinwu,Cai Lecai,Luo Renjia.The Design of Linux Driver of WSN Nodes Based on ARM[C]//Intelligent Computation Tech-nology and Automation(ICICTA),2011 International Conference,Page(s):761-764.

[12]Liu Long,Zhang Yuncui.Improved Method of Computer Keyboard Driver Based on Embedded Linux[C]//Fuzzy Systems and Knowledge Discovery(FSKD),2012 9th International Conference,Page (s):2482-2486.

Driver Designed for Dual-Core Communication Module Based on Dual-Port RAM

PAN Bichao1,CAO Biao2*

(1.College of Information Engineering,Guangdong Ji Dian Polytechnic,Guangzhou 510515,China; 2.School of Mechanical and Automobile Engineering,South China University of Technology,Guangzhou 510640,China)

The flexibility of process control is greatly affected by the relatively closed hardware architecture and limited amount of control parameters.It is a trend to develop a smart controller with open hardware architecture which can make it possible of control process network.With the use of Dual-Port RAM CY7C024AV2,A dual-core solution with DSP and ARM is presented,as long as the driver development under embedded Linux for the dual-core controller module.The driver presented provided software basis for intelligent network controlmethods.Experiment result shows that the driver can achieve a good performance on inter-core communication.

embedded system;dual-core;internet of things;driver

10.3969/j.issn.1005-9490.2014.01.013

TP31 文献标识码:A 文章编号:1005-9490(2014)01-0050-05

2013-05-11修改日期:2013-06-12

EEACC:6210C

潘必超(1978-),男,汉族,广东惠州人,广东机电职业技术学院讲师/系统分析师,硕士,研究方向为数字化电源装备及智能控制技术,物联网应用技术,bcpan@126.com;

曹 彪(1963-),男,汉族,贵州盘县人,教授/博士生导师,研究方向为数字化电源设备及智能控制技术:高性能工业逆变电源的设计、计算机仿真与智能控制,电力电子技术,新型开关电源及应用技术。