基于FPGA的视频图像画面分割器设计

2014-09-26曹旭东王程锦孙云龙

曹旭东,王程锦,孙云龙

(中国石油大学(北京) 北京 102200)

随着计算机、DSP、超大规模集成电路等技术的发展,画面分割器开始采用硬件设计。首先,将各路视频信号转换成数字视频信号;然后,在数字领域对各路视频信号进行处理。使电路的设计、调试得到了很大的改善。但是,设计中所使用的独立的逻辑电路较多,有的甚至使用专用的DSP芯片去处理视频画面的分割。虽然可以满足对视频图像数据处理速度的要求,但是还需要外加CPU去协调系统工作,使得整个系统仍显得体积较大,而且系统成本较高。随着半导体加工工艺的不断发展,FPGA在结构、速度、工艺、集成度和性能方面都取得了很大的进步和提高。本文将详细介绍基于FPGA开发技术的视频图像画面分割器的软硬件设计与实现。

1 系统总体设计

本系统选用Altera公司的Cyclone III系列中的EP3C40F780C7型号FPGA作为核心处理芯片,提出和设计了一个多路视频图像数据的采集、处理、显示,实现视频图像画面分割器。

Cyclone III系列FPGA是Altera公司的低功耗、高性能和低成本的可编程逻辑器件,具有独特的低功耗体系结构,以非常低的成本提供丰富的存储器和专用乘法器资源。在视频和图像处理等高强度算法应用中,这些特性使该FPGA成为ASSP、ASIC以及分立数字信号处理器的理想替代方案。

1.1 硬件结构设计

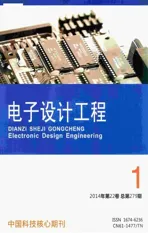

整个系统主要由DVI接口电路、DVI信号解码电路、FPGA及其配置电路、DDR2 SDRAM数据存储电路及DVI信号编码电路组成,系统结构框图如图1所示。

图1 视频图像画面分割器系统结构图Fig. 1 Block diagram for system design

从图1中可以看出,从DVI接口接收到DVI信号后通过解码芯片SiI1161进行解码,转换成并行的数字信号,然后进入FPGA对四路视频信号进行提取、存储、合成等功能,进行处理后的数据通过编码芯片SiI164再转换为DVI视频信号,就可以接到显示器上显示了。

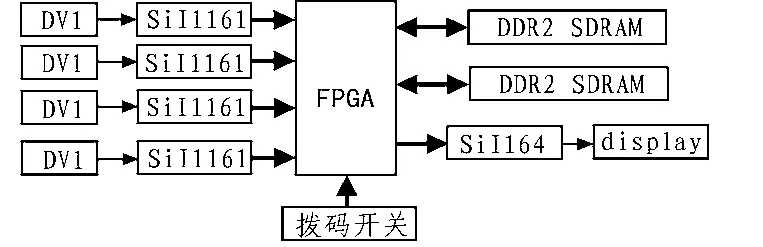

1.2 软件结构设计

系统的软件设计是系统功能实现的关键。在系统的硬件平台的基础上,通过对FPGA编程实现对视频解码芯片输出的实时数字视频数据接收,并根据画面合成需要,对有效视频图像数据进行提取和存储,然后将各路视频数据合成一路输出到显示器。系统实现功能的系统框图如图2所示。

图2 系统功能框图Fig. 2 System functional block diagram

以下重点介绍一下视频信号的提取和合成。

1.2.1 提取模块设计

1)图像提取原理

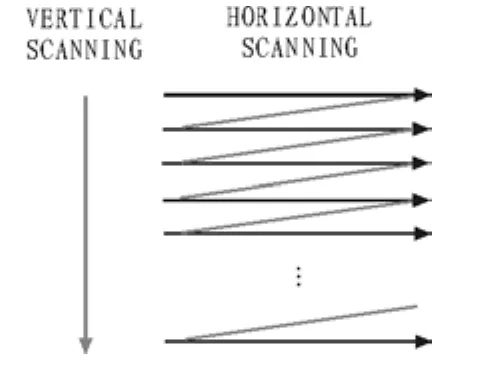

视频画面尽管看起来好像是连续运动的,其实那是一系列静止的图像,这些图像切换得足够快,使得画面看起来像是连续运动的,如图3所示。一种称为场同步(vertical sync)的特定时序信息被用于指定新图像从什么时候开始显示;每张静止图像是由扫描线(scan line)组成的,即沿着显示器从上到下、一行接着一行进行显示的数据线,另一种称为行同步(horizontal sync)的时序信息用于指定新扫描线什么时候开始显示。

图3 视频时序Fig. 3 Video timing

行同步和场同步信息通常通过以下3种方式之一进行传输:

①单独的行同步和场同步信号;

②单独的复合同步信号;

③嵌入视频信号的复合同步信号。

本系统采用的是数字视频,采用的是技术①。

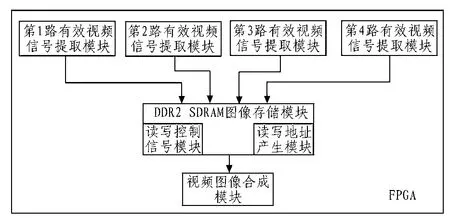

DV支持超过1 600×1 200的PC图形分辨率和包括720 p、1 080 i和1 080 p的HDTV分辨率,本设计采用的输入分辨率为1 280×720/60 Hz,像素时钟为74.25 MHz。DVI信号经SiI1161解码后得到带像素时钟的24位并行R、G、B数字信号及H、V、DE信号[8],它们之间的相互关系如图4所示。

图4 1280x720p @ 59.94/60 Hz的时序参数Fig. 4 Timing parameters for 1280x720p @ 59.94/60 Hz

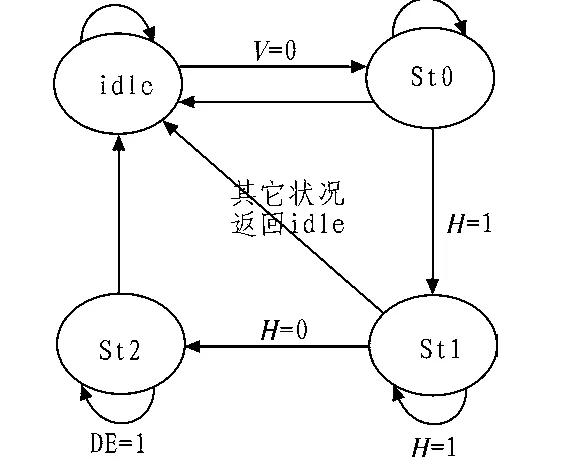

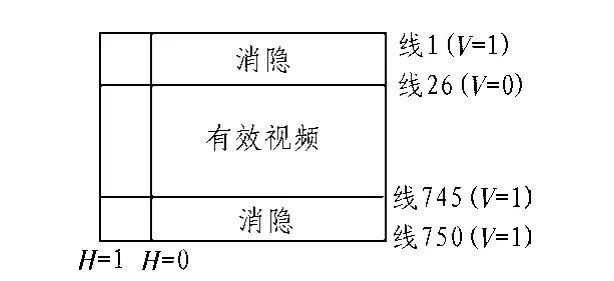

其中,当DE为1时,处理有效视频,当DE为0时,处理HSYNC和VSYNC信号。SiI1161输出的数字视频信号一帧由750行视频数据组成,每一场有效视频行为720行,每一行又有1 650个像素,其中有效像素有1 280个,这些是在视频图像合成过程中要用到的数据,每一个像素都包含R、G、B 3种信号。本设计根据H、V、DE信号对有效视频数据进行定位,并根据图像合成的需要把所需的有效视频数据提取出来。在实现的过程中利用状态机来判断有效视频数据,如图5所示。

图5 有效数据检测状态机Fig. 5 Effective data detection state machine

状态机缺省状态为idle状态。先在idle状态检测场信号由高变低,进入有效数据行,再判断H与DE的高低状态,进而检测到有效视频数据,当H由高变低,DE为高的这段视频数据则为有效视频数据。这样则可以根据视频图像合成的需要对视频数据进行选择提取。

2)图像提取模块设计

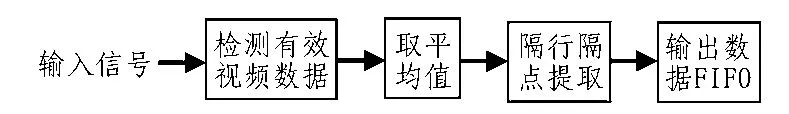

基于上述有效视频数据的提取原理可以提取任何一个数据行或任何一个象素,由于不同的图像合成需要提取的有效视频数是不同的。本设计为四画面分割,需要对每一路输入信号进行1/4压缩,即需要对有效数据进行隔行隔点提取。有效视频数据提取程序框图如图6所示。

图6 有效视频数据提取程序框图Fig. 6 Block diagram of the active video extract

由图可知:接收到输入信号后,根据视频数据提取原理,检测有效的视频数据,每来一个时钟,接收一个视频数据存储到RAM模块中;然后对RAM模块中存放的数据取平均值;接着对这些平均值隔行隔点提取,把提取出的数据送入异步FIFO中,方便读写入DDR2 SDRAM中。

隔行隔点提取有效数据就是要将一些像素丢弃,本设计采用邻域平均法来改善缩放后的视频图像质量。邻域平均法的原理是将原图中一个像素值和它周围邻近8个像素值相加,然后将求得的平均值(除以9)作为新图中该像素的值。它采用模板计算的思想,模板操作实现了一种邻域运算,即某个像素点的结果不仅与本像素有关,而且与其邻域点的像素值有关。邻域平均法的数学公式表达为:

其中f(i,j)为给定的图像,经过邻域平均处理后的图像为g(i,j),M是所取邻域中各邻近像素的坐标N是邻域中包含的邻近像素的个数。

1.2.2 图像合成和编码模块设计

1)图像合成原理

在像素域的多画面合成中,首先,对原图像按像素进行抽取,分别将多路图像按照一定的比例缩小。然后,按照一定的规则将多路图像进行排列,排列后的图像即为多路合成的图像。最后,将合成的图像编码输出,即可在同一个屏幕显示多个画面,完成对多路图像的合成。

合成后的视频图像是逐行显示的,而对于将图像以逐行方式“绘制”到屏幕上的设备,每张图像都是从显示器的左上角开始,一直向右移动,直到到达显示器的右边缘为止,然后向下扫描一行,重复地从左到右进行扫描,这个过程一直持续到整个屏幕全部被刷新一次为止,如图7所示。

图7 逐行显示Fig. 7 Progressive displays

SiI1161输出的完整的一帧图像数据结构如图8所示。

图8 1280x720p数字垂直时序(720有效线)Fig. 8 1280x720p digital vertical timing (720 active lines)

以四路为例,首先,要分别对原图像进行1/4比例缩小。一帧视频图像有效显示的图像数据为26~745行,则在垂直方向上隔行抽取有效视频行,使垂直方向缩小为原来的1/2。

在水平方向上,每行有效视频由1 280个像素组成,每隔一个像素抽取一个有效视频,使水平方向缩小为原来的1/2。这样经过垂直和水平方向的抽取所得到的图像缩小为原图像的1/4。

然后,按照一帧图像数据的排列格式对抽取的各路图像的像素进行排列。抽取的第一路图像的行与第二路图像的行组成一整行,第三路图像的行与第四路图像的行组成一整行,四路图像的行组成新的一帧图像的图像数据。

最后,将四路合成图像数据经过SiI164编码输出,通过逐行扫描在一个显示器上显示四路图像,即完成了四路视频图像合成。

2)图像合成模块设计

视频图像画面合成的实现方法主要分为两大类:像素域合成和压缩域合成。基于系统的图像数据为24位R、G、B数字视频格式,所以在视频图像画面合成中采用像素域内多画面合成的方法。四路视频图像合成的实现过程如下:

首先,分别在垂直方向和水平方向上抽取有效的视频数据,将四路图像各缩小为原图像的1/4。这部分功能由有效视频数据提取模块实现,该模块在前面已经做过详细介绍。然后,将提取的各路图像数据按找一定顺序排列,即按照一定的规律存储到DDR2 SDRAM中。各路图像数据的地址按照上一节介绍的地址产生方法实现,都有各自固定的存储空间。

图9 多路合成图像数据结构图Fig. 9 Multichannel synthetic image data chart

在完成各路视频图像的抽取,存储后,就要对抽取的各路视频图像的进行四画面合成。根据720P系统数字信号的数据格式,把有效视频数据从存储器中采用顺序读取出来,在相应的H、V、DE信号的位置,送视频编码输出,完成四路视频图像的合成。在合成的过程中,H、V、DE信号及时钟信号都由第一路输入的视频信号产生。四路视频合成图像的排列方式如图9所示。

2 调试结果

经过软硬件的综合调试,整个视频图像画面分割系统便可以正常工作了。

采集的多路视频图像经过FPGA图像合成处理后,可以在一个显示器显示多路视频图像。

3 结束语

文中采用FPGA开发技术实现了视频图像画面分割器的画面分割的功能。研究的主要特色在于构建了以FPGA为核心器件的视频画面分割的硬件平台,通过硬件形式来实现视频四画面分割,图像的提取、存储等都在一片FPGA内实现,提高了系统的集成度,所有的模块设计都是利用Verilog HDL编程实现,和软件实现方法相比,系统在处理速度方面有了显著的提高。输入/输出的信号都为DVI信号,实现了高清视频画面分割。

[1]姜建发.多画面分割器技术原理及探测方法探讨[M].福州:福建省广播影视集团,2009.

[2]黄智伟.FPGA系统设计与实现[M].北京:电子工业出版社,2005.

[3]杜建国.Verilog HDL 硬件描述语言[M].北京:国防工业出版社,2004.

[4]徐光辉,程东旭等.基于FPGA的嵌入式开发与应用[M].北京:电子工业出版社,2006.

[5]赵负图.信号采集与处理集成电路手册[M].北京:化学工业出版社,2002.

[6]李介谷.图像处理技术[M].上海:上海交通大学出版社, 1998.