一种用于亚微米多晶栅TiSi电阻优化的方法

2014-09-19王敏妲孙建洁陈海峰

王敏妲,孙建洁,陈海峰

(1.江南大学物联网学院,江苏 无锡 214035;2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着半导体技术的不断发展,电路规模不断扩大,器件特征尺寸不断减小,使得互联线电阻对电路性能的影响越来越重要。重掺杂的多晶硅由于自身杂质固溶度的限制,使得RC延时变长从而限制了特征尺寸的进一步减小。为了克服这一限制,发展了低电阻率的硅化物工艺[1]。CMOS超大规模集成电路的关键就是降低源漏区与栅电极的寄生电阻,而自对准硅化钛工艺可以在有效降低电阻的同时保存基本的多晶硅栅MOS结构[2]。

但是在实际半导体工艺流程中,由于受到光刻设备工艺能力的限制,0.6 μm及以下工艺的多晶栅条上套刻精度无法保证。这导致了后续源漏注入剂量在多晶栅上有所偏差,工艺容宽较小,影响了后续TiSi在多晶栅上的生长,从而导致多晶栅电阻异常。本文通过在多晶栅上增加一层SiN掩蔽层的方法,不改变原有源漏注入剂量,使多晶栅的掺杂剂量稳定,保证了后续TiSi生长,得到稳定而较低的多晶栅电阻。

2 实验

首先,对现有的多晶栅TiSi工艺进行一个简单的介绍。

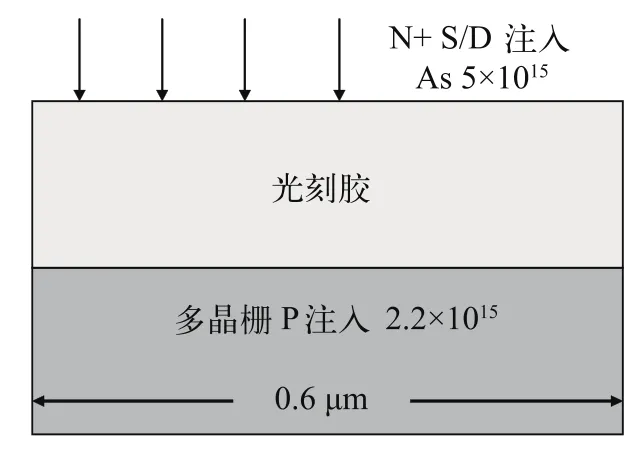

图1 现有多晶栅工艺时N+S/D注入

由图1所示,多晶栅为P注入2.2×1015的注入重掺杂,N+S/D注入光刻时需要对多晶栅进行完全的遮掩,但是由于该种多晶栅条为单独存在的单元细条,目前在线光刻机工艺能力较弱,无法保证套刻精度要求,可能会存在部分区域的裸露,导致N+S/D注入进入到多晶栅中,导致多晶栅形成表面重掺杂。由理论得知,TiSi的生长与衬底的掺杂浓度相关,特别是界面处浓度,掺杂浓度越大,TiSi的生长越困难,甚至可能导致无法生长。

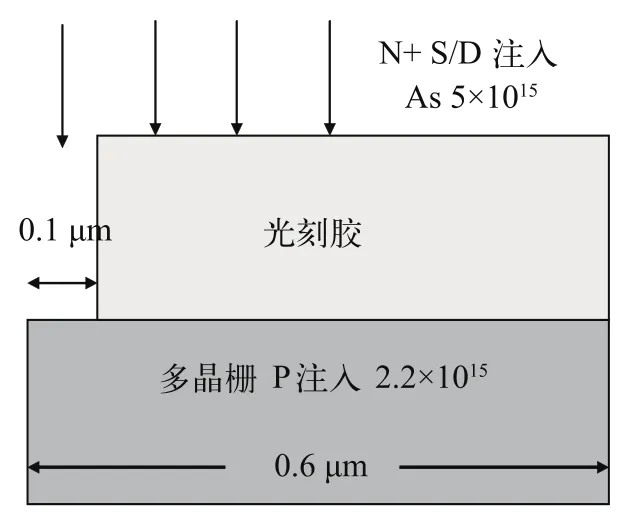

图2 N+S/D注入光刻有0.1 μm套刻偏差

图3 N+S/D注入光刻有0.2 μm套刻偏差

由图2所示,当源漏注入As时,光刻套刻偏差较好,光刻的套刻偏差为0.1 μm,多晶栅条宽为0.6 μm,假设注入没有发生偏差,7°角注入,注入的杂质总量为:P 2.2×1015+ As 0.83×1015(1/6×5×Sin83=0.83),多注入0.83×1015;由图3所示,当源漏注入As时,光刻套刻偏差较差,光刻的套刻偏差为0.2 μm,多晶栅条宽为0.6 μm,假设注入没有发生偏差,7°角注入,注入的杂质总量为:P 2.2×1015+As 1.65×1015(2/6×5×Sin83=0.83),多注入1.65×1015。由此得知,不计入注入剂量的偏差,单单是光刻套刻偏差所引起的掺杂剂量就可以达到×1015级,这对后续TiSi在多晶栅上的生长是致命的。

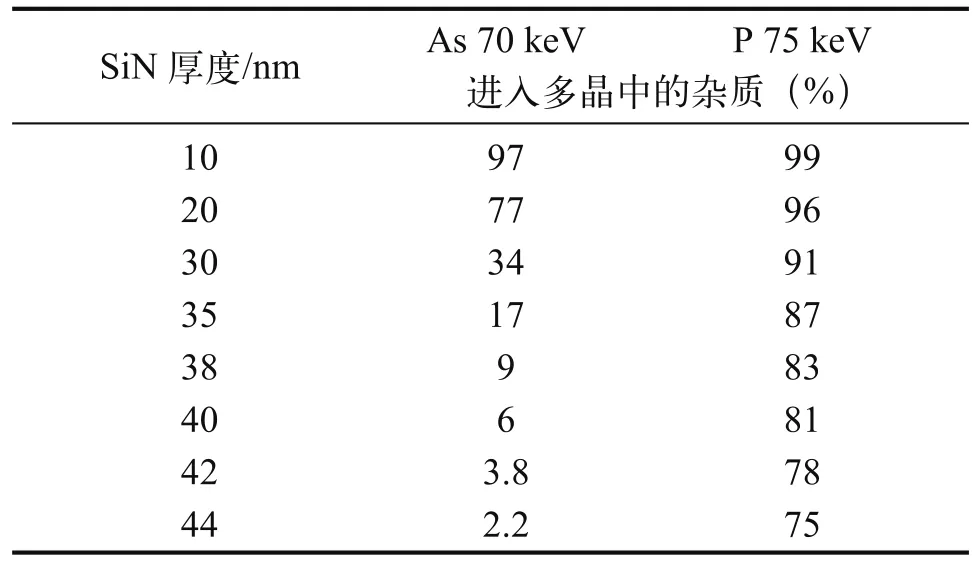

由于该步骤的光刻受到设备硬件的限制,无法从光刻改进,需要寻找其他步骤来避免N+S/D注入对多晶栅的影响。本文采用掩蔽层来防止N+S/D注入。作为掩蔽层材料,LPCVD SiN和热氧SiO2是最为常见的2种。这里选择LPCVD SiN作为掩蔽层。由于LPCVD SiN对多晶有较高的腐蚀选择比,后续可以使用湿法腐蚀,这样就大大降低了优化的成本。由于该掩蔽层在多晶后直接生长,会对后续的多晶栅注入进行一定的阻挡,因此必须选择一个合理的厚度。如表1所示,根据注入机注入原理和仿真[3],在达到40 nm左右基本可以阻挡95%的N+S/D As注入剂量而保留80%的多晶栅P注入剂量。因此选择40 nm LPCVD SiN作为最终的掩蔽层,并且在源漏注入后利用湿法腐蚀去除。

表1 As注入和P注入在不同SiN厚度掩蔽层下的穿透率

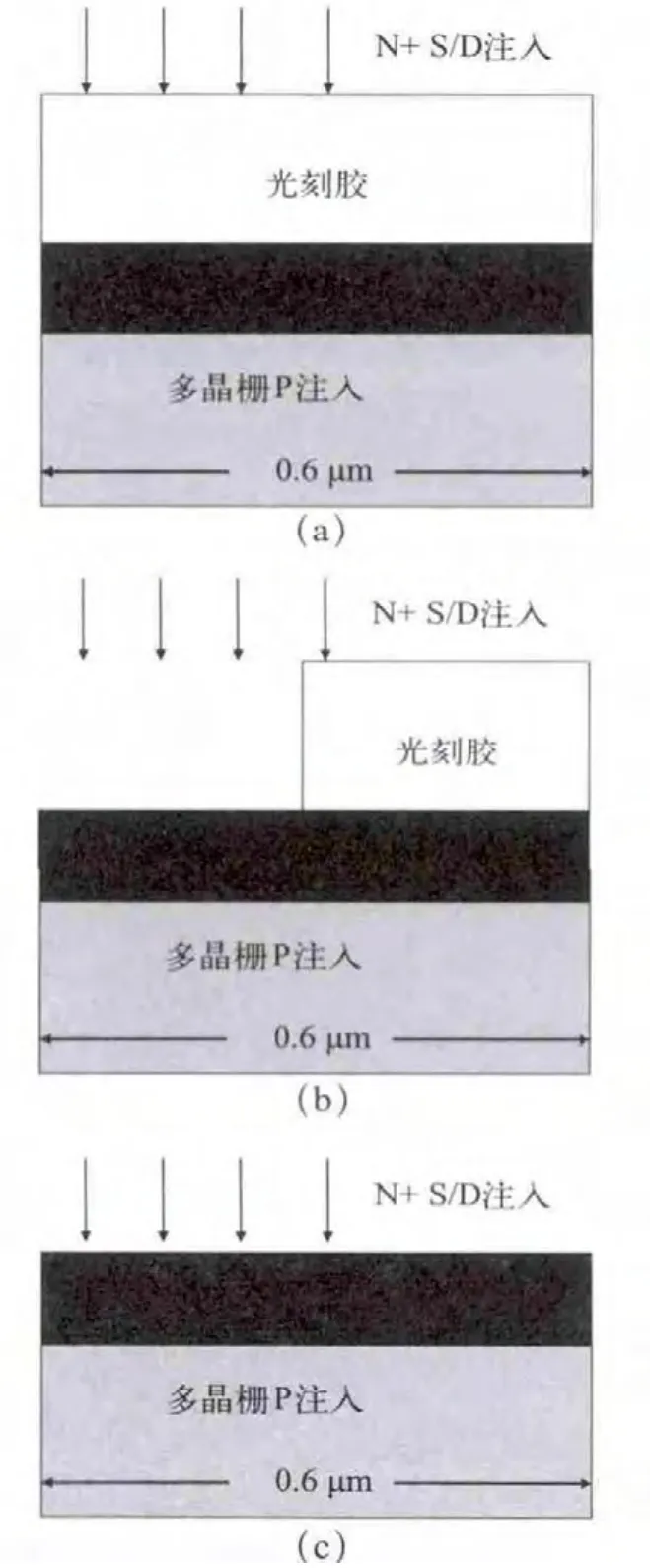

图4 实验设计的3种不同结构的N+S/D注入情况

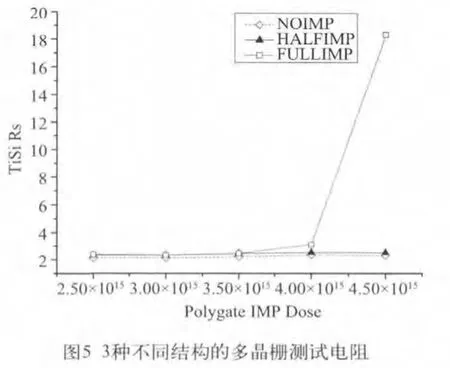

实验设计如图4所示,在PCM测试区存在3个多晶栅电阻测试区域,(a)为N+S/D注入时多晶栅完全被光刻胶挡住,N+S/D不注入到多晶栅区域;(b)为N+S/D注入时多晶栅一半被光刻胶挡住,N+S/D半注入到多晶栅区域;(c)为N+S/D注入时多晶栅完全裸露,N+S/D全注入到多晶栅区域。此外,我们也对多晶栅注入的剂量进行了拉偏,从2.5×1015~4.5×1015分为5步,观察增加掩蔽层后多晶栅注入剂量对后续TiSi生长的影响。

3 实验结果与分析

实验结果如图5所示,(a)、(b)、(c)三种情况下多晶栅测试电阻表明,增加了40 nm LPCVD SiN掩蔽层后,只要多晶栅注入的剂量不超过4×1015,N+S/D注入剂量的影响可以忽略不计,不会对后续TiSi的生长产生影响,并且多晶栅注入的剂量从2.5×1015~4×1015都是可以接受的,多晶栅注入的工艺容宽变得很大。

4 总结

本文通过在多晶栅上增加一层LPCVD SiN掩蔽层,避免了由于N+S/D注入时光刻套刻偏差引入的注入剂量偏差,从而削弱了多晶栅界面的重掺杂影响,使得后续多晶栅上TiSi的生长更好更稳定。利用该种掩蔽层的方法,优点有3点:

(1)LPCVD SiN对多晶有较高的选择比,后续可以使用湿法腐蚀,成本较低;(2)源漏注入的条件不用更改;(3)多晶栅注入的可调节剂量范围可以大大增加,可以更好地保持重掺杂多晶栅特性。

当然,由于工艺更改,该种方法也导致了一些其他问题:

(1)多晶上增加了LPCVD SiN掩蔽层,多晶光刻需要考虑顶部抗反射层;

(2)湿法腐蚀去LPCVD SiN后发现多晶栅表面有零星圈状缺陷出现,需要湿法进行工艺优化。这些问题需要在后续的工艺开发中继续优化。

[1]王大海,万春明,徐秋霞.自对准硅化物工艺研究[J].微电子学,2004,34(6).

[2]Ng K-K,Lynch W-T.Analysis of the gate-voltagedependent series resistance on MOSFET’s [J].IEEE Trans Elec,1986,33(7):965-972.

[3]EATON NV-1080 SYSTEM AND & OPERATION[Z].