模拟电子开关阵列的测试系统设计

2014-09-06,

,

(中国空空导弹研究院,河南 洛阳 471009)

模拟电子开关阵列的测试系统设计

孙龙涛,赵月琴

(中国空空导弹研究院,河南 洛阳 471009)

0 引言

电子系统中,超过20%的系统故障是由线缆的失效引起的[1],日常生产和维护中,对其检测是人工通过万用表对照接线表进行逐点导通测量,该方法落后,且存在着工作量大、效率低、易出错和测试不能详尽等问题。若直接外购通用的线缆测试设备,其功能虽然能够满足测试需求,但其价格昂贵,而且通常这种仪器有许多功能不能充分利用,从而造成资源的浪费。基于上述原因,设计了一种小型、便携和经济的线缆测试系统。它不仅可以测出线缆组件中任意两个端点之间的阻值,根据接线表判断出错连和漏连,而且可以检测出线缆组件中连接的继电器的故障情况。

1 测试方案设计

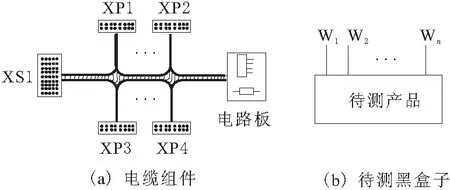

某电子设备电缆组件示意如图1a所示,图中XS1、XP1~XP4电连接器共有n个连接端点,这n个端点之间的连接关系均为直通线或者是通过功率电阻连接,本测试系统的任务就是测试XS1、XP1~XP4之间及其与电路板之间连接关系,并将其中的漏连和误连检测出来。可将图1a所示的待测电缆组件看作成如图1b所示的具有若干端点的待测黑盒子,黑盒子有n个线缆连接端子,用W1~Wn表示,黑盒子内部为直通线、功率电阻或是继电器。

图1 待测产品示意

线缆测试系统的测试原理电路图如图2所示。设图1b中所示的2个端点Wi和Wj之间的电阻为Rx,根据欧姆定律,只要测试出R0上的电压值,就可计算出Rx值。测试过程首先要选中这两个端点,在端点Wi处施加+5V的基准电压,然后采集端点Wj处的输出电压值,然后根据设定的通断判据,就可判断Wi和Wj之间的连接状态。如判据可设定Rx值小于5Ω,则认为Wi和Wj之间为短路,如Rx值大于80kΩ,则认为Wi和Wj之间为开路。如果测得阻值在5~80Ω之间,则直接在显示屏中显示这2个端点之间的阻值。对于图1a中继电器的检测则是在继电器的输入端施加一个激励,在输出端检测是否导通,检测方法与其它端点相同。

图2 任意两端点间通断关系测试原理

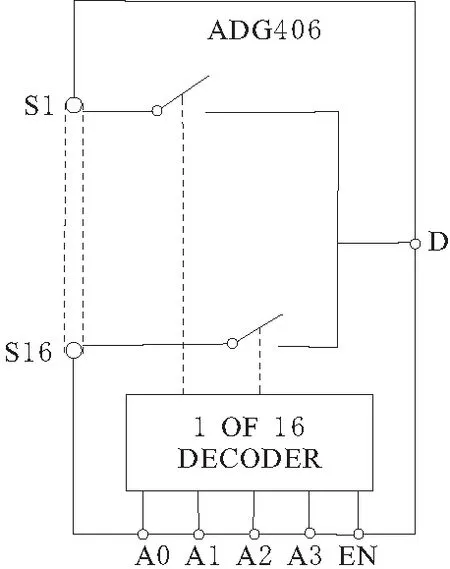

图3 ADG406原理电路

根据图2的测试原理,要完成几百个端点中任意一点Wi与所有其它端点的导通状态测试,需要每个端点在测试过程中必须是既可以作为输入端点又可以作为输出端点,即每个端点在不同的时刻既能连接到基准5V,又能连接到采集点,这就需要设计开关阵列电路和扫描控制电路。本设计拟采用16选1模拟电子开关器件作为线缆端点选择阵列的基本器件。模拟电子开关选用的是AD公司生产ADG406,ADG406的电路原理如图3所示。它可采用单电源供电或双电源供电,采用双电源供电时,其导通电阻一般为50Ω,最大为80Ω。设计中采用双电源供电模式,供电电压为±15V。EN为ADG406的片选信号,A0~A3为16路开关的地址选通信号,根据通道选通信号A0~A3值的不同,内部译码电路通过译码可使S1~S16中的其中一个端点与端点D接通。

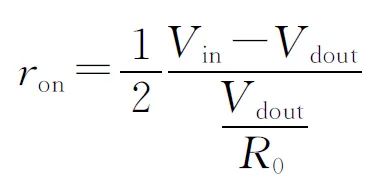

根据以上测试方案可以推导出图2的两个端点之间的电阻为:

(1)

R0为电路中接入的已知电阻,Vin和Vdout都由CPU模块通过AD采集卡采集得到。ron为模拟电子开关的通道导通电阻,由于模拟电子开关的导通电阻一般为几十欧姆,所以在计算端点之间电阻时不能忽略该导通电阻。ron模拟电子开关导通时的导通电阻。ron的大小要在实验中通过测试数据计算。

2 测试系统设计实现

2.1 系统组成

测试系统硬件平台包括:PC/104主机板、接口板、AD采集卡、端点选择阵列电路板、测试电缆、键盘和显示屏等,如图4所示。硬件电路除须自行设计线缆端点选择阵列电路和I/O扩展板卡外,其它采用市场上的货架产品。主CPU模块采用X86兼容的处理器,最高运行速度可以达到300MHz,它通过PC/104总线和接口板、AD采集卡连接。AD采集卡具有16路模拟信号采集通道,设置为单极性,每个通道的输入电压范围为0~5V,采集精度12位。主CPU模块上有显示器接口和键盘接口,用于系统软件开发和产品调试。

图4 系统组成

2.2 端点选择开关阵列电路设计

由多个ADG406器件组成的开关阵列电路如图5所示。这些电子开关被分为2组,从U1到Um为一组,称它为U阵列,从D1到Dm为另一组,称它为D阵列。这里m的值取决于待测产品的端点数n。2组模拟电子开关组成了2个n选1的阵列电路,U阵列用于从待测产品的n个端点中选择一个端点作为输入端点,并将该端点施加+5V测试基准电压,而D阵列用于从待测产品的n个端点中选择一个端点指定为输出端点,并将该端点经过一个电阻接地。测试系统中的端点数约为288个,所以共需要288×2=576路开关,需要的ADG406器件数至少为576÷16=36片,考虑设计余量,测试使用了40片ADG406,也即40片ADG406组成了2个320选1开关。640路开关的通断由计算机扫描控制电路控制,每一片ADG406的16个开关需要5个I/O控制信号来选择其中一个开关,则该2组开关阵列需要40×5=200路I/O控制电路,由于计算机I/O空间有限,需要通过计算机I/O扩展板卡完成控制。系统设计了基于CPLD的PC/104 I/O扩展板卡,在嵌入式工控机的控制下,I/O扩展板卡输出U阵列和D阵列的片选信号和片内通道地址选通信号,使U阵列和D阵列各有一个且仅有一个开关闭合,就形成图2示的测试电路。这样当按照一定的排列组合方式依次闭合U阵列中模拟开关,再依次闭合D阵列模拟开关,并采集和处理输出数据,即可判断所有端点间的通断状态。

图5 线缆通断检测实现原理

2.3 基于CPLD的I/O扩展板卡设计

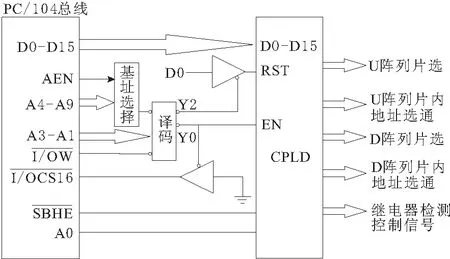

I/O扩展板用于端点选通开关阵列电路板的选通和关断控制,在主机板的控制下实现对线缆端点的扫描控制。CPU通过对外部I/O写操作,产生选通I/O信号和控制继电器检测的I/O控制信号。PC/104 I/O扩展板电路原理如图6所示。

PC/104嵌入式系统支持的端口数目是1024个,其中部分端口被系统占用。为了防止设计接口板时选用的端口地址与PC/104主板已经占用的地址冲突,采用了板卡地址用户可设置的设计方法[2]。将一个拨码开关和一个数据比较器组成一个基地址选择电路,通过设置拨码开关就可以修改接口板的地址,以提高系统的可扩展性。

图6 PC/104总线接口电路

接口电路中CPLD将总线送来的数据经过锁存、匹配及译码后,转换为控制电子开关阵列导通的控制信号,其另外一个功能是产生控制继电器检测的I/O控制信号。

3 测试系统的软件设计

根据课题要求,测试系统应具有很好的实时性和友好的人机界面,QNX操作系统实时性好且人机交互界面开发设计简单,另外测试系统在进行线缆通断的检测过程中需要进行大量的I/O操作,QNX操作系统下I/O操作速度非常快,可缩短系统的测试速度[3],故本设计选用QNX操作系统。测试系统应用软件设计在QNX操作系统平台和其开发工具PhAB(photon application builder)环境下使用C语言完成。应用软件设计主要是人机交互界面和测试控制程序设计。系统软件设计主要功能如下:

a.手动输入接线表功能,在进行线缆通断关系检测前,必须要有待检产品的转接线表和接线表,需要用户在测试前能够通过人机交互界面手动输入。

b.接线表自动生成功能,通过软件对完好的产品进行测试后,将测试结果生成接线表并存储,作为同型号中待测产品的测试基准。

c.端点扫描控制程序,按照设定流程逐次扫描各个端点,完成系统的测试控制。

d.测试完成,显示错误的连线及位置信息。

4 测试系统主要性能分析

4.1 电子开关阻抗测试

ron的确定方法如下,当第i个端点和第j个端点用短导线直接连通,则Rij的值应该近似为零,这时,式(1)变为:

则

(2)

根据式(2)可以测出每一路电子开关闭合时的实际阻抗值,将这个阻抗值以矩阵的形式储存,作为式(1)计算Rij的值一个重要参数。

4.2 线缆通断阻抗测试精度分析

由于线缆通断的检测原理是根据检测到的电压值计算两个端点之间的电阻大小,从而判断两者之间的连接关系。因此,电阻测试精度直接影响着线缆通断的判断。系统电阻测试精度受电子开关的导通电阻、AD采集精度、被测电阻阻值大小以及计算误差等因素的影响。在测量小阻值的电阻时,影响系统测试精度的主要因素是模拟电子开关自身的导通电阻,原因是模拟开关导通电阻受到自身特性差异以及环境和温度的影响较大。实验数据表明,常温下在对阻值小于10Ω的电阻进行测试时,如果模拟电子开关导通电阻取固定值,则系统电阻测量偏差在3Ω以内。此时AD采集卡引起的模拟信号采集误差在毫伏级,与模拟开关的导通电阻引起的误差相比小得多,可以忽略不计。随着电阻的增大,影响系统测量精度的主要因素转变为AD采集的量化误差,电阻越大,测量误差越大,这个结论与理论分析基本是一致的。实验选取了不同规格电阻来测试系统的测量精度,统计数据表明,1kΩ以下电阻测量误差在5Ω以内,当电阻大于10kΩ时,测量误差将达到几千欧姆,且电阻越大误差越大。

在测量小阻值的电阻时,为了减小模拟开关导通电阻对测试精度的影响,系统采取自校准设计,即每次测量前记录当时所有通道的导通电阻,通过计算测试值和校准值之间的差值得到各个端点间电阻值,尽可能的减小不同环境因素造成的测试精度偏差,提高了测试的准确度。试验表明,采用自校准设计后线缆通断检测的测试精度可以达到1Ω以内。系统主要针对线缆的通断关系测试,所以对大阻值电阻的测试精度要求不高,只要设置好相应的判断临界值,即能正确判断出线缆的连接关系。结果表明,系统测试精度满足线缆通断判断的测试要求。

4.3 系统测试时间分析

系统测试时间的长短取决于端点扫描次数、CPU的I/O操作时间、AD采集时间、阻值计算时间和结果显示时间。测试过程中线缆通断检测需要进行大量的I/O端口操作和AD采集操作,为此通过实验分别测试了在QNX操作系统下进行一次I/O操作和一次AD采集的时间。经过实验测量计算得出一次I/O操作的时间为3.8μs,一次AD采集的时间为0.348ms,由于AD采集采用的是扫描法,应用程序中的一条AD采集语句,对AD采集卡而言,实际完成的是对其16个通道的采集。因此,每个AD通道采集时间为0.348ms/16通道,即21.7 μs,与AD采集卡给出的每个通道采集时间20μs的硬件指标基本吻合。

5 结束语

采用PC/104嵌入式工控机和QNX嵌入式操作系统的软硬件平台,设计一种小型、便携和经济实用的线缆测试系统。系统运用了模拟电子开关的双向导通性完成了端点选择阵列电路设计,替代了电磁继电器阵列电路,提高了系统的可靠性。通过实测,端点数目为288个的线缆组件,测试时间约需2min,对阻抗在5Ω与1kΩ之间的连线测试精度在3Ω以内,但阻抗在5Ω以下1kΩ以上的连接线的测量精度较差,由于电缆组件的故障模式绝大多数情况下为漏连(断路)和误连(短路),所以该测试系统能满足大多数实际应用。对精度要求较高的应用场合,需要对该测试系统进一步研究和设计完善。

[1] 周恒.基于ATmega128单片机的线缆检测系统设计[D].武汉:武汉科技大学,2008.

[2] 程良明.基于FPGA的电路板光板测试机硬件设计与样机研制[D].武汉:湖北工业大学.2005.

[3] 殷代宗.基于QNX实时操作系统的嵌入式测试系统的开发[D].西安:西北工业大学,2007.

Design of Testing System Based on Electronic Switch Matrix Circuit

SUNLongtao,ZHAOYueqin

(China Air-to-Air Missile Academy,Luoyang 471009,China)

市场上的线缆测试仪大多采用电磁继电器阵列,功能强大,价格昂贵。以PC/104嵌入式工控机和QNX嵌入式操作系统为核心,采用模拟电子开关式线缆端点选择阵列和基于可编程逻辑器件(CPLD)的线缆端点扫描控制电路,设计实现了一种小型、经济实用的线缆组件自动测试系统。最后对测试系统进行了试验验证,并对其主要性能参数进行了分析。

线缆测试;PC/104 CPLD;模拟电子开关阵列;QNX

This paper introduces a small-scale,economical automatic cable testing system.The design chooses embedded industrial computer PC/104 as a platform,and selects QNX as operating system.The design adopts CPLD to design interface circuit.Useing the bidirectional conduction characteristic of electronic switch,the design achieves the goal of slecting endpoint.Finally,the main test parameters of system are analyzed.

cable testing;PC/104 CPLD;matrix circuit;QNX

2014-04-09

TP277

A

1001-2257(2014)08-0062-04

孙龙涛(1979-),男,河南洛阳人,工程师,研究方向为导弹发射控制技术。