基于FPGA的色彩空间双向转换电路设计

2014-09-06张杰,高博,龚敏,刘兵,陈昶

张 杰,高 博,龚 敏,刘 兵,陈 昶

(四川省微电子技术重点实验室,成都 610064)

基于FPGA的色彩空间双向转换电路设计

张 杰,高 博,龚 敏*,刘 兵,陈 昶

(四川省微电子技术重点实验室,成都 610064)

RGB和YUV色彩空间的转换电路广泛应用于视频、图像的压缩和传输中。为减小RGB和YUV色彩空间转换电路的芯片面积,通过采用可编程逻辑器件中嵌入的PLL(Phase Locked Loop)和流水线算法,复用矩阵乘法器结构,只需单一模块电路便可以实现RGB和YUV色彩空间的双向转换。结果表明电路设计只需3个乘法器和3个加法器,最大工作频率达到105.89 MHz。因此,该设计在满足高清数据传输的情况下,大幅节省了芯片面积。

FPGA;色彩空间转换;矩阵乘法器;PLL

终端上的视频和图像显示通常采用RGB格式,但RGB格式的视频和图像储存量消耗较大,因而在传输过程中通常采用YUV格式。随着用户对高清数据传输速度的要求越来越高,RGB与YUV色彩空间的转换也需要满足高速的要求。

传统的软件转换方法由于计算量过于庞大,转换速度缓慢从而达不到高速转换的要求。硬件转换相对于软件转换具有速度快、转换效率高等优点,同时便于批量生产[1]。目前的转换电路都只是实现RGB到YUV或者YUV到RGB的单向转换[3-7]。但大多数情况下RGB到YUV的转换和YUV到RGB的转换不会同时进行,因此可以考虑将两种功能集成在一块模块上实现,再通过复用矩阵乘法器结构,满足高清数据传输速率的前提下,使芯片面积节省3~4倍。

1 RGB与YUV转换的电路设计

1.1 RGB与YUV转换的实现方法

RGB与YUV色彩空间之间的对应关系如下[2]:

(1)

(2)

方程组(1)为RGB到YUV色彩空间的转换,方程组(2)为YUV到RGB色彩空间的转换。

目前大多数采用软件实现的方法,如使用Intel单指令多数据扩展指令集SSE2技术进行转换[3];基于VC++的YUV和RGB之间的格式转换[4]等。软件实现计算量庞大,转换速度受到严重限制。

为提高速度,部分学者采用硬件实现的方法[5-6],不过发展缓慢。做得比较好的有采用CSD码和Wallace树优化转换电路[7];在高基乘法基础上,建立参数化高基乘法算法模型从而优化电路[8];采用查找表法[9]实现快速转换的目的。但这些方法消耗的乘法器和加法器数目较多,占用芯片面积较大。

目前的转换电路只能实现YUV到RGB或者RGB到YUV的单向转换,要实现双向转换需要两个独立模块。但观察方程组(1)、方程组(2)可以发现,两种转换都可以等效为一个3×3矩阵与一个3×1矩阵的乘法运算,因此可以采用同一个模块来实现两种转换。通过复用乘法器,每一个方程式中的3次乘法运算只需使用一个乘法器,从而大幅减少转换电路的芯片面积。

1.2 RGB与YUV双向转换实现原理

方程组(1)和方程组(2)可以等效为如式(3)所示的两个矩阵的乘法运算。方程组(3)又可表示为式(4)所示。

(3)

(4)

通过在时序空间复用1个乘法器和1个加法器[10],可以得到Y的正确结果;通过并行3个与上面相同的电路结构,可以实现RGB到YUV的转换;通过选择固化参数a1~a9,可以实现YUV与RGB的双向转换。为保证传输速率,矩阵乘法器的内部频率必须是系统时钟频率的3倍。这可以通过FPGA中的PLL倍频来实现。

1.3 基于PLL的双向转换电路设计

锁相环路是一种反馈控制电路,简称锁相环(PLL)。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。锁相环可以将外部的输入信号分频或者倍频,利用这个特点,在保持系统时钟频率不变的情况下,提高模块内部的频率,从而提高传输速率,增加硬件资源复用率,减小芯片面积。

采用FPGA中的PLL模块,转换电路的结构如图1所示。

图1 通过倍频电路改进后的RGB与YUV的双向转换电路结构图

a1~a9,b1~b9采用定点数设计,参数采用12位,最高位为符号位,第8位为小数位。在选择器控制下,当参数固化为a1~a9时,电路进行RGB到YUV空间的转换;当参数固化为b1~b9时,电路进行YUV到RGB空间的转换。采用FPGA的RGB到YUV空间转换电路工作原理如下:

3Xclk是一个3倍系统时钟频率信号,通过它实现外部一次计算操作,内部乘法器3次计算操作。图像数据R、G、B采用并行输入,通过计数器Cntr选择循环输入R、G、B值。图像数据的同步输入和矩阵运算参数的加载由Cntr计数器控制。结合计数控制器Cntr1和Cntr2以及寄存器单元,完成加法器的累加功能,并更新Y、U、V的输出值。

1.4 设计仿真与实现

由于电路设计在FPGA中实现,但方程组(1)和方程组(2)中的系数均为小数,因此需要采用定点数设计。在Verilog-HDL环境中,将方程组(1)和方程组(2)中系数同乘2M得到近似的整数,其中M为放大因子,M值的取值大小将在下面讨论。当方程组(1)和方程组(2)中的乘法和加法运算结束后,同除2M-1,采用尾位加1法,最终得到四舍五入近似的转换结果。

1.4.1 放大因子的选择

方程组(1)和方程组(2)中系数的放大倍数取决于具体的设计精度要求。由于Y、U、V的取值为整数,因此定义误差阈值为1.0。如果计算结果在误差阈值范围内,则表明计算结果在允许的误差范围,否则将会产生错误的结果。

放大比例因子M与计算精度密切相关,M如果取得太小,会出现颜色失真;M如果取得太大,将会超出人眼的区别范围,并影响频率特性等性能指标。通过以上分析,计算结果的误差与放大比例因子M密切有关。

以RGB到YUV色彩空间的转换为例,其中Y的理论绝对误差的计算公式如下:

(5)

其中abs{·}是取绝对值函数,int{·}是取整函数,round{·,0}表示四舍五入后的取整函数。其中R、G、B为整数,取值范围为0~255。

分析式(5)可知,当R、G、B均为最大值255时,Y的理论绝对误差达到最大值。同理,可以得到U、V的最大理论绝对误差值。表1给出了M为6、7、8、9、10时,Y、U、V的最大理论绝对误差结果。

表1 不同放大比例因子的Y、U、V的最大理论绝对误差值列表

设计中,选取M=9。R、G、B的理论最大绝对误差分别为0.727、0.628、0.659,均小于阈值误差1.0。

1.4.2 输出结果四舍五入的实现

在FPGA中,所有的数据都采用二进制来运算。当选择放大因子M=9后,输出结果近似为理论结果的29倍。如果此时直接将结果同除29进行截位操作,误差会很大。例如理论结果为27.8,直接截位后结果为27,导致产生0.8的误差。

如果将放大后的输出结果先同除28后,再将二进制最低位加1,然后将结果同除21可以大幅减小误差,实现输出结果的四舍五入。这种方法称为尾位加1法。例如理论结果为27.8,二进制尾位加1后结果为28.3,再截位得到四舍五入的输出结果28,误差只有0.2。

2 系统综合与仿真

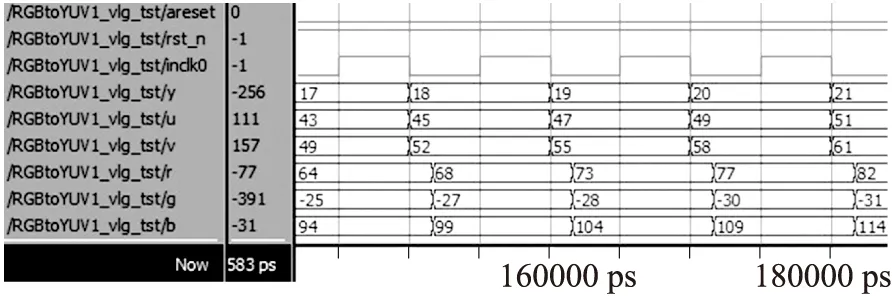

文章使用的是Altera公司的StratixⅡGX中的EP2SGX30DF780C3芯片。当参数固化在a1~a9存储单元中时,电路进行RGB空间到YUV空间的转换,Verilog源代码在Altera开发环境QuartusⅡ 9.0中综合并经过ModelSim后仿真,得到时序波形如图2所示。

图2 RGB到YUV空间电路时序仿真波形

图2中areset为PLL中异步复位信号,低电平时PLL正常工作;对PLL设置中,输入系统时钟inclk0为系100 MHz,输出时钟clk0为300 MHz;rst_n为电路内部复位信号,低电平有效。r、g、b为输入,y、u、v为输出并且延时2个系统时钟周期。后仿真结果如图3所示。以r、g、b分别等于26、53、26为例,对应的y、u、v的理论值为41.849、-7.803、-13.905,改进后的电路仿真结果为42、-8、-14,y、u、v的误差分别为0.151、0.197、0.095。通过多组验证,输出信号y、u、v是正确的。

图3 YUV到RGB空间电路时序仿真波形

当选择器将参数固化在b1~b9时,电路将进行YUV到RGB空间的转换,时钟环境不变下后仿真的波形如图3所示。

图3中的端口定义和图2中相同。以y、u、v分别等于17、43、49为例,对应的r、g、b的理论值为72.86、-28.454、104.376,改进后的电路仿真结果r、g、b为73、-28、104,误差分别为0.14、0.454、0.376。通过多组验证,输出信号r、g、b是正确的。

只需简单控制选择器的数据输入,便可以实现YUV和RGB色彩空间的双向转换,并且将加法器和乘法器数目均减为3个。与文献5和文献6对比,该设计乘法器和加法器数目都得到减少。

电路源代码在Quartus Ⅱ 9.0中进行综合,观察图2和图3的时间轴可知,系统时钟inclk0的周期为10000 ps,因此系统此时的工作频率为100 MHz。设计的实现平台使用Altera公司Stratix Ⅱ GX系列的EP2SGX30DF780C3芯片,综合布线工具使用Quartus Ⅱ 9.0,布线后通过时序分析所得时间性能分析报告总结的时序分析报告如表2所示,矩阵乘法器子系统的最大工作频率达到317.66 MHz,因此系统的最大工作频率达到105.89 MHz,流水线的工作模式使其满足高清数据传输速率的要求。

表2 时序分析报告结果 单位:ns

3 结论

文章利用FPGA中的PLL模块的倍频功能,设计行列矩阵乘法器,通过尾位加1法实现四舍五入的数据输出,完成了RGB与YUV色彩空间之间的双向转换,该系统的最大工作频率达到105.89 MHz,完全符合高清视频信号74.25 MHz的传输速率要求,乘法器和加法器数目分别减为3个和3个,减少了硬件占用资源,节省了芯片面积。通过FPGA电路的综合和仿真验证了该设计方案的正确性。

[1]章惠. 色彩空间转换的理论和实证研究综述[J]. 包装工程,2011,32(13):102-107.

[2]何斌,马天予,王运坚. Visual C++数字图像处理[M]. 北京:人民邮电出版社,2001:4-8.

[3]刘云粼,王树东. 基于SSE2的YUV与RGB色彩空间转换[J]. 中国图象图形学报,2010,15(1):45-49.

[4]闫晶. 基于VC++的YUV420与RGB24之间的视频图像格式相互转换[J]. 电脑与信息技术,2013,21(2):19-21,25.

[5]Benoit Payette. Color Space Converter:RGB toYCbCr[J]. XILINXxapp(V1. 0)September,2002:636-637.

[6]Andy Miller. Color Space Conversion-Part 2[R]. XilinxTechXclusives-Support Xilinx,2001:65-66.

[7]程星,吴金,陆生礼. 色彩空间RGB与YUV转换的硬件设计[J]. 电子器件,2007,30(2):661-663.

[8]于慧明,胡永华,高明伦. 基于参数化高基乘法算法的颜色空间转换[J]. 微电子学与计算机,2001(5):25-28,35.

[9]张秀丽. 颜色空间转换的硬件设计与实现[J]. 信息通信,2009(2):54-56.

[10]钟声,侯朝焕,杨常安. 基于FPGA的矩阵乘法器优化设计[J]. 电子测量技术,2008,31(2):95-98,102.

张杰(1989-),男,汉族,四川达州,四川大学物理学院微电子专业硕士研究生,研究方向为超大规模集成电路设计;

高博(1975-),男,副教授(通讯作者),主要从事CMOS集成电路芯片设计和生物医学成像领域的研究;

龚敏(1961-),男,教授,博士生导师,从事新型半导体材料与器件工艺、集成电路设计和工艺及半导体器件的辐照效应研究;

刘兵(1990-),男,汉族,四川遂宁人,硕士研究生,研究方向为超大规模集成电路设计,363192202@qq.com。

DesignofColorSpaceTwo-WayConversionCircuitBasedonFPGA

ZHANGJie,GAOBo,GONGMin*,LIUBing,CHENChang

(Key Laboratory of Micro-Electronics Technology of Sichuan Province,Chengdu 610064,China)

The conversion circuit between RGB and YUV color space is widely used in video compression and image transmission. In order to reduce chip area of the conversion circuit and implement the two-way conversion with only one module circuit between RGB and YUV color space,by using PLL(Phase Locked Loop)embedded in programmable devices and pipeline algorithm,and the multiplexing structure of matrix multiplication,a new circuit structure is proposed. The simulation results showed that the maximum operating frequency of the new circuit structure with 3 multipliers and 3 adders reaches 105.89 MHz. Therefore,the new circuit structure which meets the high data transfer saves chip area greatly.

FPGA;color space conversion;matrix multiplier;PLL

2014-01-07修改日期:2014-03-15

TN402

:A

:1005-9490(2014)06-1121-04

10.3969/j.issn.1005-9490.2014.06.023