星载多体制调制高速数字成形滤波器设计

2014-08-08史江博周建华

史江博, 周建华, 郑 戈

星载多体制调制高速数字成形滤波器设计

史江博, 周建华, 郑 戈

(北京遥测技术研究所 北京 100076)

卫星通信信道是典型的功率和频带受限信道,为了提高频带利用率,降低码间干扰,在卫星高速数据传输中,需对卫星发射信号进行成形滤波处理。针对星载高码率数据传输,提出一种基于多路并行运算的高速数字成形滤波算法,降低了成形滤波的工作频率,解决了高速数字成形滤波器难以实现的问题,同时实现了多体制调制信号的成形滤波。仿真及验证结果表明,算法可行,可应用于星载高码率多体制调制信号的成形滤波。

数字成形滤波; 多路并行算法; 多体制调制

引 言

随着对地观测卫星、通信卫星、中继卫星等航天技术的不断发展,卫星所获取的数据量突飞猛进,而星上数据存储能力受到体积、重量、功耗等方面的限制不可能无限制增加,这就需要及时可靠地将卫星所获得的数据传输至地面。在中继卫星通信系统及卫星对地数传系统中,下行链路数据传输达每秒几百兆比特甚至达到每秒吉比特量级。高速数据的调制解调成为中继卫星通信系统的关键问题之一。

卫星通信信道是功率和频带受限信道,同时也是非线性的恒参信道。在卫星通信中,要在尽量窄的频带内,使信息的传输速率最大,同时尽可能地减小能量的消耗,降低误码率,改善信噪比性能。为了提高频谱利用率,除了采用一些高效的数字调制技术、正交极化技术外,还广泛采用成形滤波技术,对发射信号进行处理,使其在消除码间干扰和实现最佳检测的前提下,压缩信号频带,从而提高频谱利用率。早期的成形滤波采用模拟滤波器实现[1],但模拟成形滤波器制作和调整较为复杂,体积不易缩小,相比之下数字成形滤波器具有高精度、高可靠性和高灵活性的优点,同时还具有便于大规模集成、易于实现线性相位等特点[2],因此数字成形滤波技术在全数字调制解调中得到越来越多的应用。

数字成形滤波器的实现方法有卷积滤波法[3]和查表滤波法[4~7]。卷积滤波法是根据输入的数据序列,通过卷积法或变换域法实时计算出对应的输出序列,这需要大量的乘法器和加法器,运算量较大。查表滤波法是预先将成形后可能的基带波形样本值存储起来,根据输入数据,从存储器中寻找相应的波形数据并输出,该方法实现简单,适合FPGA实现。文献[5]采用多相一步查找表法,使用二进制编码作为子滤波器统一寻址地址,一步查表直接将滤波器的卷积结果输出,实现了800Mb/s的16QAM高速数字成形滤波器设计和实现。由于是一步查找,查找表地址位数较多,查找表较大,比较耗费资源。文献[6]采用多相分布式算法(DA)结构,通过将各输入数据产生的部分积预先相加形成相应部分积,然后再对各部分积进行累加形成最终结果,实现了600Mb/s的TCM-8PSK高速数字成形滤波器的设计和实现。但是当数据速率进一步提高时,由于器件最高工作频率的限制,滤波器将难以实现。

卫星通信系统通常采用SQPSK/QPSK调制方式,且随着航天技术的不断进步,8PSK、16QAM等高阶调制方式也逐渐应用于卫星高速数据传输[8]。本文通过算法改进,在资源利用率和提高速度之间进行合理取舍,实现了更高码率的数字成形滤波器设计,打破了硬件对高速数字成形滤波器实现的限制,并在此基础上实现了高码率的多调制体制数字成形滤波器设计。

1 数字成形滤波器基本原理

图1 基带传输系统模型

基带传输系统模型如图1所示。根据奈奎斯特第一准则[9,10]提出的无失真传输条件保证了脉冲序列在接收端采样点处无码间干扰。基带系统的整体传输特性应满足奈奎斯特第一准则。满足奈奎斯特第一准则的脉冲形式有很多种,其中具有理想低通特性的脉冲频带利用率最高,但在物理上是无法实现的,且其时域响应波形衰减幅度较大,容易出现严重的码间干扰。而在实际通信系统中广泛应用的成形滤波器是升余弦滤波器。

按照最佳接收原理,发送端滤波器与接收端滤波器应共轭匹配,因此在实际应用中,发送端与接收端滤波器通常均设计为具有平方根升余弦特性的滤波器。平方根升余弦滤波器的频域响应和时域响应表达式分别为:

式中,H(f)为升余弦滤波器的频域响应,hT(t)和hR(t)分别为发送端和接收端滤波器的时域响应,T为符号间隔,α为滚降系数。发送端数字成形滤波器的设计应满足式(1)平方根升余弦特性。具体实现时,数字成形滤波器采用FIR滤波器。升余弦成形滤波器有如下几个重要参数:滚降系数α、滤波器采样频率、滤波器有效截断码元长度等,这些参数的选择对系统误码性能、硬件实现难易程度、运算速度等有直接影响。本文参数选择通过Matlab仿真得到。

在卫星高速数传系统中,信息传输速率较高。由奈奎斯特采样定理可知,信号采样时,采样频率必须大于等于最大频率的两倍。但是在滤波器设计时,需要对时域波形的有效码元进行截取,这就会造成频谱扩展,易产生频谱混叠。采样率越高,频谱产生的混叠就越小,但高采样率对硬件要求较高,实现起来较为困难,需综合考虑选取。滤波器为多倍采样,采样频率很高,而在高采样频率下直接进行滤波运算,会由于硬件工作频率的限制而变得难以实现。由数字信号处理[11]知识可知,M倍采样下,滤波器相当于M倍内插结构,在实现时可采用多相结构,将滤波器变为M个子滤波器[12],这样就可以降低数据的传输速率,便于硬件实现。滤波器多相结构原理如图2所示。

图2 滤波器多相结构原理

2 基于多路并行运算的高速数字成形滤波器设计

虽然数字成形滤波器在实现时可采用多相结构进行降速处理,但当卫星的数据传输码率进一步提高时,多相结构的成形滤波器还是会因为FPGA的工作频率或时钟的限制而变得难以实现,此时需进一步降低滤波器的工作频率,以适应卫星通信日益增长的高码率需求。

数据在进行成形滤波时,一个时钟周期内完成一次滤波运算并将结果输出。因此,可采用并行算法,在FPGA一个时钟周期内完成多次滤波运算,一次得出多个输入数据的成形滤波运算结果,这样就将单路运算变为多路运算,降低了高速数据成形滤波时的工作频率,有利于硬件FPGA实现且数据的运算速率得到极大的提高,可满足更高速率的卫星数据传输要求。以成形滤波两路并行计算为例,滤波器输入、输出关系如式(3)所示。

其中,N为滤波器系数的个数,M为滤波器采样倍数,yi,m为第i时刻第m+1个子滤波器的两路输出。每个时钟周期内同时完成两路数据的成形滤波计算并同时输出结果,在输出端将两路数据复合为一路高速数据输出,再经D/A转化为模拟数据输出处理。这里,D/A是具有数据复合转换功能的高速器件。与单路运算相比,两路并行运算在时钟不变的情况下可将数据率提高一倍,大大地提高了数据的传输速率。并行路数越多,传输的数据率提高得也就越多。基于两路并行运算4相滤波器的硬件实现结构如图3所示。

图3 基于两路并行运算的成形滤波器的硬件结构框图

当二进制数字信息进入传输系统后,首先进行串并转换完成符号映射,形成I/Q两路数据,单个子滤波器采用查找表实现。采用两路并行运算后,若仍采用传统的分布式查找表算法,则加法器数目会成倍增加,大大增加了器件的资源消耗。本文在分布式查找表算法的基础上进行一些优化,将滤波器乘法运算与流水线第一级加法运算组合起来用查找表实现,这样可以大量减少加法器的使用,降低硬件资源的消耗。查找表的数据可通过Matlab计算得到。基于两路并行运算的8PSK调制成形滤波器子滤波器的实现原理如图4所示,其中寄存器1~8和9~16分别为两路并行运算的地址寄存器。由于每个查找表规模较小,因此采用时序逻辑电路实现,从而节省了IP核资源。本文将映射数据通过数据寄存器生成能够实现多路并行的查找表地址,相比文献[5],查找表地址大大减少,节省了较大的存储空间。经加法器输出的数据为每个子滤波器同时经过两次或多次查找表结构的数据输出,在输出端将每个子滤波器的两路或多路数据复合为一路高速数据输出,再对多相数据在FPGA外部完成多路复合输出。

图3和图4构成的成形滤波器在FPGA中共需744个SLICEs资源,占芯片XQR4VSX55 SLICEs总数24576的3%,比文献[6]使用的788个SLICEs更加节省资源。该程序占用硬件资源非常少,而系统数据处理能力却成倍增加,并且解决了因硬件工作频率的限制造成的高速数字成形滤波器难以实现的问题,相比现有方法可极大地提高成形滤波器对更高数据率的运算能力。

图4 基于两路并行运算的8PSK调制成形滤波器子滤波器的实现原理

3 多体制调制下的数字成形滤波器设计

在卫星高速数传系统中,常采用QPSK/SQPSK调制体制来完成数据传输。随着卫星数传速率的进一步提高,使用QPSK带来的宽带激增、传输效率低下等问题日益突出,为此高阶的8PSK调制体制也逐步应用于卫星高速数传系统。在实际应用中,有时候会根据不同的数据速率采用不同的调制体制来完成卫星数据的编码传输。

高码率数据进入FPGA后,根据调制体制选择信号的不同,系统将选用不同的调制方式。在硬件实现时,利用图3和图4的成形滤波器结构完成硬件设计,由于查找表采用时序逻辑电路实现,因此可将8PSK与QPSK的查找表进行合并,通过调制体制选择信号选择不同的输出。

SQPSK成形滤波器设计与QPSK情况相同,只是SQPSK的Q路信号延迟I路信号半个码元。传统做法是将Q路数据利用DCM数字时钟管理模块的调相功能完成数据延迟,这种做法难以获得足够的精度且实现起来较为麻烦,特别是在数据率较高的时候。本文利用成形滤波器实现结构与寄存器固有延迟来实现Q路数据延迟关系,且由于寄存器延迟精度较高,在输出时将子滤波器输出数据作适当延迟即可完成I/Q数据相差半个码元的要求,这样便可完成SQPSK调制方式的成形滤波器设计,其实现原理如图5所示。相比传统方法,本文方法更易于实现,适合高速数据的成形滤波。

图5 SQPSK调制的成形滤波器实现原理

4 仿真验证

本文设计的数字成形滤波器参数为:滚降系数α为0.5,4倍采样,成形滤波器系数通过Matlab计算得到。硬件仿真验证采用两路并行算法,通过ISE与ModelSim联合建模仿真得到QPSK调制下的成形滤波器仿真波形,如图6所示,图中dindout_I和dindout_Q分别代表信号成形滤波前的I路和Q路波形,dout_I和dout_Q分别表示信号经成形滤波后的I路和Q路波形。从图6中可以看出,一个符号周期内系统有四个样点输出,同时可以看到一个符号成形后波形信号有一定的延迟。这是由于滤波器本身及FPGA内部的寄存器等延迟造成的。SQPSK调制波形仿真结果如图7所示。从图7中可以看出,成形后的Q路数据延迟I路数据两个采样周期,即半个码元周期,完成了SQPSK的波形成形。

图6 QPSK调制下的成形滤波器仿真结果

图7 SQPSK调制下的成形滤波器仿真结果

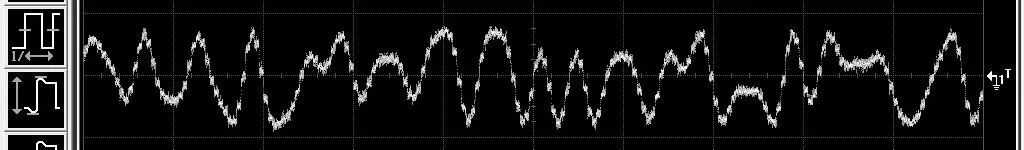

图8为1.5Gb/s数据率的8PSK调制方式在硬件平台上的实测波形图,图9为测试的星座图和频谱图。从图8中可以看出,实测波形比较平滑,看不到明显跳变,与仿真结果一致。滤波前频谱主瓣带宽为1GHz,成形滤波后其频谱的主瓣带宽为500MHz×(1+0.5)=750MHz,频带利用率有所提高,且滤波后旁瓣得到了有效抑制,星座图清晰、聚拢。硬件仿真及测试结果表明:多路并行查找算法可以在硬件中实现,能够有效提高数据的运算速率,适合更高码率下卫星数据传输的数字成形滤波,同时也可以实现多调制体制下的数字成形滤波,适应卫星多体制多速率下的数据传输波形成形要求。

图8 8PSK调制下的成形滤波实测波形图

图9 8PSK调制下成形滤波后信号实测星座和频谱图

5 结束语

数字成形滤波器在卫星高速数据传输中的使用,能够节省频带资源,降低码间干扰,对于卫星高速数据传输具有重要意义。本文提出的数字成形滤波高速并行算法,每个时钟周期内同时做多次滤波运算,降低了成形滤波器的工作频率,提高了数据传输速率,打破了硬件对卫星高速数字成形滤波器实现的限制,且节省了硬件资源,适合星载高速率的编码调制波形成形要求。本文以两路并行查找运算为例,通过对QPSK、SQPSK、8PSK多体制下成形滤波器的硬件仿真及测试,验证了算法的可行性,该算法能够达到成形滤波降速的目的,极大地提高了卫星的数传速率,并能满足卫星数据传输多体制多速率的传输要求,可应用于星载高码率多体制调制成形滤波器的设计实现。

[1] Dlklemba J J.Poles-zero Approximations for the Raised Cosine filter Family[J].Comsat Technical Review,1987,17 (1):18~25.

[2] 季 伟,周学军,林海涛,窦高奇.基带成形滤波器设计与实现[J].舰船电子工程,2012,32(2):131~133.

[3] 杨贞斌,邬江兴.一种数字化基带成形实现新方法:基于码元间隔的定长滑动窗算法[J].通信学报,1999,20 (6):40~44.

[4] King Myung-Soon,Chung Jin-Gyun.Look-up Table-based Pulse-shaping Filter[J].Electronics Letters,2000,36 (17):1505~1507.

[5] Hu Junjie,Cheng Xin,Xiong Weiming,Chen Xiaomin.Design and Implementation of 800Mbps 16-QAM Pulse Shaping Filter in the Satellite High Speed Transmission[C].International Conference on Space Information Technology,2009,7651:1~5.

[6] 李爱红,肖山竹,张 琛,张尔扬.高速成形滤波器的设计实现[J].电路与系统学报,2006,11(5):90~93.

[7] 赵林军.根升余弦脉冲成形滤波器FPGA实现[J].现代电子技术,2011,34(1):23~25.

[8] 张 倩.卫星高速数传系统中调制方式的发展动态[J].空间电子技术,2002,(3):28~31.

[9] 周炯槃,庞沁华,续大我,吴伟陵,杨鸿文.通信原理[M].(第3版),北京:北京邮电大学出版社,2008.

[10] 樊昌信,曹丽娜.通信原理[M].(第六版),北京:国防工业出版社,2006.

[11] Diniz P SR,Silva E A B,Netto SL(著).门爱东,杨 波,全子一(译).数字信号处理系统分析与设计[M].北京:电子工业出版社,2004.

[12] 李增红,何攀峰,时 慧.多相滤波在脉冲成形中的应用[J].仪器仪表学报,2010,31(8):330~332.

Design of Spaceborne High-speed Digital Shaping Filter for M ulti-modulation Signals

Shi Jiangbo, Zhou Jianhua, Zheng Ge

The satellite communication channel is a channel typically limited by power and frequency band.In order to increase the frequency band utilization and depress the inter-symbol interference in the high-speed data transmission of satellite,the emission signal of satellite needs to be processed by the shaping filter.A multi-way parallel algorithm for the high-speed digital shaping filter aiming at the high bit-rate data transmission of satellite is proposed in this paper to depress the operating frequency and solve the problem thathigh-speed digital shaping filter is difficult to achieve,also it implements the digital shaping filtering ofmultimodulation signals.The simulation result shows that the algorithm is feasible and it can be applied to spaceborne high-speed digital shaping filtering ofmulti-modulation signals.

Digital shaping filtering; Multi-way parallel algorithm; Multi-modulation

TN927.22

A

CN11-1780(2014)05-0061-06

史江博 1988年生,在读研究生,主要研究方向为空间信息传输技术。

2013-11-26 收修改稿日期:2014-01-23

周建华 1966年生,硕士,研究员,主要研究方向为卫星通信技术。

郑 戈 1976年生,硕士,研究员,主要研究方向为卫星中继传输技术。