嵌入式处理器片外访存加密机制设计与实现

2014-08-04刘根贤王海霞刘振宇汪东升

刘根贤,王海霞,刘振宇,汪东升

1.清华大学计算机科学与技术系,北京 100084

2.清华大学信息科学技术国家实验室(筹),北京 100084

嵌入式处理器片外访存加密机制设计与实现

刘根贤1,2,王海霞2,刘振宇2,汪东升2

1.清华大学计算机科学与技术系,北京 100084

2.清华大学信息科学技术国家实验室(筹),北京 100084

1 引言

应用在电子商务、军事通讯等高安全敏感领域的嵌入式系统往往面临各种恶意攻击。这些攻击给嵌入式系统的安全带来巨大威胁,一旦得逞将给用户造成重大的损失。嵌入式系统由以微处理器为核心的硬件及其配套的固件构成。硬件系统可以划分为电路系统和芯片两个层次。恶意攻击者可以从一个或多个层次对嵌入式系统进行攻击,从而达到窃取或篡改高价值信息等非法目的。

在嵌入式系统的硬件设计中,设计者以微处理器为核心,根据功能需要设计数据采集处理,通讯等外设电路,往往需要设计SRAM或DRAM存储器以满足数据处理的需要,而后将相应的程序代码写入处理器集成的或电路板上的非易失性存储器中,从而构成整个系统。恶意攻击者在破解嵌入式系统时,可以在电路系统层次上进行多种方式攻击。这些攻击都是通过在系统的电路板上增加少量的硬件改动,并配合适当的底层手工代码,来达到监听总线、窃取机密信息的目的[1]。在这类攻击中,具有代表性的有:总线监听、数据篡改以及存储器复制等攻击方式。

对以总线监听以及数据篡改攻击为代表的外部攻击方式,根据目前嵌入式系统的实际状态,可以假设系统中仅微处理器本身是安全可信的,攻击者无法获取处理器内部的寄存器以及片内集成的SRAM或DRAM数据,而所有外部器件都是不可信任的,系统设计者无法确保来自这些器件的数据是否被监听或篡改。在这种前提下,嵌入式系统的攻击主要来自板载总线和板载存储器[2]。图1为嵌入式系统的硬件攻击模型。目前大部分微处理器都可以集成SRAM或FLASH甚至DRAM存储器,因此部分或整个软件系统可以固话在处理器内部的FLASH存储器中(即为固件)。因此可以假设攻击者无法获取嵌入式系统软件进行分析。

图1 常规嵌入式系统攻击

2 嵌入式系统片外访存加密机制设计

为了对抗这类外部攻击,嵌入式系统在设计时必须对此予以考虑。在已知攻击方式的情况下,若在设计时就有相关的安全机制,则可以有效地提高嵌入式系统的安全性。

2.1 嵌入式系统安全设计

根据已有的攻击行为特征,为嵌入式系统总结出了两项基本安全设计准则:

(1)敏感信息的机密性设计。嵌入式系统的安全机制应当能确保片外存储器中保存的敏感数据信息的机密性。即所有片外存储的数据都是经过加密操作的,难以分析的密文[3]。攻击者可以通过外部硬件工具完全读取片外存储器中的内容,或者捕获片外访存时处理器外部总线的所有信号,在没有密钥的情况下攻击者仍然无法即时获取其中的信息。这样才能保证攻击者不能通过这种攻击手段破解系统[4]。

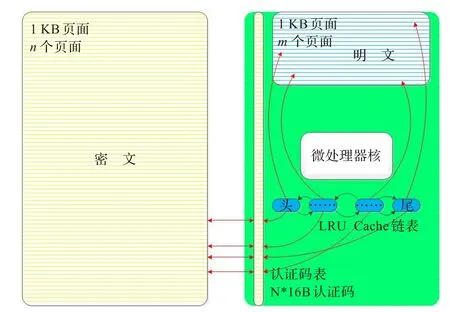

(2)敏感信息的完整性。对于恶意攻击者的总线篡改行为,仅仅加密数据还是不够。攻击者可以通过控制处理器外部总线信号,篡改数据,分析微处理器的响应行为,了解处理器的内部运行机制,通过重复尝试探测敏感数据。因此,为了能够对抗总线篡改伪造的外部存储器数据,嵌入式系统在使用外部存储器中数据之前需要先通过认证操作确保外部存储器中数据信息的完整性[5-6]。完整的具有外部访存加密认证的嵌入式系统如图2所示。

图2 嵌入式系统片外内存加密

此外嵌入式系统设计时还需要确保敏感信息的时效性[7]。诸如密钥等敏感信息保存的时间越长,被分析出的可能性就越高。根据程序流程或者运行周期,定期更换密钥,则嵌入式系统中保存的敏感信息具有时效性,就可以有效地防止攻击者对系统的暴力攻击,确保整体系统的安全性。

器件选型和软件设计时尽可能选择使用片内集成RAM和片内集成程序存储器,减少片外敏感数据的传输[8]。如果微处理器的读指令和数据操作都可以在微处理器片内进行,则意味着更少的敏感信息暴露在电路板的外部总线上,从而减小总线监听的信息泄露风险;此外减少片外数据传输可以避免攻击者篡改总线信号,增加攻击者通过总线监听分析敏感数据的难度。相反如果程序存储器和内存都需要集成在在电路板上,则无法保证程序不被直接逆向工程分析,更无法保证敏感数据的安全性。

通过以上的安全机制,嵌入式系统可以对系统中敏感信息的机密性、完整性提供完善的保护,从而有效地避免攻击者通过总线监听、篡改等攻击方式,分析系统响应,探测系统的设计漏洞,获取敏感信息。

2.2 数据加密和完整性认证算法

要实现外部敏感信息的机密性和完整性设计,就需要采用加密和认证算法。常用的加密算法有DES、3DES、AES等,常用于数据完整性认证的HASH算法有MD5、SHA-1等。可以根据系统加密强度需要选择相应的算法,以软件实现算法运算,此外也有不少微处理器已经集成了密码算法加速引擎和真实随机数发生器,以提高算法性能。

根据高安全敏感领域的嵌入式系统的强安全性要求,选择高级加密标准的Galois/计数器模式(AES-GCM)作为加密算法和数据完整性算法[9-10]。AES-GCM是一种使用分组密码进行加密并在伽罗华域(GF(2128))上计算认证码的加密认证算法。此伽罗华域由多项式x128+x7+x2+x+1定义。

AES-GCM算法分两个部分:一个用于数据加解密的AES,另一个用于计算认证码的伽罗华域乘法器。AES-GCM一次运算即可以加密并产生HASH认证码,或者解密并认证数据完整性。

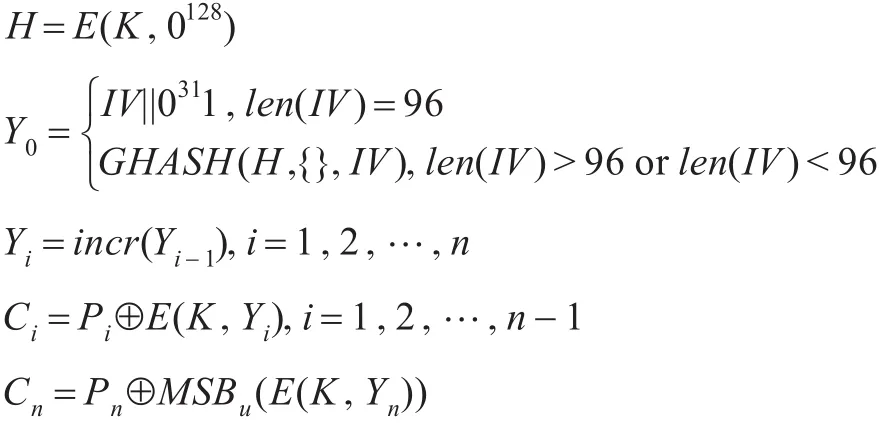

AES-GCM算法数学描述如下:

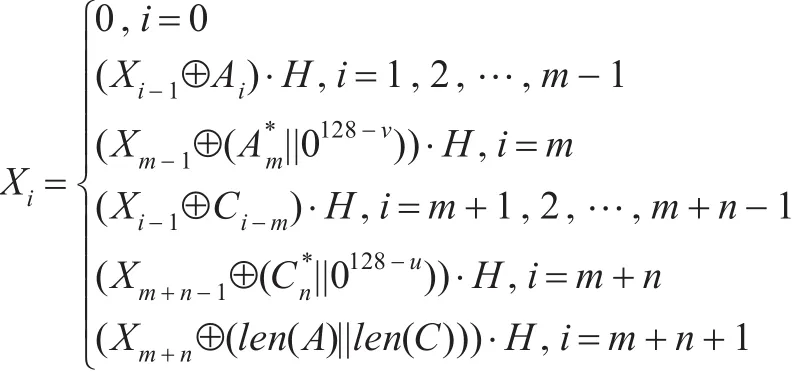

最后一组数据长度为u,其他分组长度均为128位,其中||表示串连接,len表述数据位长度,E(K,Y)表示用密钥K对Y做AES加密。上面描述中所用的GHASH函数定义如下:AES-GCM通过分组加密算法AES以计数器模式将输入的数据帧以128位长度为单位进行分组,当最后一个分组不是128位时,将会添加0使分组达到128位。每个分组通过AES读数器模式加密为密文,密文与散列密钥进行循环相乘,当最后一个分组与散列密钥相乘完毕后,附加认证数据与密文的长度信息与相乘的结果进行异或,最终得到128位的认证码,如图3所示。

图3 AES-GCM算法加密流程

AES-GCM解密认证时,由密文与附加认证数据生成一个新的认证码,将它与加密时产生的认证码进行比较,如果两个认证码不一致,说明数据完整性被破坏,数据已经被篡改。嵌入式系统软件可以对这种攻击行为进行相应处理。

2.3 嵌入式系统的片外访存安全机制

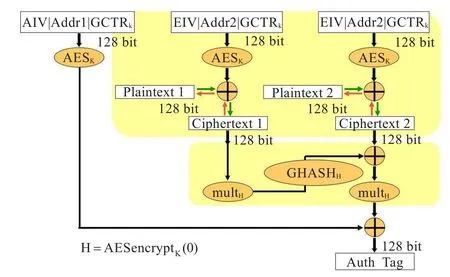

采用AES-GCM算法设计嵌入式系统的片外访存加密认证机制。综合考虑微处理器的访存局部性以及片外存储器的组织结构,选择AES-GCM的加密数据帧长度为1 024字节,产生的认证码长度为16字节。这种条件下,片外存储器被划分为一组1 KB大小页面,存储加密的敏感数据,而每个页面产生的16字节认证码,以及加解密所需密钥需要存放到可信存储空间[11-12]。

图4 多级认证码存储结构

当片外存储器的容量比较适中,可以将所有页面的认证码存储到微处理器片内SRAM,典型的嵌入式系统片外存储器往往不超过1 MB,以片外存储器1 MB为例,片外存储器划分为1 024页面,需要16 KB的片内存储器存放认证码,16字节用于密钥。

而当片外存储器远大于1 MB时,片内SRAM已经无法满足存储认证码的需求,可以采用多级页表模式,将认证码也作为敏感数据加密后保存到片外存储器。而片内SRAM存储保存末级认证码的片外存储器页面的认证码[13]。

此外虽然每个页面都可以使用不同的密钥,但这样将需要花费较大的可信存储空间代价。因此方案设计中,采用二次密钥进行加解密。

其中Addr为页地址,S为置乱操作,原始密码和页地址进行一次置乱运算,这样虽然原始密钥相同,而每个页面的实际密钥完全不同,在没有增加存储代价的情况下,提高了系统的整体安全性。

3 基于STM32微处理器的实现及评估

为了验证片外访存加密机制的可行性,以及评估加密机制带来的性能影响,选择较为典型的STM32系列嵌入式处理器系统实现片外访存加密机制。STM32微处理器是ST公司基于ARM公司授权的CORTEX-M系列内核开发的面向嵌入式实时系统应用处理器。

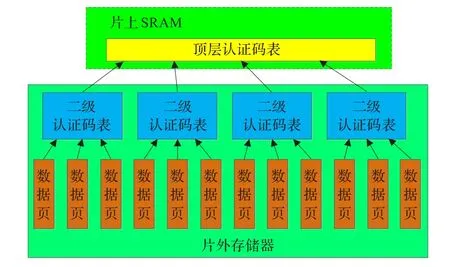

STM32系列处理器通过FSMC扩展外部SRAM存储器,容量不超过1 MB,采用1级TAG表方式,外部SRAM存储器页面的TAG直接存放到STM32处理器片内,如图5所示。

图5 STM32嵌入式系统片外访存加密

STM32访问外部SRAM存储器时,页面大小为1 KB,而STM32F40x的Cache line为16字节,由于处理器硬件目前并不支持片外加密访存,因此当处理器需要访问片外存储器中存储的数据时,必须先解密到片内SRAM,再进行操作,为了提高明文利用率,软件设计Cache进行缓存管理。

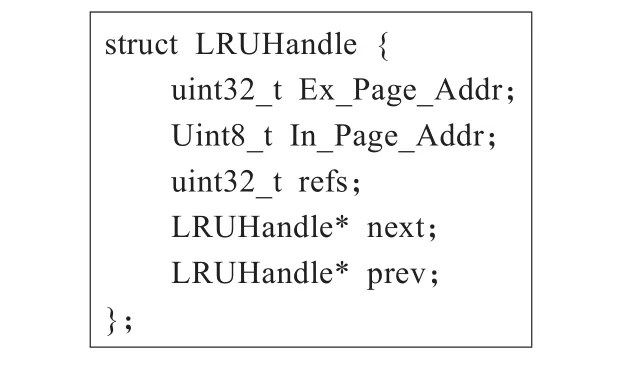

软件Cache用来提高加密片外存储器的访存效率。Cache替换算法常见的有FIFO(first in first out)和LRU(least recently used),FIFO算法对CPU的指令序列非常有效,但对于Memory或者磁盘文件的这种数据,LRU算法更有效。因此选择LRU算法设计缓存管理[14]。

从微处理器片内SRAM存储空间划分一块用于软件LRU cache,占用16 KB,分成16个缓存页面,每一块对应片外存储器的一个页面,只是存放的是对应的明文数据,形成这种映射关系。当Cache中的存储块被用完,而需要把新的页面解密缓存进Cache的时候,就需要LRU算法来完成缓存块的替换,选择再次访问概率最小的缓存块,如果该缓存已被修改则加密写出到对应的片外存储器页面,如果没有修改则无需操作。LRU算法是基于最近用到的数据被重用的概率比较早用到的数据被重用的概率大得多的规律来实现的[15]。

Cache中的所有缓存块位置都用双向链表链接起来,数据结构如图6,Ex_Page_Addr为片外存储器页面索引,In_Page_Addr为片内缓存页面索引,refs用于性能统计的命中次数计数,next指向下一个缓存节点,prev指向前一个缓存节点。当一个缓存被命中后,就将通过调整链表的指向将该缓存节点调整到链表的头位置。新缓存的页面直接放在链表的头上。在系统软件运行中,最近被命中过的缓存节点就向链表的头移动,而没有被命中的缓存节点就向链表的后面移动。当需要缓存新页面时,链表最后的节点指向的页面就是最近最少被命中的页面,只需要淘汰链表最后的节点指向的缓存,将新的内容放在链表前面节点就可以。

图6 软件LRU cache数据结构

使用双向链表软件实现LRU cache是因为Cache中块的命中可能是随机的,和系统软件访存局部性有关,和解密缓存进来的顺序无关,而采用双向链表这种结构来保存位置队列,使得其可以灵活地调整相互间的次序。此外双向链表可以快速访问前后节点,时间复杂度为O(1)。

为了评估加密机制性能,基于STM32系列微处理器硬件平台对比试验,软件实现DES和TDES的ECM和CBC模式加密算法,MD5、SHA-1、SHA-224和SHA-256四种HASH算法,AES算法的ECB,CBC,CTR,CCM和GCM五种模式加密算法。AES-CCM和AES-GCM是加密和认证一体的算法,对于其他则是单纯的加解密算法和HASH算法,可以根据加密强度需要选择响应的加密算法和HASH算法组合实现片外访存的加密和认证。算法均可以通过软件实现,而硬件加速则依赖特定型号器件。

表1 STM32微处理器平台片外访存加密认证

为了评估加密机制性能,通过FSMC接口扩展1 MB SRAM存储器,软件存储器按1 KB划分页面,内存压力测试随机选择页面,页面中随机写入、随机读出256字节数据。测试中AES算法选择AES-128位,可选AES-196或AES-256满足更高加密强度需要。

4 结论

本文以嵌入式系统安全机制为研究目标,从片外访存的机密性、数据完整性出发,构建安全机制,探索嵌入式系统面临的外部攻击的对抗方法,并对典型硬件平台的实现展开可行性评估。在假设嵌入式处理器本身是安全可信的条件下,采用AES-GCM算法对片外存储器加密认证,可以有效地保证嵌入式系统的安全性,在STM32F103微处理器平台以软件实现了该加密机制,在内存压力测试中其片外访存平均性能降低了40%,验证其可行性。通过一次密钥和页面地址置乱,使得不同页面具有完全不同的密钥,确保了加密强度。通过软件设计LRUcache缓存明文,较好地优化了系统性能,降低采用加密和认证带来的性能损失,片外访存性能仅下降了9%。

[1]Huang A.Hacking the Xbox:an introduction to reverse engineering[M].San Francisco,CA:No Starch Press,2003.

[2]Yan C,Rogers B,Englender D,et al.Improving cost,performance,and security of memory encryption and authentication[C]//Proc of the International Symposium on Computer Architecture,2006:1-12.

[3]Gassend B,Suh G,Clarke D,et al.Caches and hash trees for efficient memory integrity verification[C]//Proc of the 9th International Symposium on High Performance Computer Architecture(HPCA-9),2003:1-14.

[4]Suh G E,Clarke D,Gassend B,et al.Hardware mechanisms for memory integrity checking,Technical Report MIT-LCSTR-872[R].2002:1-17.

[5]Durahim A O,Savas E,Sunar B,et al.Transparent code authenticationattheprocessorlevel[J].IETComputers and Digital Techniques,2009,3(4):354-372.

[6]Hu Yin,Hammouri G,Sunar B.A fast real-time memory authentication protocol[C]//Proceedings of the 3rd ACM WorkshoponScalableTrustedComputing,NewYork,NY,USA,2008:1-10.

[7]Clarke S D,Gassend B,van Dijk M,et al.Efficient memory integrity verification and encryption for secure processors[C]//The 36th International Symposium on Microarchitecture,2003:339-350.

[8]Recommendation for block cipher modes of operation:Galois/Counter Mode(GCM)and(GMAC)[Z].Inst Standards Technol,Special Publication 800-38D,2007.

[9]McGrew D A,Viega J.The Galois/counter mode of operation(GCM)[Z].Nat.Inst Standards Technol,Updated Submission to Modes of Operation Process,2005.

[10]Elbaz R,Champagne D,Lee R B,et al.TEC-Tree:a lowcost,parallelizabletreeforefficientdefenseagainst memory replay attacks[C]//Cryptographic Hardware and Embedded Systems(CHES),2007:289-302.

[11]Clarke D,Edward Suh G,Gassend B,et al.Towards constant bandwidth overhead integrity checking of untrusted data[C]//2005 IEEE Symposium on Security and Privacy,2005:1-19.

[12]Vaslin R,Gogniat G,Diguet J P,et al.A security approach for off-chip memory in embedded microprocessor systems[J].Microprocessors and Microsystems,2009:37-45.

[13]Vaslin R.Hardware core for off-chip memory security management in embedded systems[D].Univ South Brittany,Morbihan,France,2008.

[14]Dybdahl H,Stenstrom P,Natvig L.An LRU-based re-placement algorithm augmented with frequency of access in shared chip-multiprocessor caches[C]//MEDEA.06.USA:New York,2007,35(4):46-47.

[15]Jeong J,Dubios J,Dubois M.Cost-sensitive cache re-placement algorithms[C]//ProceedingsoftheNinthInternational Symposium on High-Performance Computer Architecture(HPCA-9.03).[S.l.]:IEEE Computer Society,2002:1-4.

LIU Genxian1,2,WANG Haixia2,LIU Zhenyu2,WANG Dongsheng2

1.Department of Computer Science and Technology,Tsinghua University,Beijing 100084,China

2.Tsinghua Laboratory for Information Science and Technology,Beijing 100084,China

Embedded systems in high security-sensitive areas are susceptible to various types of attacks,including stealing passwords,tampering data and offline analysis.Especially,the hardware-level attacks often result in significant losses to the users.In order to defend the above attacks,the off-chip memory is encrypted and authenticated through AES-GCM algorithm.This scheme writes data after encryption,decrypt and authenticate after read data.In addition,a function is built that scrambling password with page address to ensure the encryption strength.Finally LRU cache is introduced to improve its performance.The scheme is implemented on STM32F103 microprocessor platform in software and the feasibility of the system design is proved.The memory stress experiment shows that the system security is strengthened with 9%performance degradation.

embedded;microprocessor;off-chip memory;encryption and authentication

高安全敏感领域的嵌入式系统面临总线监听、数据篡改、离线分析等类型的恶意攻击,试图窃取密码、篡改信息等。特别是配合硬件电路的攻击,给用户造成重大的损失。为了从根本上解决系统外部电路系统攻击威胁,提出片外访存加密认证机制,选择AES-GCM算法,对所有片外写数据进行加密,对读数据进行解密并认证。同时设计一次密码与页地址置乱函数产生二次密钥,保障了加密强度。进一步通过软件实现LRU Cache优化性能,在STM32系列微处理器硬件平台上,软件实现片外访存加密认证机制。在内存压力测试中,加密片外访存性能平均降低了9%。

嵌入式;微处理器;片外访存;加密认证

A

TP309

10.3778/j.issn.1002-8331.1403-0022

LIU Genxian,WANG Haixia,LIU Zhenyu,et al.Encryption scheme design and implementation of embedded processor off-chip memory access.Computer Engineering and Applications,2014,50(22):92-96.

国家高技术研究发展计划(863)(No.2012AA012609,No.2012AA0100905);国家自然科学基金(No.61373025,No.61303002)。

刘根贤(1974—),男,博士研究生,研究领域为嵌入式系统,信息安全;王海霞(1977—),女,博士,副教授,研究领域为高性能计算,形式验证;刘振宇(1974—),男,博士,副教授,研究领域为视频编码,VLSI设计;汪东升(1966—),男,博导,教授,研究领域为计算机体系结构,高性能计算和存储系统。E-mail:liugx08@mails.tsinghua.edu.cn

2014-03-05

2014-04-24

1002-8331(2014)22-0092-05

CNKI网络优先出版:2014-07-11,http://www.cnki.net/kcms/doi/10.3778/j.issn.1002-8331.1403-0022.html