一类适用于串行通信的高速包络检测电路

2014-07-26罗志聪孙奇燕方金花

罗志聪,孙奇燕,方金花

(1.福建农林大学机电工程学院,福建 福州350002;2.贝莱特集成电路(福州)有限公司,福建 福州 350003)

USB2.0具有即插即用、数据传输快等优点,广泛地应用在数据通信中,目前普遍采用分立的USB2.0芯片实现,成本较高.随着信息社会的发展,芯片规模也越来越大,越来越多的芯片希望集成USB2.0功能模块,从而降低芯片的应用成本.如TI公司的STM32系列的arm芯片集成了USB2.0的全速模式,飞思卡尔的K60系统arm芯片集成了USB2.0的高速模式.

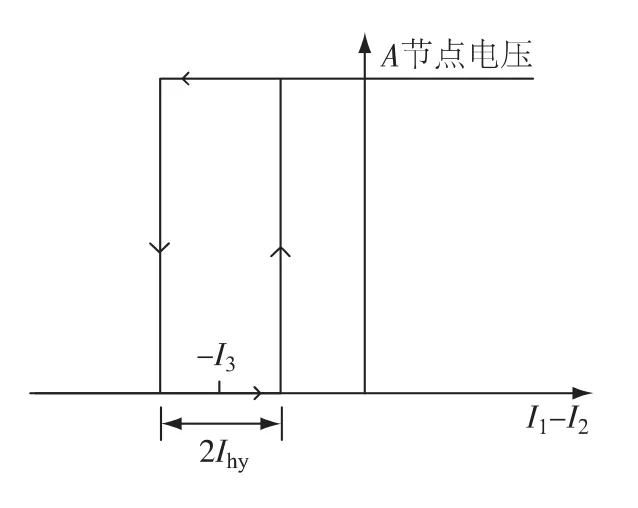

包络检测电路是USB2.0系统中非常重要的模块,主要作用是区分噪声和数据[1-3].USB2.0 协议规定,当包络检测器的输入电压(INP、INN的电压差)小于100mV时,输出信号Squelch为低电平.当包络检测器的输入电压大于150mV时,输出信号Squelch将输出高电平,如图1所示.

文献[3]和文献[4]采用图2所示的包络检测器结构,该电路结构有一定的局限性,主要原因是输出的Squelch信号持续输出高电平的时间是由电阻R1和电容C1的延迟决定的,因此不能有效反映数据线上的状态.如在电路设计时,为了保证数据线上出现连续8bit的J状态或者K状态时Squelch信号持续输出高电平,数据线上单次数据跳变引起的Squelch输出高电平持续时间必须大于8×2.08ns=16.64ns,该持续时间不能过长,否则会导致数据延迟过大,无法满足协议要求.然而在高速断开检测过程中,主机会发送一个uSOF EOP包,该包会有持续40bit的K或者J状态,按上述指标设计的包络检测将不能有效地反映数据线上的状态.

图1 适用于USB2.0的特性曲线Fig.1 The transmission characteristic curve for USB2.0

其中文献[4]没有讨论工艺、温度以及电源电压(PVT)等对系统性能的影响.

图2 传统包络器Fig.2 The conventional envelop detector

文献[5]采用额外的校准电路抑制了PVT的影响,设计了如图3所示具有数模转换器(DAC)校准的预放大电路,校准电路在上电过程中工作,需要大量的数字控制电路,占用面积大,校准过程相对复杂.

除此之外文献[3-5]所采用的方案中,其输入输出特性曲线和协议要求的图1有所差别,其最大问题是当输入电压之差在负向阈值电压和正向阈值电压区间时,Squelch输出值不确定,与协议要求不符合.

图3 具有DAC校准的预放大电路Fig.3 The pre-drive amplifier with DAC calibrate

因此设计一个对PVT不敏感的、能有效反映数据线上状态的且其输出特性曲线完全符合USB2.0协议要求的包络检测电路是一个挑战.

1 包络检测器电路的分析与设计

施密特触发器电路是包络检测器的核心电路,电流型施密特触发器具有增益适中、带宽宽、功耗低的优点.

1.1 抑制PVT变化的新颖施密特触发器设计

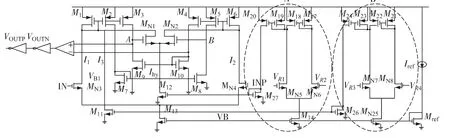

在文献[6]的基础上,提出了如图4所示的新颖的电路结构,图4所示电路和文献[6]中电路相比多了I3电流源.为了分析简单,所有的电流镜管子的W/L都一样.这里分析时假设I2、I3和Ihy不变,且Ihy小于I3.

1.1.1 施密特触发器定性分析与电路设计

1)I1逐渐降低的过程.考虑到所有工作过程中,流过M9的最大电流等于I2+Ihy(此时Ihy由M6节点提供),因此如果有I1+I3≥Ihy+I2时,即I1-I2>-(I3-Ihy)时,A节点肯定输出高电平,Ihy电流由M1提供,进一步保证了A节点为高电平,因此流过M6的电流仅仅为I2.

当I1逐渐降低时,刚开始的时候Ihy继续由M1提供,此时依然有I1+I3+Ihy>I2.因此A节点继续高电平,B节点为低电平.

当I1继续降低,满足I1+I3+Ihy<I2时,即I1-I2<-(I3+Ihy),此时A节点输出低电平.同时Ihy转由M6提供,进一步保证了A节点输出低电平,B节点输出高电平.

图4 新颖的电流型施密特比较器电路Fig.4 Anovel current schmitt trigger

2)I1逐渐增大的过程.当I1很小,且满足I1+I3+Ihy<I2时,即I1-I2<-(I3+Ihy),此时A节点输出低电平,B节点输出高电平.

当I1逐渐增大时,依然有I1+I3<Ihy+I2,此时A节点输出低电平,同时Ihy继续由M6提供,B节点输出高电平.

当I1增大,且满足I1+I3≥Ihy+I2时,即I1-I2>-(I3-Ihy)时,A节点将变成高电平,此时Ihy将由M1提供,进一步保证A节点变为高电平,B节点变为低电平.

通过上述分析,可以得到图5所示的输出特性曲线.其中施密特触发器的正向(负向)阈值电流值的平均电流等于-I3,即该值由图5中的电流源I3决定;而回差电流值(正向阈值电流减负向阈值电流)等于2Ihy,即该值由图6中的电流源Ihy决定.因此电路设计时,平均电流值和回差电流值可以单独设定,互不影响.

完整电路图如图6所示,简称SchmitA电路.假设差分输入管MN3、MN4、MN5、MN6、MN7、MN8的宽长比一致,除了特别说明外,电流镜的宽长比都一致.

图5 新颖的电流型比较器输出特性曲线Fig.5 The transmission characteristic curve for current schmitt trigger

图6 新颖的完整的施密特触发器电路Fig.6 Circuit for the novel schmitt trigger

差分输入管MN3提供I1、MN4提供I2,因此I1-I2与输入电压VINN-VINP成比例关系.Ihy由虚线A内所示电路提供,因此Ihy与输入电压VR1-VR2成比例关系.I3由虚线B内所示电路提供,因此I3与输入电压VR3-VR4成比例关系.电路中VR1、VR2、VR3和VR4这4个电压由设计者根据应用场合自行设定.

1.1.2 抑制PVT变化的电路设计函数推导

许多器件和电路参数都随着制造工艺、电源电压和环境温度而变化.通常用PVT来表示这些效应.在指定的PVT变化范围内,所设计的电路性能应在一个允许的范围内.文献[5]采用了专门的校准电路,图6所示电路为完整的施密特触发器电路,通过合理的电路设计,施密特触发器的正向(负向)阈值电压和回差电压是PVT的弱函数,因此无需外加的校准电路.

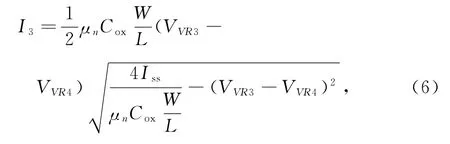

当MN3和MN4工作在饱和区时,对于平方率器件有

由式(1)~(3)可得

其中Iss为流过M13的尾电流.

同理可以得到

其中Iss为流过M14的尾电流.

其中Iss为流过M15的尾电流.

从1.1.1节分析可知当I1-I2=-I3时,为正负阈值电压的平均电压.当流过M15和M13的尾电流一致时,由式(4)和(6)可得正负阈值电压的平均值等于VR3-VR4,并且该平均值与Un、Cox等工艺参数无关,也与Iss电流源的精度无关,因此该平均值和PVT变化无关.

假设系统要求的回差电压为2X,正负阈值电压的平均值为Y,定义Y/X=N,(VR1-VR2)/X=M.同时定义一个参考电流源Iref,流过M13的电流为(N-1)2×Iref,流过M14的电流为M2×Iref,那么正负阈值电压VINN-VINP=-(N±1)X,代入式(4)~(6)可得:

由1.1.1节分析可知,正向阈值电流为I1-I2=-(I3±Ihy),因此由式(7)~(9)可得

由式(10)可以得到两个结论:1)在保证电路正常工作的前提下,正负阈值电压的大小与参考电流源Iref无关,因此对Iref的设计要求并不严格.2)当M和N值满足此电路设计函数时,正向和负向阈值电压将是PVT的弱函数,最终的结果是该包络检测的正负阈值电压受PVT的影响较小.

因此如图7(a)所示,正负阈值电压的平均值等于-(VR3-VR4),回差电压等于2(VR1-VR2)/M.将图6中的M11管的漏极改接到M5管的栅极,就得到一个新的电路,简称Schmit B电路,同理可以得到如图7(b)所示输出特性曲线.

图7 图6所示电路的输出特性曲线Fig.7 The output characteristic of the circuit shown in figure 6

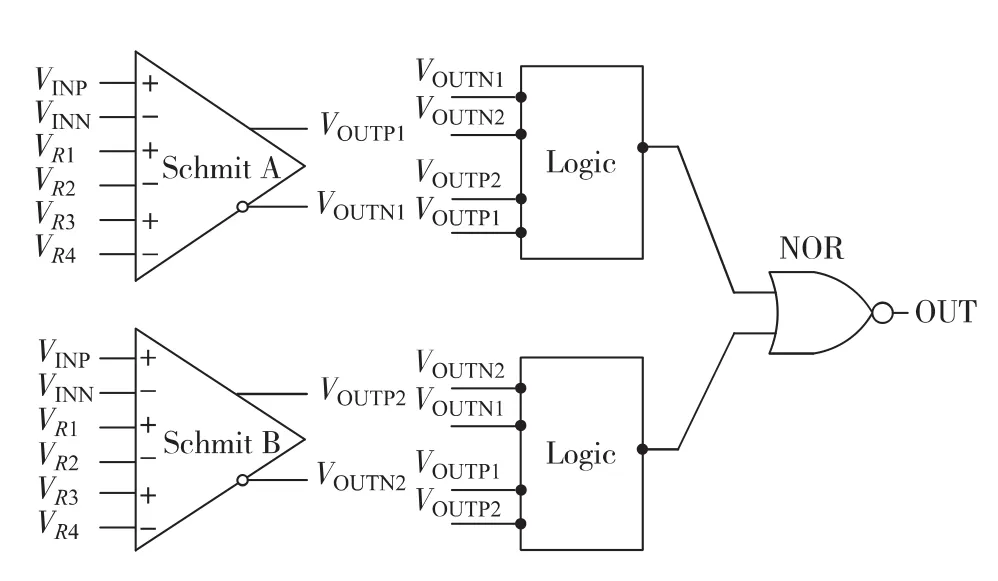

1.2 包络检测器完整电路设计

图8是完整的包络检测电路,由Schmit A电路和Schmit B电路,以及一些逻辑电路和或非门构成,其中名字相同的端口连接在一起,如Schmit A电路的VINP和Schmit B电路的VINP是连接在一起的.该包络检测器的正负阈值电压平均值和回差电压可以独立设定,而不取决于器件参数,即如图8所示正负阈值电压的平均值等于VR3-VR4或者-(VR3-VR4),回差电压等于2(VR1-VR2)/M.

图8 完整的包络检测电路Fig.8 Circuit for envelop detector

2 基于电路设计函数的USB2.0的包络检测器设计与仿真验证

式(10)给出了针对图7所示电路的抑制PVT变化的电路设计函数,因此施密特触发器和大部分串行通信系统的包络检测电路都可以按照此函数完成电路设计,下面以USB2.0设计为例,阐述整个设计过程.

对于USB2.0系统而言,系统要求的回差电压为50mV,即X=25mV,正负阈值电压的平均值Y=125mV,所以根据定义N=Y/X=5,由式(10)可得M=3或者M=3.3,取平均值M=3.15.根据第1节的分析,在电路设计时取VR1-VR2=78.75mV,VR3-VR4=125mV,这2个值可由基准电压提供,流过M13和M15的电流为16×Iref,M14的电流为9.9×Iref.差分对管的宽长比一致.

2.1 版图设计

在版图设计时,除了注意差分对管对称设计外,对于深亚微米工艺来说还要注意电流镜的匹配与噪声的影响,采用两个措施保证流过M13和M15的电流为16×Iref,M14的电流为9.9×Iref,首先在电路设计时设置MrefMOS管的Finger数为1,M13、M15的Finger数为16,版图设计时必须注意的是,M13或者M15的源漏极不能共用,否则电流复制会存在偏差,M14管可以是9个Mref和0.9个Mref组成.其次在模块版图四周设计2个隔离环,降低衬底噪声对电流镜复制电路的影响.

2.2 后仿真分析

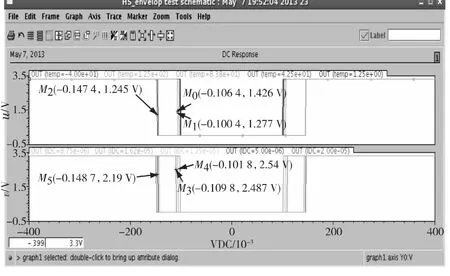

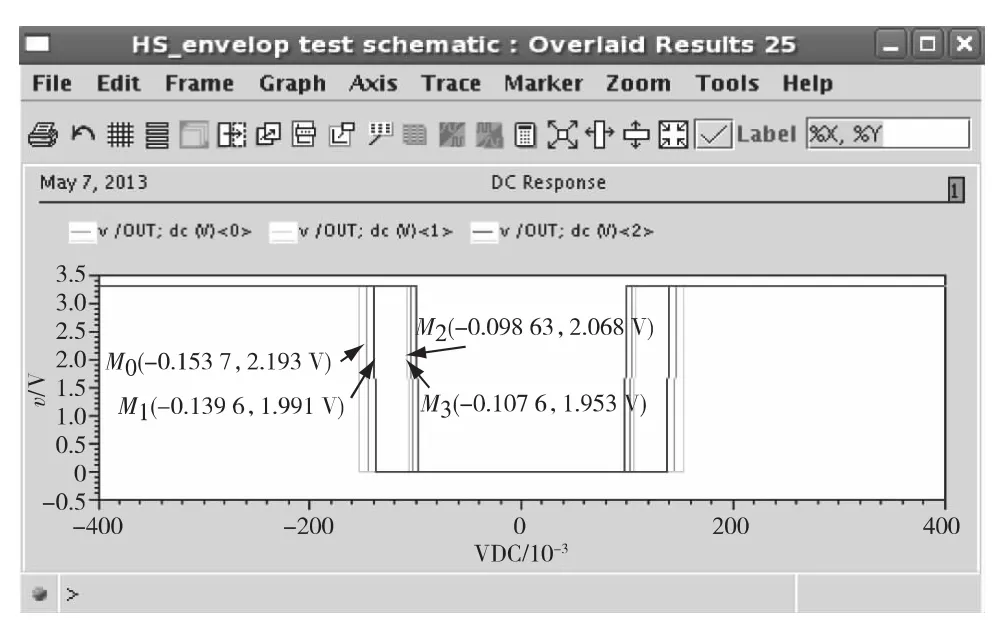

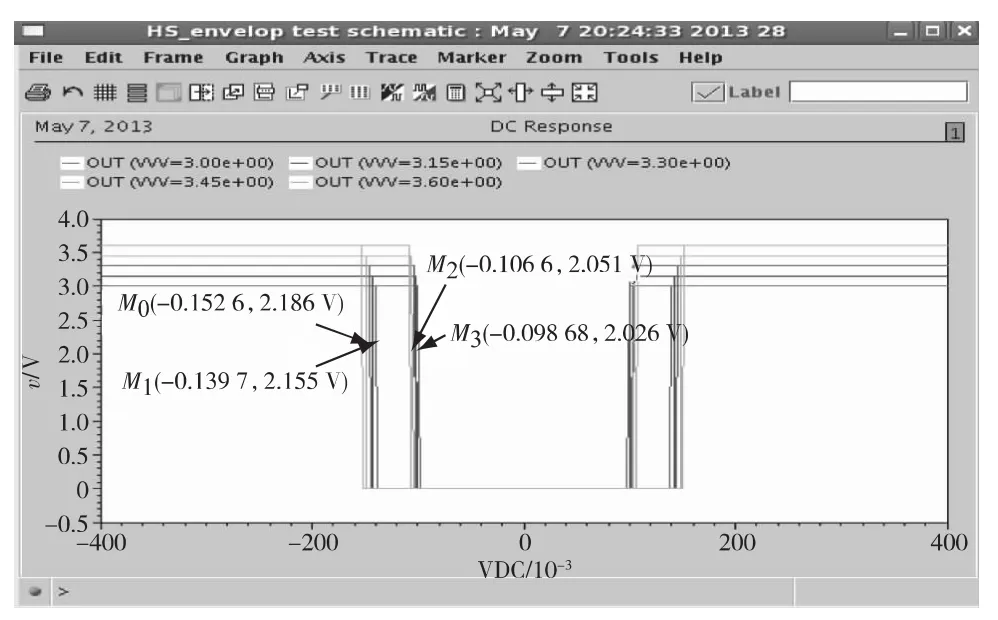

本次设计基于SMIC0.13μm CMOS工艺采用Spectre模拟仿真.图9模拟了温度从-45~125℃变化时,包络检测器的输出,从仿真结果看出负向阈值电压最大变化小于6mV,正向阈值电压最大变化1 mV;同时模拟了图6所示电路中偏置电流源Iref在5~20μA变化时,包络检测器的输出,从仿真结果看正负阈值电压偏差最大为8mV,该结果表明此结构具有非常好的温度抑制能力,同时表明偏置电流源Iref到温度影响较小.图10模拟了在电源电压3.3V条件下,工艺角变化时对包络检测器输出的影响,分别仿真了SS角、TT角、FF角3种情况,正向和负向阈值电压值最大变化仅为14mV,负向阈值电压最低位-98.6mV,最高为-153.7mV,满足 USB2.0要求.图11模拟了在TT角下,电源电压变化时对包络检测器输出的影响,即电源电压在3.0~3.6V时,正向和负向阈值电压最大变化13mV,负向阈值电压最低位-98mV,最高为-152.6mV.

从仿真结果看,当电路设计满足式(10)方程时,此类包络检测器对PVT变化和偏置电流源变化不敏感,无需外接校准电路,完全满足USB2.0的要求.

图9 温度和偏置电流Iref对包络检测器输出的影响Fig.9 The transmission characteristic curve by temperature and bias current Iref

3 结 论

基于1.8/3.3V0.13μm CMOS工艺设计了一类新颖的适用于串行通信的包络检测器电路,并推导出抑制PVT变化的电路通用设计函数.与传统的包络检测器不同的是按着电路设计函数设计的此类结构无需采用任何校准电路,就可以抑制工艺偏差、温度和电源电压变化引起的阈值电压和回差电压的变化,同时该包络检测器的正负阈值电压平均值和回差电压可以独立设定,不会相互影响.因此通用性极强.在此基础上设计完成了USB2.0的包络检测器,仿真结果表明工作温度从-40~125℃变化时,正向阈值电压变化小于1mV,负向阈值电压小于6mV,工作电压和工艺变化导致的阈值电压变化小于14mV,该结构完全符合USB2.0协议要求.同时也验证了其电路设计函数的准确性,此包络检测电路结构及其电路设计函数也可以应用到需要包络检测的串行通信系统中,或者其他需要施密特触发器的场合中.

图10 工艺角对包络检测器输出的影响Fig.10 The transmission characteristic curve by process conner

图11 电源电压对包络检测器输出的影响Fig.11 The transmission characteristic curve by voltage

[1]Intel Corporation.USB2.0transceiver macro cell interface(UTMI)specification[EB/OL].[2001-03-29].http:∥www.intel.com/technology-usb-download-2-0-xcvr-macrocell-1-05.

[2]Liu C H,Jose S.Squelch detection system for high speed data links:US,20080278227A1[P].2008-11-13.

[3]Jou S J,Kuo S H,Chiu J T,et al.A serial link transceiver for USB2.0high-speed mode[C]∥IEEE International Symposium on Circuits and Systems.Sydney:IEEE,2001:72-75.

[4]Nam J J,Kim Y J,Choi K H,et al.A UTMI-compatible physical-layer USB2.0transceiver chip[C]∥IEEE International SOC Confeence.Portland:IEEE,2003:309-312.

[5]Seth S,Thinakaran R,Chakraverty S,et al.A low power high speed envelope detector for serial data systems in 45nm CMOS[C]∥IEEE International Symposium on Circuits and Systems (ISCAS).Beijing:IEEE,2011:49-51.

[6]Wang Z.CMOS current schmitt trigger with fully adjustable hysteresis[J].Electronic Letters,1989,25(6):397-398.