一种伪随机控制的2ASK调制解调电路实现

2014-07-01潘玲佼任艳玲

程 钦,潘玲佼,任艳玲

(江苏理工学院电气信息工程学院,江苏 常州 213001)

1 伪随机序列与2ASK数字调制

1.1 伪随机序列

伪随机序列[1],也称为PN序列,m序列,是一种能够事先确定、可不断重复,具有二进制随机序列统计特性,广泛应用于通信领域的数字码序列。实现PN序列有多种方法,其中,用通用数字器件[2]构成m序列,速度快,但硬件电路修改不便,产生序列单一。用软件方式具有获得任意级数的本原多项式系数的特点,但速度受限。使用FPGA电路开发[3],能够有效节约设计时间,减少PCB板占用,使系统变得可靠,并且能进行灵活设计,可实现较大规模的通信电路。

1.2 2ASK调制与解调

二进制振幅键控(2ASK)是一种利用载波幅度变化来传递数字信息的二进制数字信号调制方式,它是研究其他数字调制技术的基础。2ASK时域表达式为

2ASK调制波形如图1所示,通过载波幅度变化作为控制信息,频率和初始相位不变。载波的幅度变化对应二进制信息的符号“0”或“1”。产生2ASK信号的方法包括模拟法和键控法两种,如图2所示。

图1 2ASK调制波形

图2 2ASK调制方法

2ASK解调方法包括两种:相干解调和非相干解调,接收系统如图3所示。2ASK解调部分增加抽样判决电路,有利于提高数字信号接收性能。

图3 2ASK解调方法

2 伪随机控制2ASK系统软件设计

2.1 DDS程序设计

载波信号源发生器采用直接数字式频率合成器(DDS),DDS采用全数字技术处理[4],输出频率和相位和幅度能够在微控制器控制下准确快速变换。DDS设计程序流程图如图4所示,其中,26位累加器对输出的频率控制字进行累加,取26位累加器的的第20到第26位作为ROM地址,在clk驱动下对存储一个周期128点的正弦波ROM寻址。

图4 DDS程序流程图

图5 m序列程序流程图

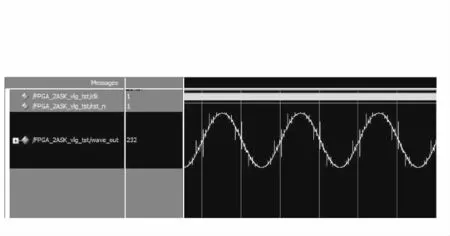

DDS输出正弦波时序仿真波形如图6所示。第1个信号是50MHz系统时钟clk,第2个信号是复位信号rst_n,第3个信号是输出波形wave_out,是ROM 的10KHz输出载波。

图6 DDS输出正弦波时序仿真波形

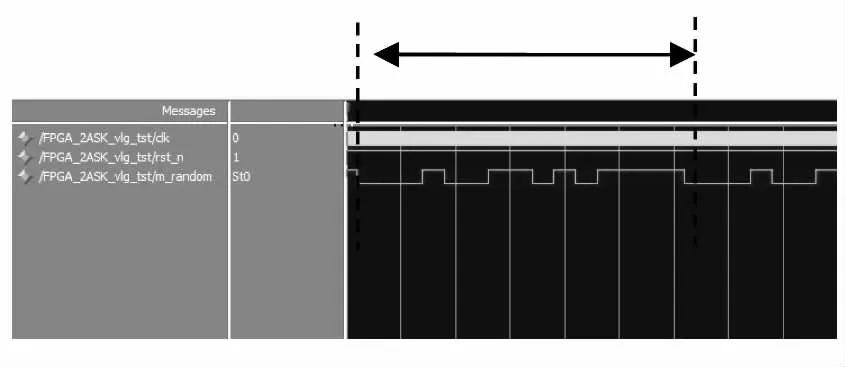

图7 m序列仿真图

2.2 伪随机序列发生器设计

伪随机序列发生器设计中,当线性反馈逻辑的移位寄存器设置各级初始状态之后,每次经过时钟信号,移存器的状态随之改变。到最后一级的输出,通过下个时钟周期产生一个新序列。设计采用了4级移位寄存器用于产生周期长度为15的m序列。线性反馈逻辑遵从式2的递归关系:

第1级与第2级输出进行模2运算并将结果反馈到第4级。假设4级移位寄存器的初始状态为0001,那么通过移位时钟信号,移位寄存器各级状态随之改变,软件设计流程见图5。

如图7为m伪随机序列模块波形图,图中第1个信号clk是50MHz系统时钟信号,第2个信号rst_n是低电平复位信号,第3个信号m_random输出周期为15位的m伪随机序列“000100110101111”。

3 伪随机控制2ASK电路设计

3.1 ASK系统调制电路

ASK调制框图如图8所示,包括产生10KHz正弦载波信号的DDS载波模块,m随机序列模块,受控开关根据m序列控制载波输出,再将输出的数字波形经过数模转换得到调制后的模拟波形,最后经过低通滤波器,得到已调信号。

图8 ASK实现框图

图9 ASK的仿真波形图

图10是ASK调制RTL级图。图中DDS_inst对应DDS模块,包括3个信号端口,clk为输入50MHz系统时钟,rst_n为系统低电平复位信号,wave_out为输出波形的数字量,m_randomsquen_inst对应m随机序列产生模块,也包括3个信号,clk和rst_n信号和DDS模块相同,level1信号即输出m随机序列,MUX21对应模拟开关,在SEL控制下选择OUT0=DATAA(=8’h7F)或者OUT0=DATAB(DATAB连接wave_out)。调制信号经过D触发器锁存输出。

图10 ASK的RTL级联图

调制仿真波形从图9中可以看出,当m随机序列为1时调制后的输出信号为10KHz的载波,当m随机序列为0时调制后的输出信号为0。

3.2 ASK系统解调电路

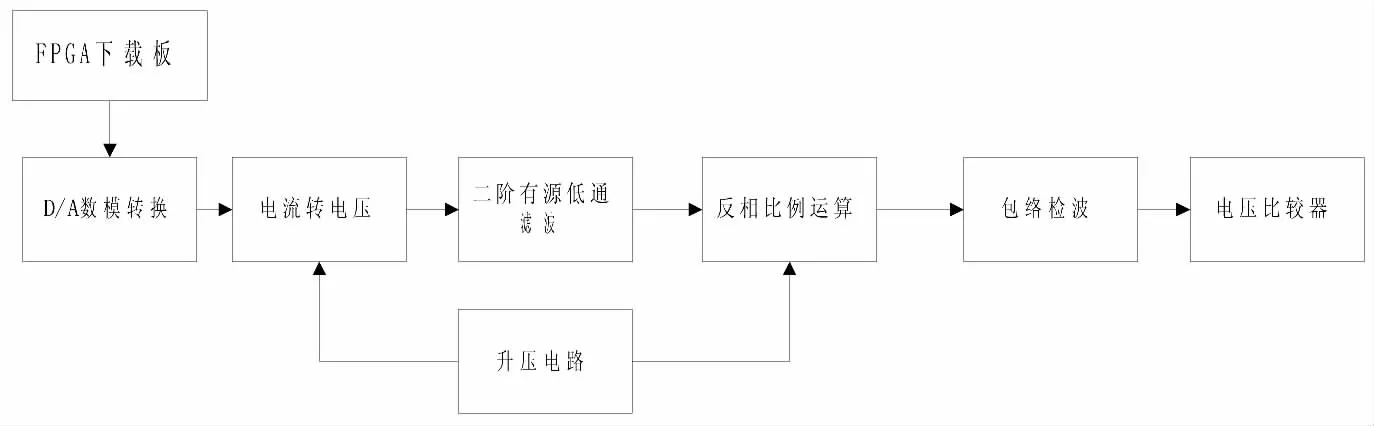

通过D/A转换芯片接收FPGA数据,再将产生的电流信号转换为电压信号,从而得出电压模拟信号。电路中的高频成分经过低通滤波器去除得到纯净的低频

信号。最后进行包络检波并整形得到解调输出波形。如图11所示。

3.3 单元电路设计分析

图11 解调系统框图

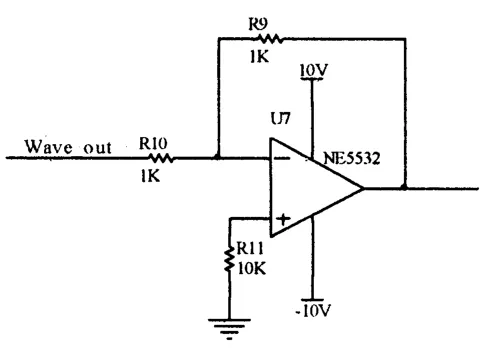

数模转换电路:FPGA进行ASK调制后输出数字波形,需要经过DAC0832芯片转换为模拟量,DAC0832芯片转换结果采用电流形式输出。为了得到模拟电压信号,就要使用一个高输入阻抗的线性运算放大器来转换。运放的反馈电阻不仅能用RFB端引用片内固有电阻还能够使用外接。为了将DAC0832芯片变化得到的模拟电流值变为模拟的电压值,在DAC0832芯片的输出端接了由运放NE5532构成的电流转电压电路。

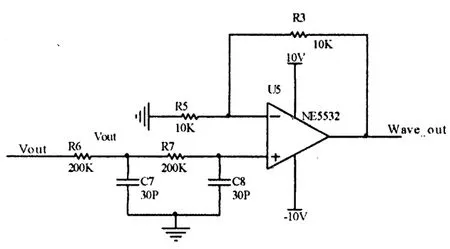

二阶有源低通滤波器:采用运放NE5532,其截止频率设计为10KHz,载频信号频率是10KHz。二阶有源低通滤波器如图12所示。将R=200KΩ,C=30pF带入式计算得f0=26.54KHz。

将f0=26.54KHz带入式fp=0.37f0计算得二阶低通滤波器的通带截止频率fp=9.82KHz。因为经过电流转电压电路图,将DAC0832输出的电流转为的是负电压,所以需要接个反向比例运算电路将负电压转为正的,如图13为由NE5532构成的反相比例运算电路,其比例为-1。

图12 二阶有源低通滤波器

图13 反相比例电路

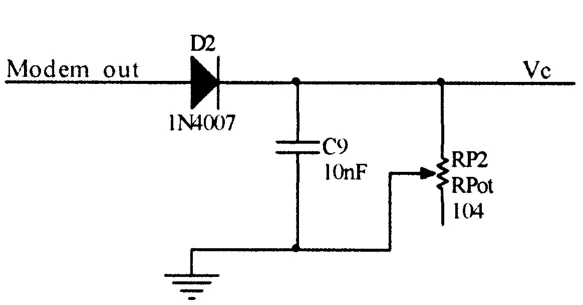

包络检波电路:由半波或全波整流器和低通滤波器构成,属于非相干解调,无需相干载波。包络检波电路电阻R和电容C应该满足式3的要求。

式中:fH是调制信号的最高频率;fc是载波的频率。设计中fH为5KHz,vc为10KHz,C为10nF,经过计算得R的取值范围为:10 KΩ<<R<<20 KΩ,即图14中的RP2的调节范围为10KΩ到20KΩ。

图14 包络解波电路

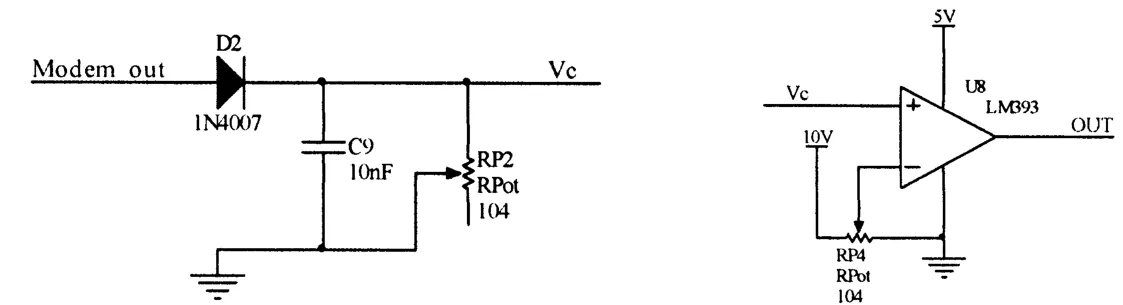

图15 电压比较器

为得到性能较好的解调波形,还在包络检波输出加了个电压比较器,如图15所示。比较器采用LM 393芯片。图14中RP4是100 KΩ的电位器。将包络检波输出的Vc和RP4分得电压做比较,使输出的解调波形边沿陡峭。

升压电路和负电源电路:系统输入电压5V,因为需要±10V给运放NE5532供电,所以需要将5V升压到10V。设计中采用LM 2577-ADJ升压芯片。由于NE5532需要提高正负电压,所以要设计负电压电路供电。选用UCL7660芯片。

4 结果测试及分析

分别测试ASK硬件电路m序列产生,ASK调制输出和ASK解调输出各点波形。图16和图17分别为输入伪随机序列与ASK已调信号,输入伪随机序列与解调输出信号波形图。从图中可见调制波形能够正确反映伪随机序列的变换规律,解调结果与输入伪随机序列保持一致,验证了电路设计的可行性。下一步工作将在该电路基础上,考虑采用混沌信号代替伪随机码序列,从而能够进一步增强系统的保密性,有利于ASK电路更广泛的应用。

图16 m序列和调制信号波形

图17 m序列和解调信号波形

[1]樊昌信,曹丽娜.通信原理[M].6版.北京:国防工业出版社,2008.

[2]朱幼莲.数字电子技术[M]北京:机械工业出版社,2011.

[3]潘松,黄继业.EDA 技术与 VHDL[M].2版.北京:清华大学出版社,2007.

[4]高银,林其伟.DDS数字移相正弦信号发生器的设计[J],华侨大学学报:自然科学版,2009,30(1):34-37.