基于CPLD的高精度可调脉冲信号发生器研制

2014-06-21樊多盛施韶华李孝辉

樊多盛,施韶华,李孝辉

基于CPLD的高精度可调脉冲信号发生器研制

樊多盛1,2,3,施韶华1,2,李孝辉1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院时间频率基准重点实验室,西安 710600;3. 中国科学院大学,北京 100049)

为满足精密时间间隔测量设备的测试需要,研制了一种时间间隔可调的高精度脉冲信号发生器。利用计算机串口控制的方式,结合复杂可编程逻辑器件(CPLD)集成度高、可靠性好及工作速度快的优点,采用Altera公司的设计软件Quartus II进行设计仿真及实现。仿真与实测实验表明,该脉冲信号发生器不仅可以产生单路可调脉冲信号,而且能产生多路可调脉冲信号,产生的单路秒脉冲信号的1s取样Allan方差为1.84×10-11;产生的时间间隔为100 ns的多路脉冲信号的1s取样Allan方差为2.36×10-11,2路信号之间的时间间隔数据系列的峰-峰值为101ps,可以满足多通道时间间隔测量设备测试要求的稳定度与准确度。

脉冲信号发生器;复杂可编程逻辑器件(CPLD);时间间隔

0 引言

在评估测试多通道时间间隔测量设备时,需要一个稳定性好准确度高的时间间隔可调的脉冲信号发生器[1-3]。然而,目前市场上大部分脉冲信号发生器的稳定度与准确度及通道数量不满足产生测试信号的要求。

本文研制的高精度可调脉冲信号发生器,是在外部提供参考信号(如常见的5,10,100 MHz等)的条件下,使用可编程逻辑器件CPLD实现的多路可调脉冲信号发生器,可为多通道时间间隔测量设备提供测试信号。

1 工作原理

脉冲信号发生器是基于预置累加计数器而产生的。在预置计数器中,当测量结果超出某个数值(基数)时,预置计数器将输出一个电压信号。首先给计数器设置一个基数,当外部周期性参考信号到来时,该计数器便开始累加计数,当计数值超出预置的基数时,便输出一个脉冲信号。通过外部实时发送数据改变计数器的基数,即可实现频率可调的单路脉冲信号。对于多路脉冲信号,是给计数器设置多个基数,用同一个计数变量对参考信号进行累加计数,当计数变量超出其中一个基数时,便输出一个脉冲信号,从而产生多路脉冲信号。当然,计数变量有限制范围,超过最大限制范围,便开始下一次计数。同理,改变其特定的基数,可实现多路脉冲之间的时间间隔的实时可调性[4-6]。脉冲信号发生器脉冲输出示意图见图1。

图1 脉冲信号发生器波形图

当外部输入10 MHz的参考方波信号,对其上升沿进行计数,当计数到9 999 999时,CPLD输出一个脉冲信号,以此实现秒脉冲信号。通过计算机RS232接口向CPLD发送数据,使计数基数为999 999,从而调节脉冲信号的频率,实现百毫秒脉冲信号。其他单路脉冲信号,以此类推[7-9]。

对于多路脉冲信号,在同样外部参考情况下,若设置其中一个基数为9 999 999,另外一个基数为9 999 998,便可产生时间间隔为100 ns的两路脉冲信号;若改变基数9 999 998为9 999 996,两路脉冲信号的时间间隔可实时变成300 ns。总之,通过计算机串口改变计数基数,可实时调整多路脉冲信号之间的时间间隔[10-11]。

2 总体实现方法

可调脉冲信号发生器的核心器件是CPLD,包括接收器与计数器的设计。计算机通过RS232接口连接至CPLD,实时发送一定格式的数据,实现对其输出单路脉冲信号频率及多路脉冲信号之间时间间隔的有效调节控制,通过外部选择按钮选择单路脉冲输出还是多路脉冲输出。50MHz晶振为CPLD的异步串口接收提供参考信号。在输入参考信号的条件下,通过计算机实时控制,CPLD输出单路可调脉冲信号或多路可调脉冲信号。输入参考信号,作为对CPLD的激励信号,可以是10,20,100 MHz等。输出的单路脉冲信号是指常见的秒脉冲、毫秒脉冲、微秒脉冲等。多路可调脉冲信号,在CPLD的I/O口允许条件下,可以根据测试信号要求,同时输出任意路脉冲信号,其时间间隔的范围受限于外部参考信号与给计数器设置的最大基数。该系统结构见图2。

图2 系统结构图

该系统能实现单路脉冲信号输出或同时输出8路脉冲信号,脉冲路数根据测试要求进行选择。脉冲最小时间间隔是外参考输入信号的一个周期,脉冲最大时间间隔取决于计数器,脉冲信号的稳定性与准确度主要取决于参考信号的性能。

3 CPLD实现

3.1 CPLD的硬件电路设计

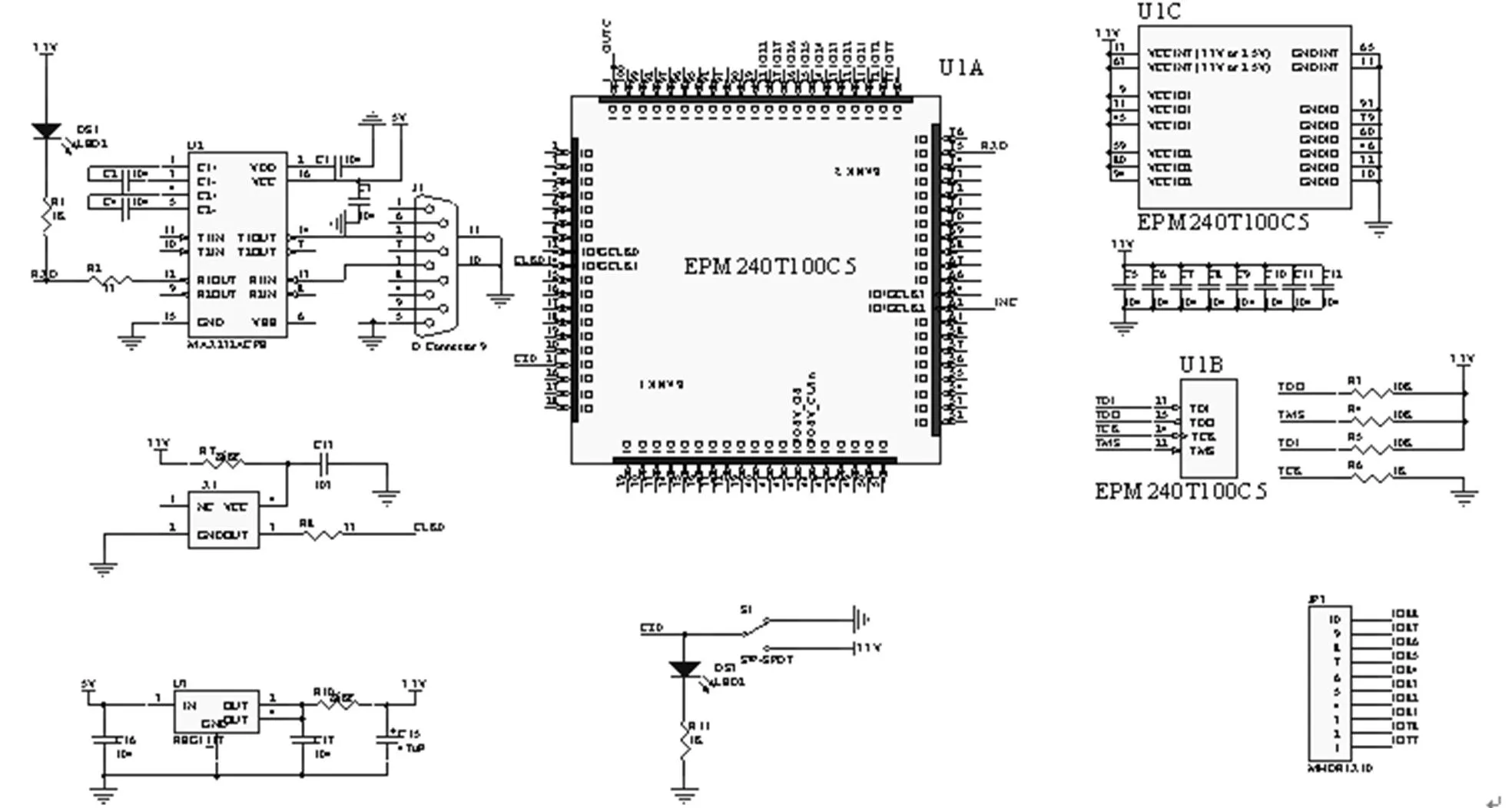

硬件电路设计,主要是实现CPLD的外围电路,包括串口接收处理与控制电路和电源电路等。

在硬件电路设计中,选用的CPLD是Altera公司MAX‖系列EPM240T1005C,该芯片具有低功耗、高速度以及高速I/O计数等性能,是业界普遍使用、性能稳定、低功耗且性价比高的一款可编程逻辑器件[12-13]。

脉冲信号发生器输出信号的时间间隔是通过计算机来控制的,可以采用串行接口、PS/2、USB或无线通信接口等实现计算机与CPLD之间的通信,本设计中采用常见的串行接口[4]。串行通信接口采用RS-232C标准,为单向不平衡传输方式,以负逻辑规定逻辑电平,即逻辑1表示为信号电平-5~-15 V,逻辑0表示为信号电平+5~+15 V,最大传送距离15 m,最大传送速率20 kbit/s。平时线路保持为1,传送数据开始时,先送起始位(0),然后传8(或7,6,5)个数据位(0,1),接着可传1位奇偶校验位,最后为1~2个停止位(1),由此可见,传送一个ASCII字符(7位),加上同步信号最少需9位数据位。

串行通信,一般采用专用芯片来协调处理串行数据的发送接收,称为通用异步发送/接收器(UART),以节省CPU的时间,提高程序运行效率。该系统中采用MAX232芯片来处理串行通信[14]。

在系统板上,MAX232工作时需5V电源,而EPM240T1005C工作时需要3.3 V电源。在外部提供5 V电源的前提下,采用REG1117M3电源转化芯片将输入5 V转为3.3 V,从而实现整个系统的供电。高稳定的精密电源对系统的稳定度和准确度有极大的影响,故系统电源需特殊处理与保护,即对CPLD的供电电源须进行电容滤波。若将芯片MAX232换为MAX3232芯片,电源供电电压就统一为3.3 V,因而使设计更加简洁。系统硬件电路图见图3。

图3 系统硬件电路图

在图3中,为便于表示,将EPM240T1005C(CPLD)分为U1A,U1B及U1C3个部分,其中U1A为芯片的输入输出端口,U1B为芯片的下载端口,U1C为芯片的电压部分。CPLD的IO76端口(RXD为连接标识)通过MAX232芯片与外控计算机连接;CPLD的IO64端口(INC为连接标识)为外部参考信号输入端;CPLD的IO1端口及IO77~IO88端口为脉冲信号输出端;CPLD的IO20端口(CZ0为连接标识)为外部选择端口;50 MHz晶振X1通过CLK0连接到CPLD的IO20端,外部5 V电源通过REG1117转换为3.3 V电源,为CPLD提供电压。其硬件电路实现图见图4。

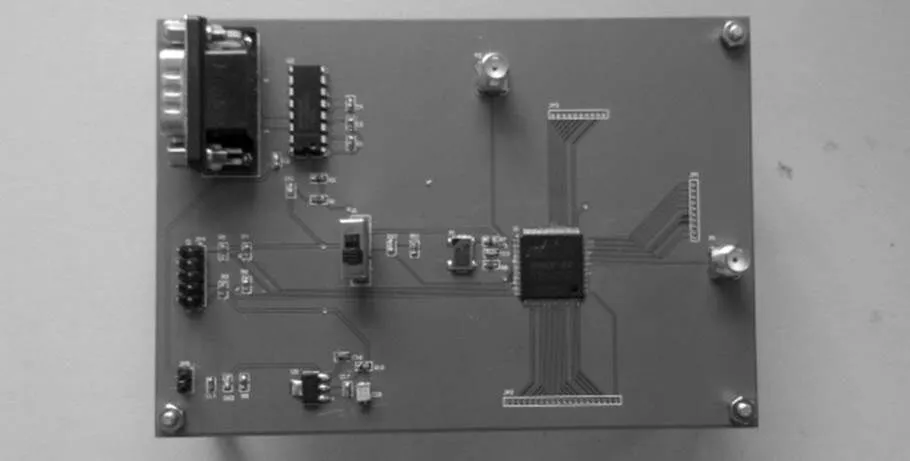

图4 硬件电路实现图

3.2 软件设计

软件设计的任务是基于计算机开发软件平台在CPLD上实现计数器与串口接收器等。

CPLD是超大规模可编程逻辑器件,实现编程常用的硬件电路描述语言有VHDL与Verilog HDL,本设计采用VHDL语言。VHDL语言是美国IEEE标准协会于1987年公布的通用工业标准硬件描述语言,1995年,我国将VHDL作为EDA硬件描述语言的国家标准,用语言的方式而非图形等方式描述硬件电路[15]。

VHDL主要用于描述数字电路系统的结构、行为、功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格十分类似于一般的计算机高级语言。使用该语言,端口设计方便,易实现设计思路,不仅可以采用自顶向下设计流程,也可以采用自下向上的设计方案。

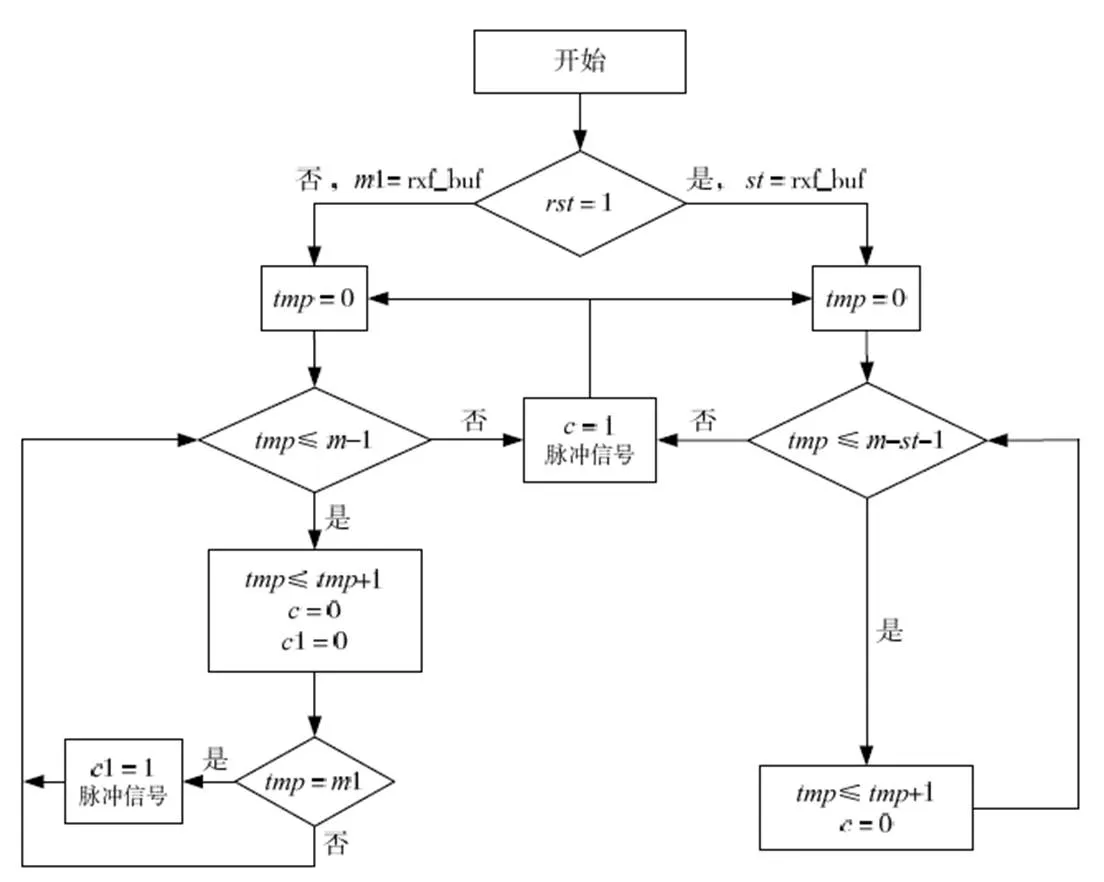

软件设计中的关键部分是计数器,计数器的设计思路直接决定了脉冲信号的稳定度与精度。经过多次实验设计与仿真,发现采用十进制整数计数或直接调用库函数计数器等,误差都比较大,最后决定采用32位的位累加计数器,误差非常小、稳定可靠、设计思路简洁且能实现设计目标。具体软件设计流程见图5。

注:rst表示单路脉冲信号还是多路脉冲信号,m表示基数(初始化设置),m1表示另外一个基数(串口接收数据),st 表示用于设定单路时脉冲信号的频率(通过串口获得数据),tmp表示计数变量,c,c1表示输出的2路脉冲信号。

文中的专用接收器是在CPLD上编程实现的。CPLD上的接收器接收来自计算机的数据,需要外部提供参考时钟信号。在本系统中,串口软件发送数据的发送速率选取为9 600 bit/s,因此在设计串口接收器时,为便于分频,选用50 MHz的晶振作为参考信号。

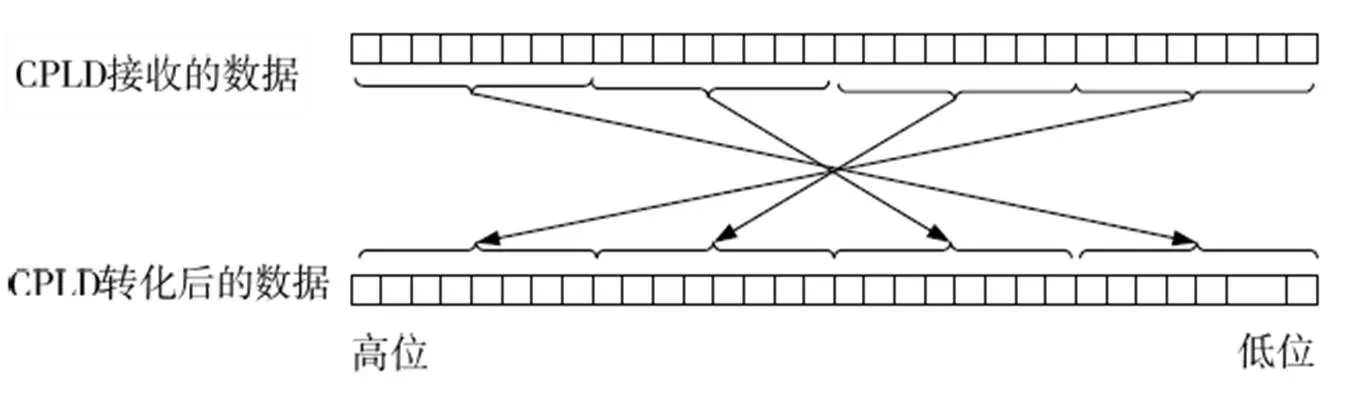

在CPLD串口接收器(UART)设计方面,其接收数据格式的转化是指 CPLD与计算机之间交互的数据格式转化。计算机串口软件发送数据格式是按字节的方式,且对于多位数据,先发低位再发高位。而CPLD接收数据时,是按照位的方式接收,且接收的数据是按照从低位到高位存储。因此,CPLD接收的计算机串口数据需要转化后才可使用。又计算机串口软件发送一个字节,仅能发送一位十进制数,而这个字节高四位与该数无关,但该高四位在CPLD中需占用逻辑单元,造成资源浪费。因此,计算机串口软件采用十六进制的方式发送数据。所需发送的十进制数据在发送前需要转化为十六进制格式。根据计数器的设计,CPLD只能接收8位十六进制数据,字长为4字节的32位二进制数,数值的范围为0~4 294 967 295。因此,为了准确控制脉冲信号相位,计算机串口软件每次必须发送8位十六进制数据。图6是CPLD数据格式转化示意图。

图6 CPLD数据格式转化示意图

4 仿真实验

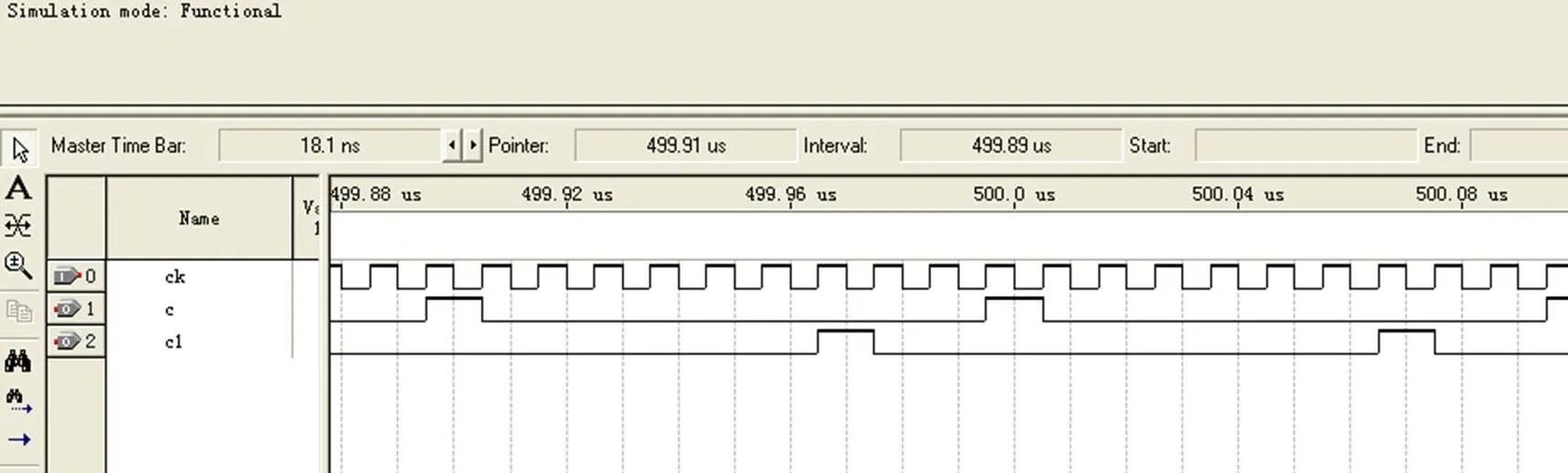

仿真实验是在Quartus II 9.0软件平台上进行的,该设计平台在实现软件设计的同时还提供了丰富的其他功能,如仿真、时序分析与逼近、功耗分析及调试等,这极大地缩短了设计周期,提高了开发效率,而且该功能仿真与实际电路实现功能相比误差较小。此外利用该平台还可实现JTAG下载等。本文选取的仿真实验是指功能仿真实验。设置参考信号为100 MHz,基数为9时,其单路输出为百纳秒脉冲信号,仿真图见图7。在同样的外部输入参考信号下,设置一个基数为9,另外一个基数为7,即多路脉冲信号之间的时间间隔为70 ns,其多路脉冲信号仿真实验图见图8。

在仿真实验中,表示参考信号,与1表示输出脉冲信号。由图7、图8可以看到,输出脉冲信号的宽度为输入信号的一个周期,输入信号上升沿与输出信号上升沿是同步的,没有毛刺与相位差,这说明了本设计中选取位累加计数器的方案是正确的。

图7 单路脉冲信号仿真图

图8 多路脉冲信号仿真图

5 测试实验

5.1 单路脉冲信号测试实验

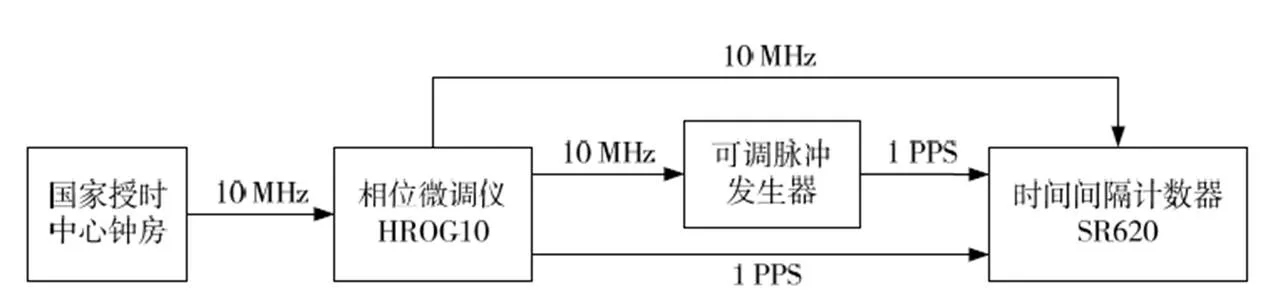

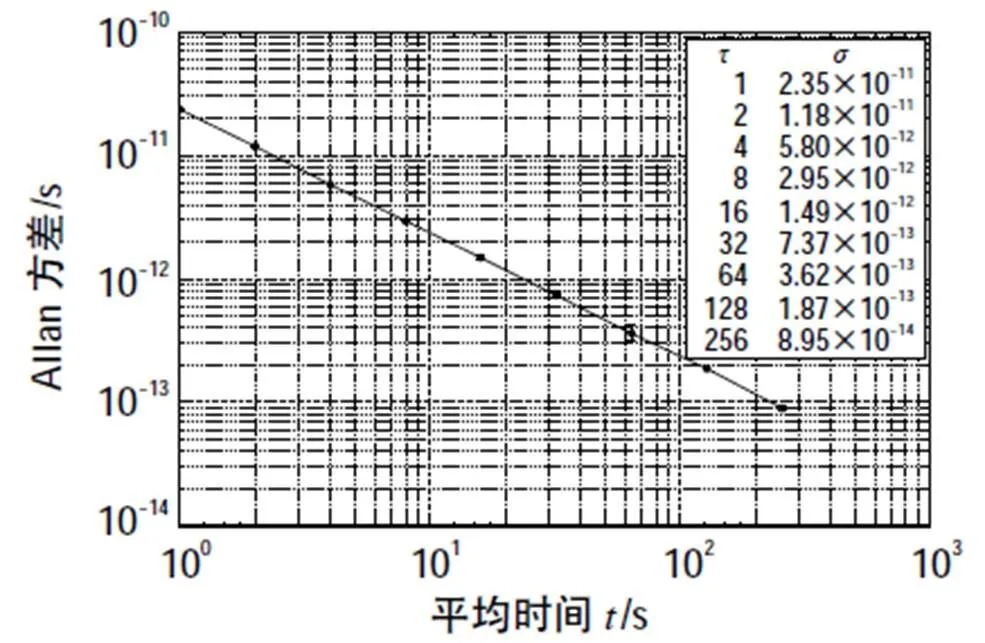

在系统单路测试实验中,首先将中国科学院国家授时中心UTC(NTSC)主钟的10MHz信号作为HROG10(相位微调仪)的外部参考信号,由HROG10输出高稳定度的10 MHz信号,将HROG10输出的10MHz信号提供给基于CPLD的高精度可调脉冲信号发生器,由该脉冲信号发生器产生单路脉冲信号,最后,使用时间间隔计数器SR620测量HROG10输出1PPS与该脉冲信号发生器产生的秒脉冲的时间间隔,对该可调脉冲信号发生器产生单路脉冲信号的稳定性和准确度进行评价。单路脉冲信号测试框图见图9。曾于2012年11月1日00:00到04:00每秒取一个数据,共采样14 000个数据,由取样数据计算得到该可调脉冲信号发生器产生秒脉冲信号的1 s取样Allan方差为1.84×10-11,见图10。

图9 单路脉冲信号测试框图

图10 Allan方差

5.2 多路脉冲信号测试实验

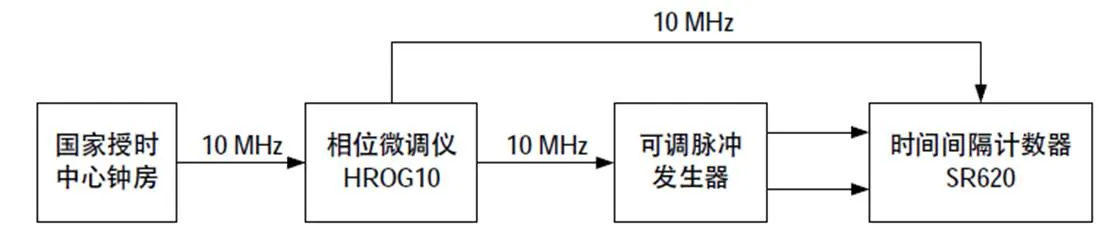

在系统多路测试实验中,将国家授时中心UTC(NTSC)主钟的10 MHz信号作为HROG10(相位微调仪)的外部参考信号,由HROG10输出高稳定度的10 MHz信号,将HROG10输出的10 MHz信号提供给基于CPLD的高精度可调脉冲信号发生器,由该脉冲信号发生器产生多路脉冲信号,最后,使用时间间隔计数器SR620测量该脉冲信号发生器产生的2路脉冲信号的时间间隔,对该可调脉冲信号发生器产生的多路脉冲信号的稳定度和准确度进行评价。多路脉冲信号测试原理框图见图11。

图11 多路脉冲信号测试框图

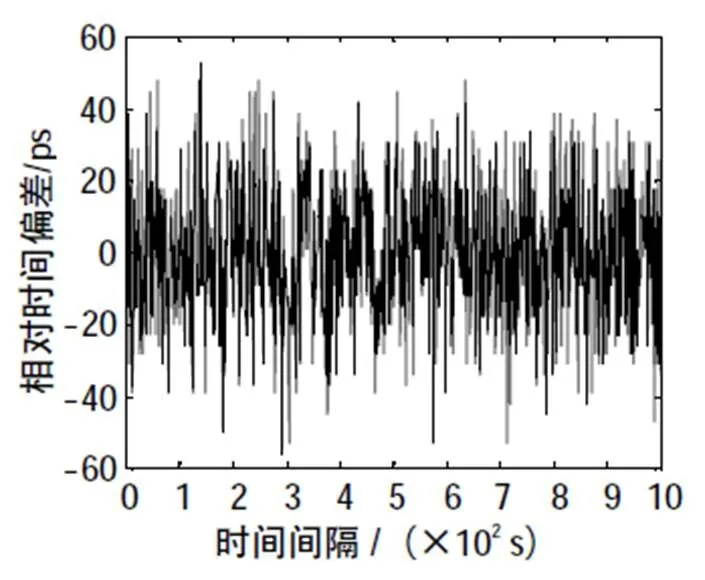

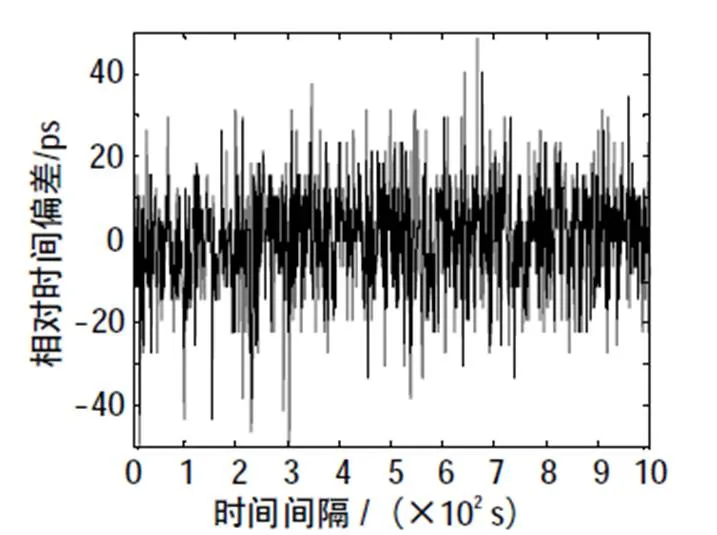

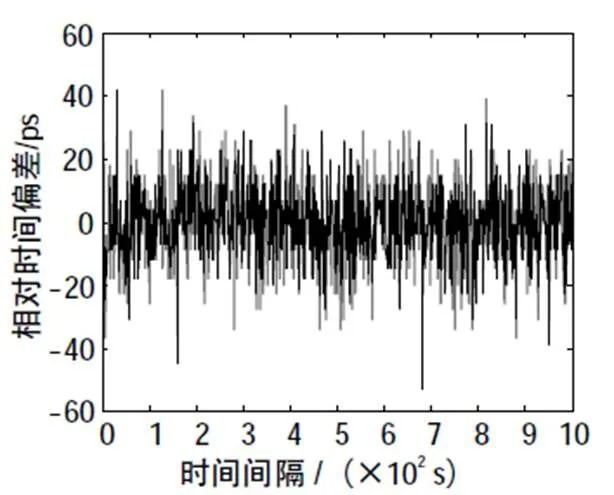

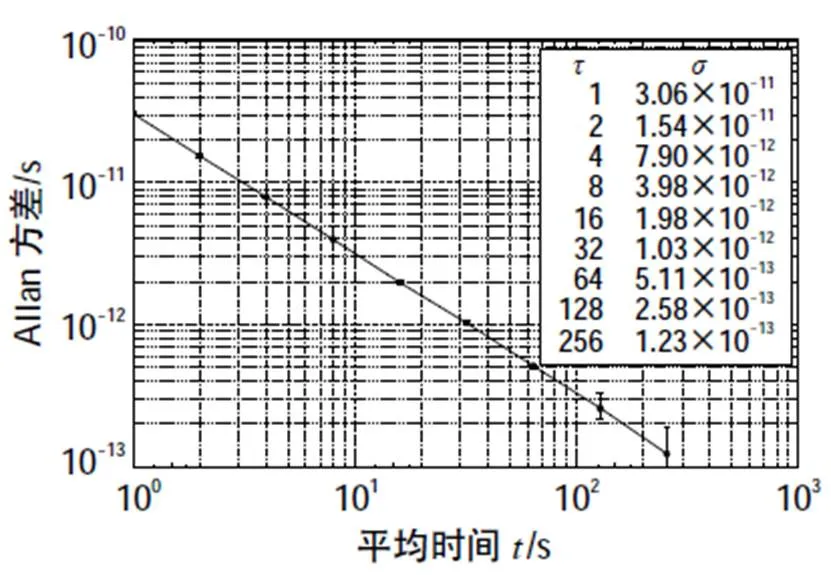

取2路脉冲信号的时间间隔分别为10 s,1 s,100 ms,10 ms,1 ms,100μs,10μs,1μs,500 ns,200 ns和100 ns,进行测量。测量所得各个时间间隔相对偏差(2路信号之间的时间间隔与标准值之差)的均值、2路信号之间的时间间隔数据系列的峰-峰值和1 s取样的Allan方差值见表1。以2路脉冲信号的时间间隔为1 s,100 ms,1μs及200 ns的情况为例绘制相对时间偏差图和Allan方差图,分别示于图12至图15和图16至图19。

表1 测量结果

图13 时间间隔为100 ms的相对时间偏差

图14 时间间隔为1 ns的相对时间偏差

图15 时间间隔为200 ns的相对时间偏差

图16 时间间隔为1 s的Allan方差

图17 时间间隔为100 ms的Allan方差

图18 时间间隔为1 μs的Allan方差

图19 时间间隔为200 ns的Allan方差

在测量中,信号电缆时延差为5.59963 ns,另外有BNC接头时间差、硬件电路走线时间差及随机误差等,故从表1看出,该可调脉冲信号发生器产生脉冲的时间间隔是准确的,最小时间间隔取决于外部参考信号,最大时间间隔取决于硬件计数器的最大基数。表1及图12至图15、图16至图19表明,该可调信号发生器产生的脉冲信号是稳定可靠的。

6 结论

本文研制的基于CPLD的高精度可调脉冲信号发生器充分利用了CPLD数字器件及VHDL语言的优点,设计清晰简洁,控制灵巧方便。它可以为多通道时间间隔测量设备提供单路可调的测试脉冲信号或多路可调的测试脉冲信号,在评估测试多通道时间间隔测量设备试验中得到了具体应用。通过实验测试证明,该可调脉冲信号发生器准确性好、稳定度高、性价比高、应用前景广阔。若使用精密专业供电电源,该可调脉冲信号发生器的性能会更加稳定。另外,若将计算机控制改进为微系统(单片机或FPGA等)控制,可调脉冲信号发生器便可微型化,方便测试使用。

[1] 李孝辉, 杨旭海, 刘娅, 等. 时间频率信号的精密测量[M]. 北京: 科学出版社, 2010.

[2] 施韶华, 李孝辉, 张慧君. 基于TDC-GPX的多通道时间间隔测量系统设计[J]. 仪器仪表学报, 2009, 30(S10): 252-256.

[3] 辜新宇, 郭际, 施韶华, 等. 多通道精密时间间隔测量系统的研制[J]. 电子测量与仪器学报, 2013, 27(1): 69-75.

[4] 张正, 董绍武, 张敏. 一种基于FPGA的多种波形发生器的设计[J]. 时间频率学报, 2008, 32(2): 133-136.

[5] 陈建, 白永林, 程光华, 等. 基于MCU和CPLD的嵌入式可调脉冲信号发生器设计[J]. 电子器件, 2007, 30(4): 1249-1251.

[6] 张良, 秦玲, 刘承俊, 等. 多通道可调脉宽脉冲发生器设计[J]. 电子技术应用, 2007(5): 29-31.

[7] 王冲, 霍正军, 羊天德, 等. 基于CPLD的雷达脉冲发生器的设计[J]. 计算机工程与设计, 2007, 28(13): 3172-3181.

[8] 杜继业, 董静然, 宋顾周. 一种脉宽可调的高压脉冲发生器的研究与设计[J]. 核电子学与探测技术, 2010, 30(8): 1046-1049.

[9] 王奎龙. 基于LabVIEW的多路时序控制脉冲发生器设计[J]. 现代电子技术, 2009, 307(20): 181-195.

[10] 谢东东, 吴侠义, 禹卫东. 一种多通道星载SAR通道间一致性精确测量方法[J]. 电子测量与仪器学报, 2012, 26(5): 379-384.

[11] 田芳宁, 孙国强. 脉冲信号发生器自动测试系统设计[J]. 国外电子测量技术, 2011, 30(3): 44-45.

[12] 曾繁泰, 陈美金. VHDL程序设计[M]. 北京: 清华大学出版社, 2001.

[13] 潘松, 黄继业. EDA技术实用教程[M]. 北京: 科学出版社, 2005.

[14] 郭俊香, 曹领. RS-232C接口及其使用[J]. 仪器仪表用户, 2007(1): 27-28.

[15] 刘玉钦, 吴国强. 运用VHDL实现数字信号处理[J]. 电子测量与仪器学报, 2008, (S2): 145-148.

Development of an adjustable high-precision pulse signal generator based on CPLD

FAN Duo-sheng1,2,3, SHI Shao-hua1,2, LI Xiao-hui1,2

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China; 2. Key Laboratory of Time and Frequency Primary Standards, National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China; 3. University of Chinese Academy of Sciences, Beijing 100049, China)

To meet the test requirement of the precise time interval measurement equipments, we designed a phase-adjustable high-precision pulse signal generator. In the design, simulation and hardware-implementation, the computer serial port control mode was adopted, the complex programmable logic device (CPLD), which has the advantages of high level of integration/good reliability/fast operating speed, was utilized, and the Altera's Quartus II software was adopted. The result of simulation and experiment shows that the pulse signal generator can not only generate a single adjustable pulse signal, but also generate the multi-channel adjustable pulse signals. The Allan(=1s) for the single 1PPS signal is 1.84×10-11, the Allan variance(=1s) for the multi-channel pulse signals with a time interval of 100 ns is 2.36×10-11, and the peak-peak value of the time interval data series for two channels of signal is 101ps. This pulse signal generator can meet the needs of the multi-channel time interval measurement equipment in stability and accuracy.

pulse signal generator; CPLD(complex programmable logic device); time interval

TN782

A

1674-0637(2014)01-0025-09

2013-04-22

国家自然科学基金资助项目(61001076);国家重大科研仪器设备研制专项资助项目(61127901)

樊多盛,男,硕士研究生,主要从事高精度时间频率测量与控制研究。