基于DDS技术的Loran-C信号源的杂散信号抑制的分析与实现

2014-06-21皇甫江华宇李实锋

皇甫江,华宇,李实锋

基于DDS技术的Loran-C信号源的杂散信号抑制的分析与实现

皇甫江1,2,3,华宇1,2,李实锋1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院大学,北京 100049)

采用直接数字频率合成(DDS)技术设计的Loran-C信号源,具有输出杂散多且难以预测的缺点。基于对DDS基本原理的研究分析,针对DDS输出信号存在的相位舍位杂散问题,对其关键部位的相位累加模块进行优化设计,并基于FPGA技术,在QuartusⅡ环境下完成了对Loran-C信号源的实现与仿真验证。结果表明,通过优化的设计算法能够产生失真小,稳定度好的输出波形,从而验证了该方法抑制杂散的有效性与可行性。

罗兰-C;直接数字频率合成;相位舍位杂散;相位累加;现场可编程门阵列(FPGA)

0 引言

Loran-C信号源是Loran-C信号产生设备,其在Loran-C系统建设和Loran-C接收机研制与应用中占有重要的地位[1]。直接数字频率合成(DDS,direct digital frequency synthesis)作为第三代频率合成技术,是从相位概念出发直接合成所需波形的一种新型频率合成技术,它具有频率转换快、分辨率高、频率合成范围宽、相位噪声低等优点[2-3]。随着微电子技术和数字集成电路的迅速发展,以及工程的实际需要,DDS技术越来越显现其某些性能优于传统的频率合成技术,使得DDS成为优秀的现代波形合成技术。本文借助DDS技术对Loran-C台链信号的合成进行研究与设计,为研制高性能Loran-C信号模拟源奠定基础。然而DDS由于固有的输出杂散多且难于预测,成为制约其发展应用的一个瓶颈[4],加之各类电子系统对信号源的要求越来越高,如何抑制DDS输出信号中的杂散成分也就成了系统设计研究的重点。对此,文章在利用FPGA设计DDS时,依据DDS的基本原理,系统地分析了DDS输出杂散来源,针对杂散成因在电路上进行了优化设计,在一定程度上改善了相位舍位杂散对信号输出的影响,从而获得失真小、稳定度好的Loran-C输出波形。

1 基于DDS的传统Loran-C信号的设计

1.1 罗兰-C信号模型

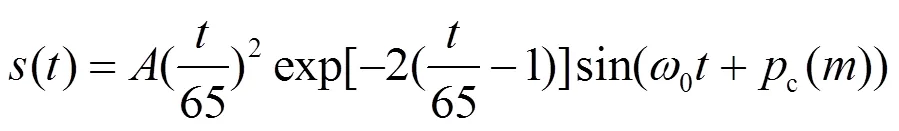

罗兰-C信号是载频为100 kHz的相位调制脉冲,其标准单脉冲波形定义为

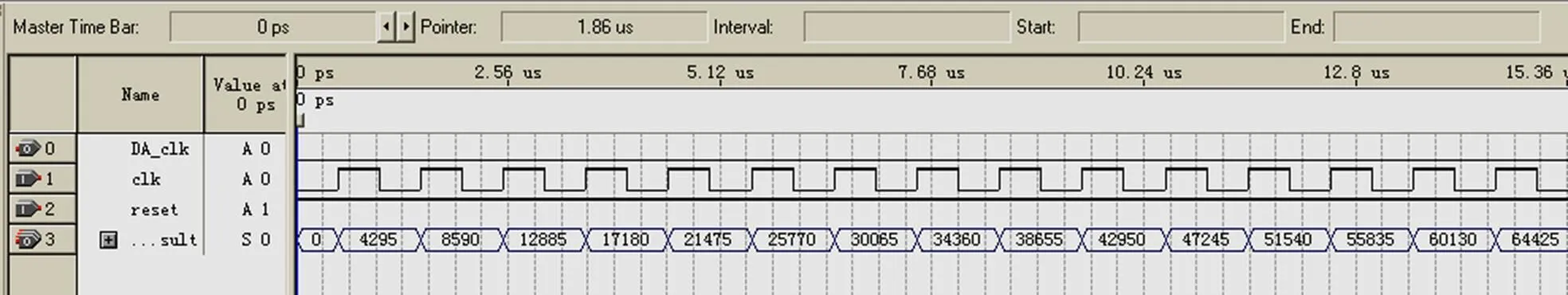

1.2 DDS工作原理

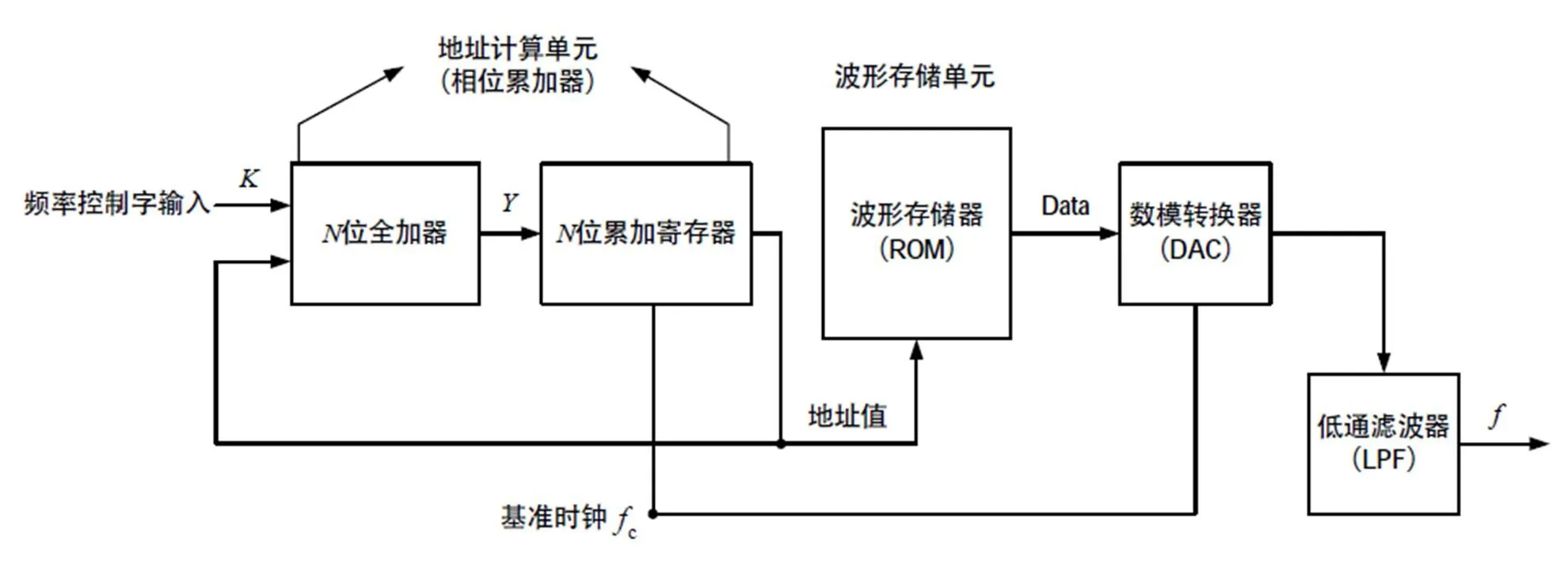

直接数字频率合成技术(DDS)的基础是经典的奈奎斯特采样定理[5],通过查表法产生所需要的波形。DDS的工作原理实质上是以基准频率源(系统时钟)的精确时间间隔对相位进行采样,通过编程频率控制字对系统时钟进行分频以产生所需要的频率。如图1所示,DDS结构中一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和低通滤波器(LPF)。在每一个时钟周期,频率累加器对输入信号进行累加运算,产生频率控制数据。相位累加器由位全加器和位累加寄存器级联而成,对代表频率的二进制码进行累加运算,通过反馈电路,产生累加结果。位相位累加器与其反馈值进行累加,将其结果输出的高位数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换,读出的波形数据送入DAC(数模转换器)。被转换成为阶梯模拟波形,最后由具有内插作用的LPF将其平滑为连续的所需信号波形。

1.3 Loran-C信号产生原理及FPGA实现

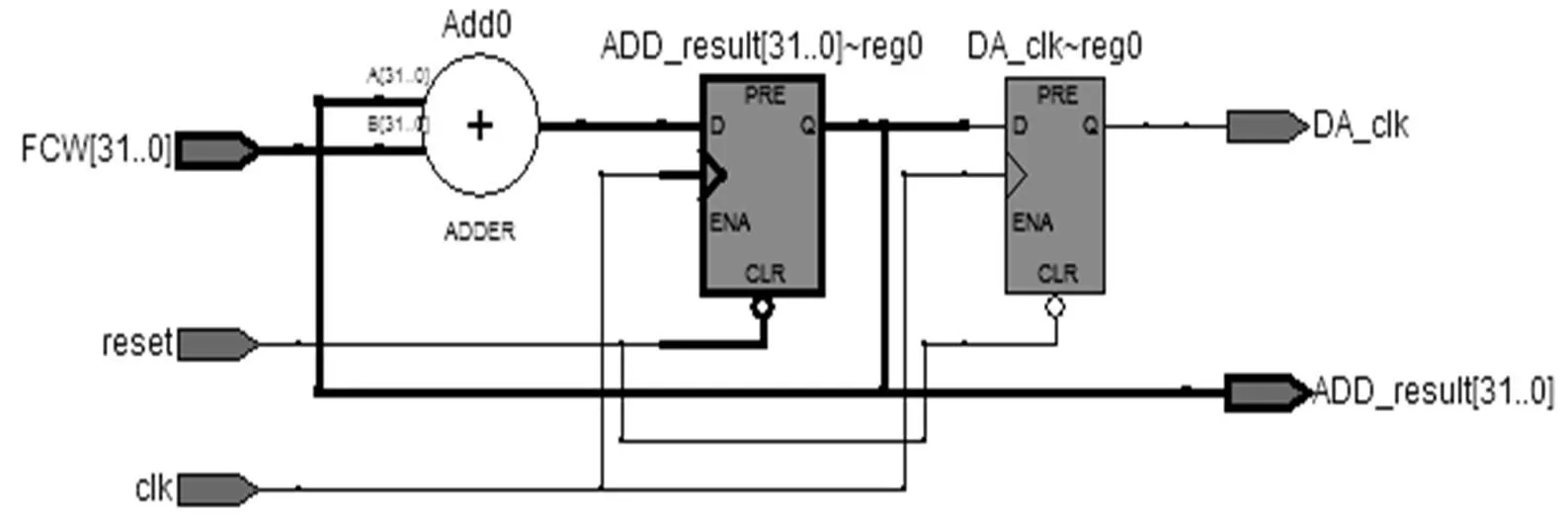

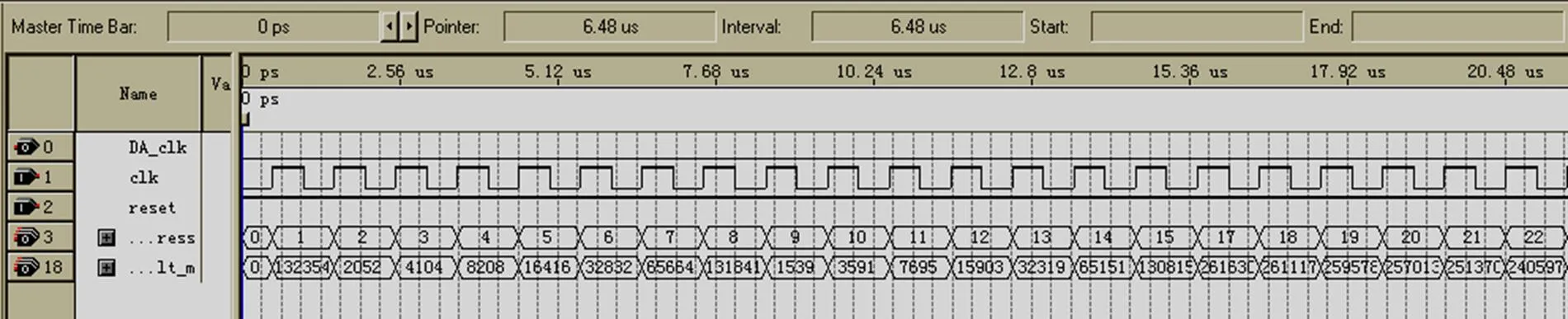

在借助DDS技术实现Loran-C[6]信号的设计过程中,最基本的构件是相位累加器和波形存贮器部分。相位累加器是整个DDS的核心[7-8],主要完成相位累加功能,其输入是相位增量,又可称为频率控制字。在硬件结构中,此次设计使用ALTERA公司的EP2C70F672C8芯片,软件部分在QuartusⅡ开发环境下完成。在具体的设计过程中,当每次时钟脉冲触发时,位全加器会将频率控制字FCW[31:0]与位累加寄存器输出的累加相位数据ADD_result相加,并把相加后的结果送至累加寄存器的输入端,累加寄存器将上一时钟周期作用后所产生的新的相位数据反馈到全加器的输入端,使全加器在下一时钟的作用下继续与频率控制字相加,这样循环进行线性的相位累加,当相位累加器满程时,就会产生一次频率的溢出,从而完成一个完整的周期性运行,而这个周期就是所要实现的Loran-C脉冲信号的一个脉冲周期,相位累加器溢出的频率就是此系统信号模拟源输出的信号频率。相位累加器的RTL逻辑图如图2所示。由此也可以看出,相位累加器在基准时钟的作用下,进行线性相位累加,当位相位累加器累加次后就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS输出信号的周期。传统的相位累加器设计方法是将加法器与寄存器两者组合起来一并进行设计,其仿真结果如图3所示。

图2 相位累加器RTL逻辑框图

图3 相位累加器仿真结果

设计中若是将相位累加器的32 bit用来寻址地址,则4294967 bit的存储空间对ROM资源的消耗量会很大,为此,在FPGA内部配置了一个存储深度为1000,存储容量为1000×14 bit 的Loran-C脉冲信号波形存储器的ROM,另外根据波形存储深度将累加器的高14位作为ROM 查询表的地址,它的存储单元数量214=16 384,输出位数为14 bit。波形存储器的设计基于ROM 宏模块lmp_rom,设置ROM的宽度为14位,调用时产生数据文件.mif,然后直接在定制lmp_rom时,添加数据文件即可。

将设计好的Loran-C脉冲信号程序在软件工具Quartus II 9.0 中编译综合仿真,仿真波形如图4所示。

图4 Loran-C脉冲信号仿真波形图

2 基于DDS的Loran-C信号杂散抑制的分析及FPGA实现

2.1 DDS系统杂散来源及抑制分析

DDS的数字化处理体现了频率捷变速度快、相位连续、易于编程控制等诸多优异性能,但同时全数字化结构也带来丰富的杂散。这些杂散的来源主要有相位截断误差、幅度量化误差、DAC转换误差。通过分析可知其最主要的杂散来源是相位截断所引起的[9-10]。这是因为为了提高输出端信号的频率分辨率,相应地就会将其相位累加器的量化位数值增大,进而就增加了ROM的容量,这样消耗的硬件资源常常是不能容忍或是不可实现的。因此,为了减小系统设计容量,通常的做法就是采取截取其相位累加器输出端口位中的高位作为ROM查询表的寻址地址,其=-低位就必须舍弃,这样就会造成所谓的相位截断误差,使得输出的信号波形失真,在输出信号频谱中就表现为杂散分量。

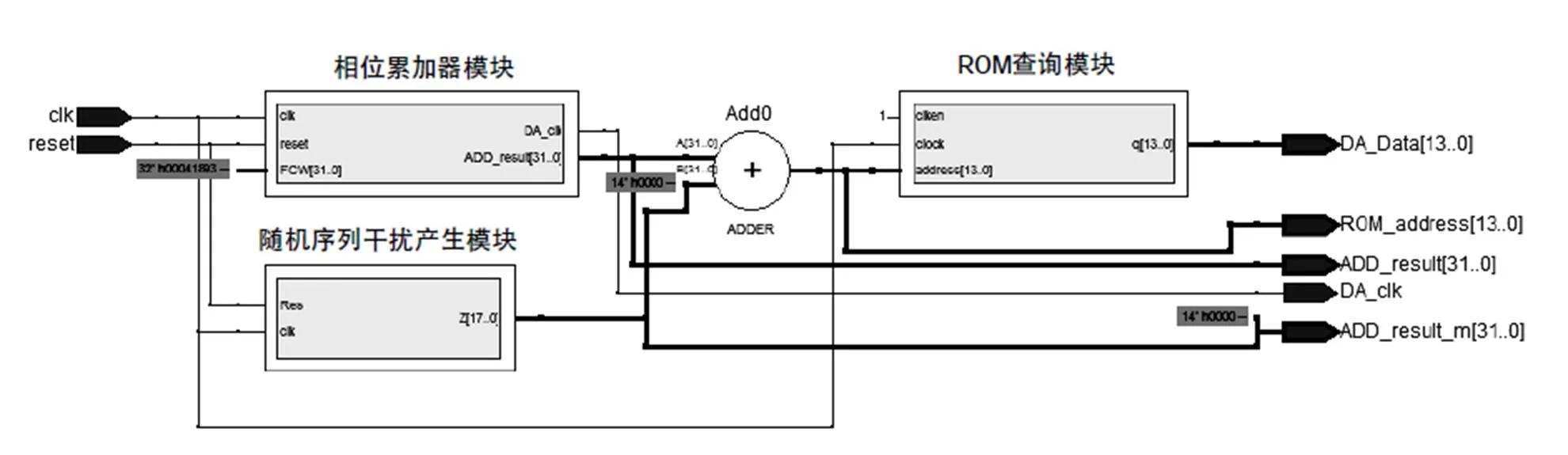

对于所产生的相位截断误差的有关分析研究表明[11],输出信号频谱中的杂散分量是满足周期性特点的序列。因此,设法破坏杂散的周期性及其与信号的相关性,就可以有效地抑制相位截断带来的误差,其主要思想是把确定性的、有规律的杂散转化为随机的、无规律的相位噪声[12]。其实现的过程可以理解为当系统的时钟脉冲信号每次触发时,相应地给相位累加器部分的输出端口加入符合一定统计特性的随机扰动信号来打破误差信号序列的周期性,将具有较大幅度的杂散信号谱线的功率在较宽的频率范围内进行平均从而改善总的信号频谱质量。其具体的实现框图如图5所示。

图5 相位累加器模块的优化设计框图

通常抑制幅度量化误差的方法主要是尽量提高波形存储器的容量,即通过压缩存储数据来等效增大存储器的数据寻址位来实现。理想的DAC本应该是线性的,但在实际的转换过程中DAC是半波不对称的,它的正半周期近似于理想DAC,负半周期则出现偏离。这样时域上的半波不对称在频域中就会引入偶阶杂散,而平衡结构技术可以消除这种半波不对称所造成的偶次分量现象。此外,由于数据传输延迟的不对称,逻辑翻转的不对称等原因,DAC产生了瞬间毛刺,平衡DAC结构有效地消除了毛刺,在一定程度上可以减小杂散能量。

2.2 相位累加器的优化设计及其FPGA实现

从上面相位累加器模块的优化设计框图可以看出,相位累加器的主要功能是分别对输入的频率控制字进行累加,并把累加所得到的相位和存储到位的相位寄存器中。这里相位寄存器的输出长度是32 位,经过相位截断处理后,用其中的高14位去寻址,截断了其低18位,而所设计的随机序列产生器模块在整个过程中是把产生的随机信号在相位截断前与相位寄存器的输出信号相加。因此,根据优化设计要求需在这之前设计产生18位符合一定统计特性的随机序列。

系统设计过程中随机序列码的产生采用最长线性移位寄存器序列即序列产生算法来实现[13]。这种算法简单,产生速度快,可重复性强,并且具有良好的自相关特性和很长的周期性,便于在FPGA中实现。鉴于系统设计中加扰的目的只是破坏相位寻址序列的周期性,所以并不一定要产生一个18位的序列,在这里我们可以设计产生两个9位的序列1和2,再将1和2串连就可以满足加扰的要求。将1和2串连得到的18位移位寄存器的内容作为所需要的随机序列[17: 0]。

随机序列产生模块的输出[17:0]就是所需要的扰动信号,波形仿真如图6所示,可以看出其满足序列良好的自相关特性。把所得的[17:0]与相位累加器的输出ADD_result[31:0]的低18位ADD_result[17:0]相加,再用和的高14位作为地址去寻址波形ROM。在添加了随机信号之后的相位累加器模块的RTL逻辑框图如图7所示。

图6 随机信号产生模块仿真图

综上所述,此次对于DDS优化设计后所综合的RTL逻辑框图如图8所示。在QuartusII 9.0集成开发环境下,优化后的Loran-C脉冲信号发生仿真波形图,如图9所示。

图7 添加了随机信号的相位累加器模块的RTL逻辑图

图8 系统优化后DDS综合的RTL逻辑框图

以上分析研究表明,为了使输出的Loran-C脉冲信号频率稳定度高,非线性失真小,文中针对DDS系统中关键模块相位累加器进行了改进。采用Cyclone II-EP2C70F672C8芯片,利用其频率可控制编程原理,将DDS的组成模块(相位累加器、随机序列干扰产生模块、ROM查询模块等)连接起来进行仿真得到优化后的Loran-C脉冲信号发生仿真波形图。从仿真出的Loran-C脉冲信号波形图可以看出,各路信号输出的同步关系正确,产生的Loran-C脉冲信号格式与要求相符合,且优化后的设计不仅可以很好地实现加法功能,而且具有很短的上升下降时间,输入信号变化时不会产生传统进位加法器那样的毛刺,输出信号稳定。

图9 优化后的Loran-C脉冲信号仿真波形图

2.3 杂散抑制前后信号的性能分析

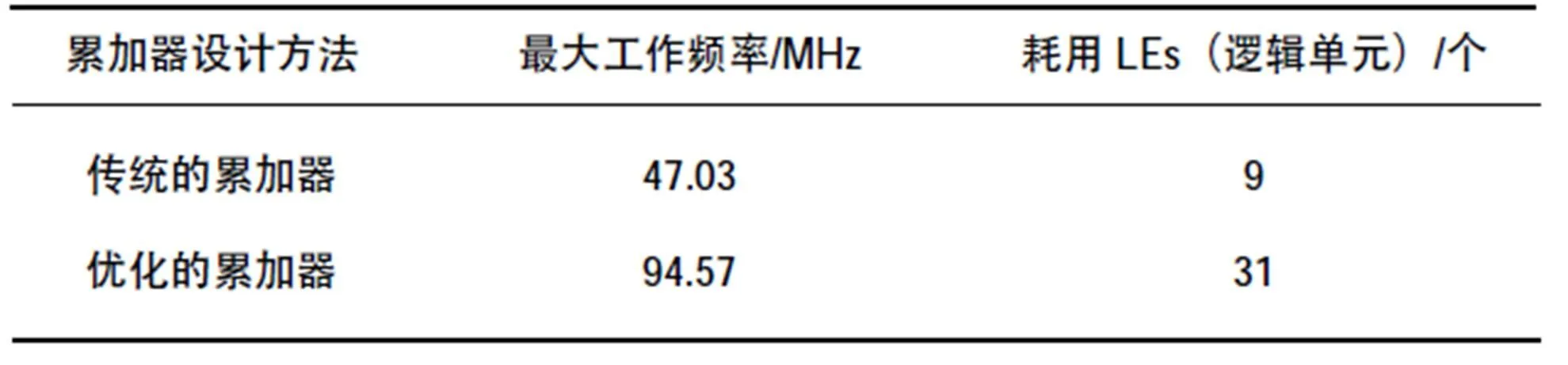

FPGA开发软件中,以co代表数据从触发器的输入端口到输出端口的延时时间,以delay代表组合逻辑的延时,以setup代表触发器的建立时间,则时钟的延迟必须大于co+delay+setup,也就是说最小的时钟周期min=co+delay+setup,即最快的时钟频率max=1/min。FPGA开发软件也是通过这种方法来计算系统最高运行速度max的。由于co和setup是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延迟时间delay,因此缩短触发器间组合逻辑的延时时间是提高电路速度的关键所在。

以此为基础,文中在优化设计实现Loran-C脉冲信号的仿真过程中,加入的满足一定统计特性的18位随机序列,在具体的逻辑电路设计中被分解为较小的2个9位模块,这样通过适当的分配就可以平均组合逻辑电路,然后在中间插入触发器,并和原触发器使用相同的时钟,避免在2个触发器之间出现过大的延时,消除速度瓶颈,因而可以加快系统的工作频率,也可以从根本上提升系统的运行频率。通过运用传统技术方法与杂散抑制技术对DDS系统的关键部分相位累加器进行设计验证,从各自的仿真数据结果可见它们完成的功能是完全一致的,但由于采用的不同的相位累加器设计方法,资源消耗也有差异。如表1所示。传统的相位累加法使得工作频率最高达到47.03 MHz,消耗的资源是9个LEs(逻辑单元),而优化后的设计方法使得工作频率最高达到94.57MHz,资源消耗为31个LEs。比较可以看出,资源上的消耗换来了性能的提高。

表1 累加器设计比较

2.4 系统硬件实体

在实验室系统平台搭建的基础上,借助于带有USB接口的信号采集卡通过同轴电缆与Loran-C信号产生平台相连接,将产生的信号通过AD量化采样后转换为十进制的文本文件存储到PC机中,再利用Matlab将文本文件读入且与后续产生的Loran-C脉冲信号进行对比验证,实验验证框图与具体的系统实验实物环境框图如图10和11所示。

图10 实验验证框图

图11 系统实验实物环境框图

3 结语

本文在对DDS信号产生原理及其杂散来源进行研究分析的基础上,基于FPGA技术对决定DDS信号质量的关键部位——相位累加器模块进行了算法的设计优化,即在相位累加器模块输出端口加入满足一定统计特性的随机信号,达到抑制杂散的目的。根据传统方法与优化方法的实现对比结果可以看出,对于相位累加器的优化设计可以使得Loran信号源输出波形质量得到一定程度的提高,从而验证了采用此种优化设计方法对于抑制DDS设计过程中由于相位截断误差所引起杂散的有效性与可行性。

[1] TIERNEY J, RADER C M, GOLD B. A digital frequency synthesizer[J]. Audioand ElectroAcoustics, IEEE Transactions on, 1971, 19(1): 48-57.

[2] 许慧波, 张厥盛. DDS—直接数字式频率合成器综述[M]. 西安: 西安电子科技大学出版社, 1989.

[3] 迈迪. 长河二号工程-远程无线电导航系统[M]. 北京: 电子工业出版社出版, 1993.

[4] 谢仁宏, 是湘全. 直接数字频率合成器相位截断杂散谱的精确分析[J]. 电子与信息学报, 2004, 26(3): 495-499.

[5] 李衍达, 常迥. 信号重构理论及其应用[M]. 北京: 清华大学出版社, 1991.

[6] 李君一. 罗兰C数据链的设计与实现[J].信息与电子工程, 2006, 4(5): 356-360.

[7] 张平, 高海霞. 用于DDS系统相位累计器的加法器设计. 现代电子技术[J]. 2009, 13(252): 49-52.

[8] 刘晨, 王森章. 直接数字频率合成器的设计及FPGA实现[J]. 微电子学与计算机, 2004, 21(5): 63-65.

[9] 王建新, 张先萌. 直接数字频率合成中相位截断误差分析[J]. 电子测量与仪器学报: 1995, 9(1): 1-6.

[10] 曹平, 安琪, 唐世悦, 等. 基于非均匀采样模型的DDS相位杂散谱分析[J]. 电子与信息学报, 2006, 28(11): 2182-2185.

[11] KROUPA V F, CIZEK V, STURSA J, et al. Spurious signals in direct digital frequency synthesizers due to the phase truncation[J].

Ultrasonics, Ferroelectrics and Frequency Control, IEEE Transactions on, 2007, 47(5): 1166-1172.

[12] 张熙, 王晓峰, 邵春辉. 基于DDS技术的杂散分析及抑制方法[J]. 微计算机信息, 2008, 24(14): 295-297.

[13] 张萍, 戴光明. 高斯随机噪声实时生成实现方法研究[J]. 电子技术应用, 2004, 13(4): 34-47.

Analysis and implementation of spurious signal suppression for Loran-C signal source based on DDS technology

HUANG Pu-jiang1,2,3, HUA Yu1,2, LI Shi-feng1,2

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China;2. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center,Chinese Academy of Science, Xi′an 710600, China;3. University of Chinese Academy of Sciences, Beijing 100049, China)

A shortcoming of the Loran-C signal source designed with DDS(direct digital frequency synthesis) technology is that there are much unpredictable spurious signals in the output. According to the basic principle of the DDS and aiming at the spurious signal caused by phase-truncation, we optimized the design of the phase accumulationmodule, a key part of the direct digital frequency synthesizer. And based on FPGA technology we completed the implementation and simulation/verification of the Loran-C signal source under the QuartusⅡ environment. The results show that an output waveform with small distortion and good stability can be generated through the optimization of the design algorithm, thereby the validity and feasibility of the optimized design method in spurious suppression are verified.

Loran-C; direct digital frequency synthesis; spurious signal caused by phase-truncation; phase accumulation; FPGA(field programmable gate array)

TN911.4

A

1674-0637(2014)01-0041-08

2013-04-01

中国科学院“西部之光”联合学者资助项目(2007LH01);中国科学院科研装备研制资助项目(YZ201218)

皇甫江,男,硕士,主要从事授时理论、方法与技术研究。