基于多核处理器的高清内窥镜视频处理系统

2014-06-07陈耀武

何 灿,陈耀武

(1.浙江大学生物医学工程与仪器科学学院,杭州310027;2.浙江省网络多媒体技术研究重点实验室,杭州310027)

基于多核处理器的高清内窥镜视频处理系统

何 灿1,2,陈耀武1,2

(1.浙江大学生物医学工程与仪器科学学院,杭州310027;2.浙江省网络多媒体技术研究重点实验室,杭州310027)

设计一个基于TILE-Gx多核处理器的高清医用电子内窥镜视频处理系统。该系统支持2路1080p60高清视频输入输出,以及1路YCbCr422格式高清视频的实时H.264编解码,利用现场可编程门阵列为高清视频数据提供输入输出接口,采用4片TILE-Gx多核处理器进行H.264编码解码运算,并使用1片TILE-Gx多核处理器完成系统控制、视频拼接和数据存储转发功能。实验结果表明,该系统的编解码性能满足医用内窥镜的高分辨率和实时性需求,图像质量达到了H.264的High Profile级别。

内窥镜;TILE-Gx处理器;多核处理器;高清视频处理;现场可编程门阵列;H.264编解码

1 概述

随着计算机技术、网络技术和芯片制造技术等的不断发展,医用电子内窥镜领域对视频处理系统的要求越来越高,目前最先进的医用电子内窥镜视频处理系统之一是FUJIFILM公司的VP-4450HD[1],其分辨率可以达到1080i(即1 920×1 080隔行扫描)。本文提出的系统在分辨率上可以达到1080p60(即1 920×1 080逐行扫描,场频60 Hz),并支持YCbCr422格式实时H.264编解码[2],支持画中画和画外画显示。

传统的电子内窥镜视频处理系统使用PC配合视频采集卡[3]或者使用专门的DSP芯片(如TI公司的DaVinci系列)实现视频编解码[4],无法满足医用内窥镜对于分辨率和实时性越来越高的要求,本文系统使用Tilera公司的36核处理器对YCbCr422格式的1080p60高清视频进行实时的H.264编解码,系统具有视频处理性能高、图像质量好、延时短等特点。

2 系统总体架构和工作原理

系统的总体结构如图1所示。系统输入源为两路1080p60视频,一路为医用电子内窥镜,另一路为其他辅助医疗视频设备或者高清摄像机;输出为两路1080p60视频,可以选择为实时视频输出或者解码输出,支持画中画和画外画模式视频输出。

图1 系统总体结构

系统基本工作原理是:两路视频信号以3G-SDI格式进入系统,经过3G-SDI均衡器和3G-SDI解串器后进入FPGA,FPGA将其转换为16位宽并行数据后通过PCI-Express总线传送给TILE-Gx多核处理器,处理器将对视频原始数据进行编码和存储。TILE-Gx多核处理器将输出视频数据通过 PCIExpress总线传送给 FPGA,FPGA将其转换为SMPTE425M标准[5]的格式后输出,经过3G-SDI串化器后以3G-SDI格式输出系统。

3 系统实现

本文系统包括1块主板和4块子板,主板主要负责系统控制、视频输入输出、视频拼接处理和视频数据存储等,子板主要负责视频数据的H.264编码和解码。主板与各子板间使用高速连接器连接。下面分别描述主板和子板的设计与实现。

3.1 系统主板设计与实现

系统主板设计与实现如下:

(1)硬件组成

主板硬件组成如图 2所示,可以分为2个单元——主控单元与采集显示单元,2个单元通过PCI-Express高速接口互联。

图2 主板硬件设计

主控单元负责整个系统的控制,以及对视频拼接处理。主控单元主要由TILE-Gx8036及外围设备组成,TILE-Gx8036是Tilera公司推出的一款多核处理器,拥有36颗高性能RISC核心,核心工作频率为1.2 GHz。该处理器支持丰富的扩展接口,包括: 2个独立的64 bit存储 DDR3控制器,最高支持1 600 MT/s的DDR操作;3个Gen2 PCI-Express x4接口;最多4个万兆以太网即XAUI接口或者16个10/100/1 000 SGMII以太网接口;2个USB2.0接口;4个I2C接口等[6]。

为实现本地存储功能,选用 Marvell公司的88SE9120作为SATA控制器。88SE9120是一款基于PCI-Express总线的 SATA控制器,提供一个Gen2 PCI-Express x1接口,兼容SATA 3.0标准,支持RAID。本文系统直接将其挂载在主板CPU的PCI-Express0总线上。

由于TILE-Gx8036处理器的PCI-Express接口有限,主板无法直接通过PCI-Express总线与各个子板进行数据传输,因此本文系统使用了一颗 PCIExpress Switch芯片对主板CPU的PCI-Express接口进行扩展,Switch芯片选用的是 IDT公司的89HPES32T8G2,这是一款 32-lane,8-port的 Gen2 PCI-Express Switch,最多可提供4个x8或者8个x4的交换接口。PCI-Express Switch芯片挂载在主板CPU的PCI-Express1总线上。

主板处理器的其他外围设备还包括:2个DDR3 SO-DIMM,1个USB 2.0 PHY和1个千兆以太网PHY。

采集显示单元负责系统视频数据的采集和显示。采集显示单元以Xilinx公司的XC6VLX130T FPGA为核心。XC6VLX130T属于Xilinx Virtex-6系列FPGA,拥有128 000个逻辑单元,9 504 Kb内部 Block RAM,支持 64 bit DDR3接口,支持x4 Gen2 PCI-Express接口[7]。本文系统将其挂载在主板CPU的PCI-Express2总线上。FPGA的外围设备包括1个DDR3 SO-DIMM,2个3G-SDI均衡器, 2个3G-SDI解串器以及2个3G-SDI串化器。

(2)FPGA设计

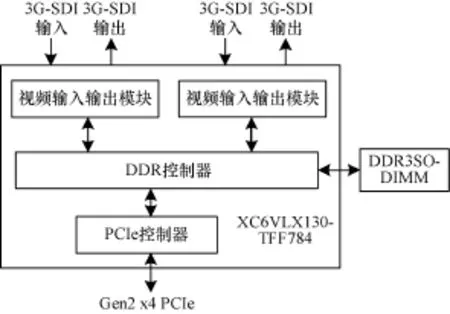

FPGA总体设计如图3所示,主要由2个视频输入输出模块、1个 DDR控制器模块和1个 PCIExpress控制器模块组成。2路视频数据进入FPGA后,首先被2个视频输入输出模块去掉包头包尾,得到16 bit YCbCr422的有效视频数据,有效数据通过DDR控制器存入DDR3内存,当CPU发起PCIExpress读事务时,DDR控制器将数据从DDR3内存中取出,由 PCI-Express控制器将其发送给 CPU。CPU将待显示的视频数据通过PCI-Express总线发送给FPGA,由PCI-Express控制器接收,之后数据通过DDR控制器存入DDR3内存,当视频输入输出模块需要输出数据时,DDR控制器将数据从DDR3内存中取出,视频输入输出模块添加好包头包尾后将其输出FPGA送至3G-SDI串化器。

图3 FPGA功能模块

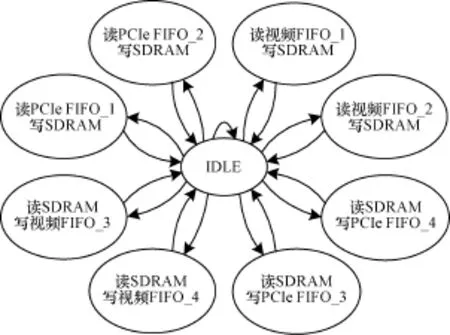

系统FPGA需要对外部输入的两路1080p60高清视频数据进行缓存,然后再发送给CPU进行处理;同时,FPGA还需要对 CPU发送来的两路1080p60高清视频数据进行缓存,然后再将其输出。从整体来看,相当于一共有8路1080p60高清视频数据同时需要由FPGA发送或接收,这对FPGA的控制逻辑以及对外部存储设备的读写速度有较高要求。本文设计扩展了一个 DDR3 SO-DIMM为FPGA提供缓存,数据总线宽度为64 bit,工作时钟频率为400 MHz。在DDR控制器中例化了8个FIFO,用于缓存8个读写接口的数据,并使用一个状态机来协调对这8个FIFO的读写操作,如图4所示,状态机共有9个状态:系统复位时为IDLE状态,该状态下不做任何操作,是其他各状态的入口和出口状态;4个读FIFO写SDRAM状态,每一个状态对应一个FIFO,当对应FIFO的prog_full拉高时进入此状态,该状态下从对应 FIFO取出数据并写入SDRAM;4个读SDRAM写FIFO状态,每一个状态对应一个FIFO,当对应FIFO的prog_empty拉高时进入此状态,该状态下从SDRAM取出数据并写入对应FIFO。

图4 FPGA DDR控制状态机

(3)软件设计

主板CPU的软件架构如图5所示,主板软件的核心是视频拼接程序。

图5 主板CPU软件架构

视频拼接程序由9个核心完成,首先由主核心将内存里的一帧主画面数据分为8个连续的块,通知8个子核对各个块进行缩小或放大处理[8]并存储至目标区域,然后将一帧子画面数据做同样的处理,并叠加至上述目标区域,根据对2个画面的不同缩放处理和不同位置的叠加,可以实现多种画中画与画外画显示功能。

3.2 系统子板设计与实现

系统子板设计与实现过程如下:

(1)硬件组成

子板总体硬件设计较简单,主要由 TILEGx8036及外围设备组成,外围设备包括8片2Gb的DDR3 SDRAM、1个千兆以太网PHY和一组高速连接器。系统共有4块子板,其中,3块子板负责在主板处理器的协调下对一路1080p60高清视频进行实时H.264编码;1块子板负责H.264解码。各子板通过 Gen2 x4 PCI-Express总线与主板进行数据交互。

(2)软件设计

子板CPU的软件架构与主板CPU类似,子板软件的核心是H.264的编码/解码程序。

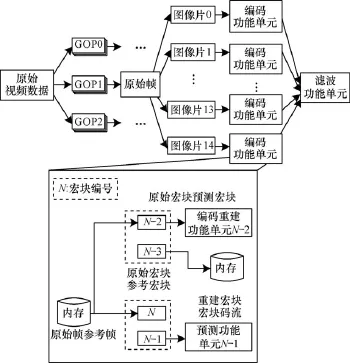

H.264编码的流程如图6所示,为充分利用多核处理器的优势提高系统编码性能,做了3个层次的并行化处理[9]:

1)并行的GOP(Group of Picture)划分,主板CPU以GOP为单位依次循环向3个编码子板发送原始视频数据,3个编码子板同时执行编码任务,编码完成后,子板再通过PCI-Express总线将数据传回主板CPU。

2)基于数据单元划分的帧级并行编码设计,将每帧图像划分成15个片(Slice),用15个运行在不同核心上的进程分别编码。

3)基于功能单元划分的宏块级并行编码设计,在基于数据单元划分的帧级并行编码架构基础下,将编码功能单元进一步分为预测功能单元和编码重建功能单元,在数据并行的基础上,每个进程创建出一个线程用来执行预测功能单元,同时为该线程分配一个独立的核心,主线程则用来执行编码重建,所以每个编码子板CPU里共有30个核心用于实现H.264编码功能。

图6 H.264编码流程

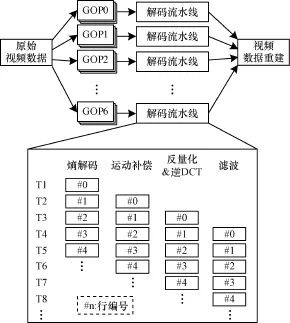

H.264解码的流程如图7所示,解码器共使用29个核心,由一块解码子板提供,其中1个核心作为主核心,负责整个编码流程的调度,其余28个核心分为7组,并行地执行解码任务。首先,主核心将待解码的原始视频数据以GOP为单位分为7组,然后通知7个核心组开始解码,每个核心组里的4个核心以行为单位,使用流水线的方式完成解码任务中的各个子任务,实现了解码的并行化处理,提高了解码效率[10]。

图7 H.264解码流程

4 系统性能

系统性能如下:

(1)接口性能

测试使用2台1080p60高清摄像机提供输入源,使用2台全高清显示器承载输出,实际效果如图8所示,系统运行稳定,显示正确,证明系统接口性能满足要求。

图8 系统实际运行效果

(2)编码性能

选用7段YCbCr422格式视频序列对系统编码性能进行测试,码率设置为60 Mb/s,熵编码方式为CABAC编码[11],GOP设置为15。测试结果如表1所示,结果表明系统编码性能能够达到60 fps以上,满足系统要求。

表1 系统编码性能 fps

(3)解码性能

选用 7段经过本文系统编码的视频序列(YCbCr422格式,CABAC编码,GOP=15)对系统解码性能进行测试。测试结果如表2所示,结果表明系统解码性能能够达到60 fps以上,满足系统要求。

表2 系统解码性能 fps

(4)图像质量

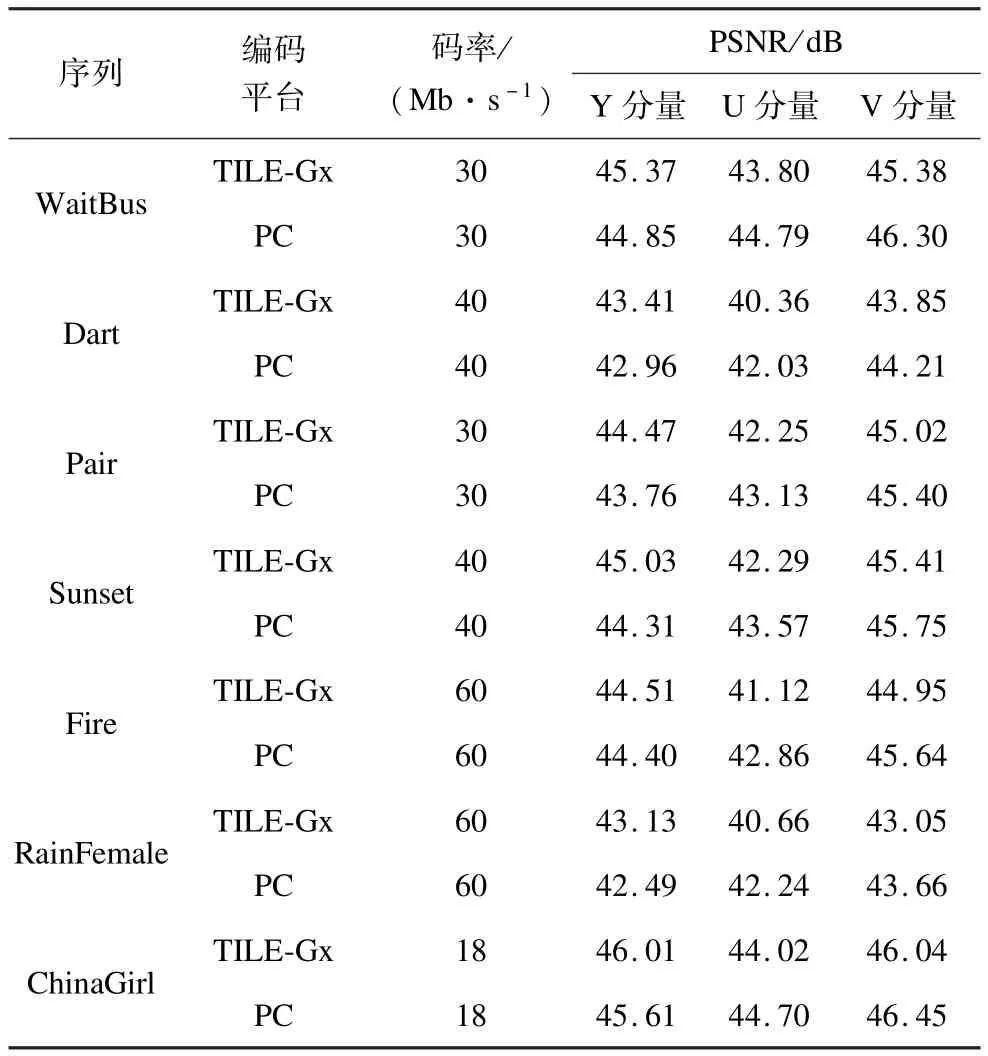

通过与使用H.264 JM18.0编码器的PC在相同编码选项、相近码率下比较PSNR值来对本文系统的图像质量进行客观评价[12]。测试选用7段YCbCr422格式,1080p60的视频序列,分别在本文系统和PC上进行编码,GOP设置为 15,熵编码方式选择为CABAC编码。PC上使用的编码器是H.264 JM18.0编码器,Profile选项设置为High Profile。测试结果如表3所示,由表中的PSNR值的对比可以看出,本文系统图像质量达到了H.264的High Profile级别。

表3 峰值性嗓比对比

5 结束语

本文提出一种基于Tilera多核处理器和FPGA的嵌入式高清医用电子内窥镜视频处理系统设计方案,系统使用Tilera多核处理器完成系统控制和视频的实时H.264编解码,通过Xilinx Virtex-6 FPGA实现多路视频的输入输出。相对于其他传统的医用电子内窥镜视频处理系统,本文系统能够支持YCbCr422格式1080p60高清视频处理,处理性能高、图像质量好、功能稳定可靠。随着未来核心数更多、性能更高的多核处理器的出现,下一步将对本文系统实现升级,以提供更高的视频处理性能和更好的图像质量。

[1] Fujifilm Corporation. Electronic Video Endoscopy System EPX-4450HD Specification[EB/OL].(2011-02-19).http://www.fujifilm.com/products/medical/ brochures/pdf/index/epx4450hd.pdf.

[2] 夏 龄,舒 涛.一种H.264/AVC视频编码并行算法[J].计算机工程,2013,39(4):314-317.

[3] Park J A,Chang M.Development of a Low-cost PC-based Endoscope System [C]//Proceedings of ICHIT'06.Washington D.C.,USA:IEEE Computer Society,2006: 109-115.

[4] 李 侃,陈耀武.面向医用电子内窥镜的高清视频处理系统[J].计算机工程,2011,37(23):261-263,266.

[5] SMPTE.425M-2008SMPTE Standard for 3GB/s Signal/Data Serial Interface——Source Image Format Mapping[S].2008.

[6] Tilera Corporation.TILE-Gx8036 Processor Specification Brief[EB/OL].(2011-05-17).http://www.tilera.com/ sites/default/files/productbriefs/TILE-Gx8036_PB033-02_ web.pdf.

[7] Xilinx,Inc..Virtex-6 Family Overview[EB/OL].(2012-02-19).http://www.xilinx.com/support/documentation/ data_sheets/ds150.pdf.

[8] Gonzalez R C,Woods R E.Digital Image Processing[M].北京:电子工业出版社,2010.

[9] 于俊清,李 江,魏海涛,等.基于同构多核处理器的H.264多粒度并行编码器[J].计算机学报,2009,32 (6):1100-1109.

[10] 郭 倩,陈耀武.基于功能模块的H.264并行解码算法[J].计算机工程,2010,36(23):231-233.

[11] Marpe D,Schwarz H,Wiegand T.Context-based Adaptive Binary Arithmetic Coding in the H.264/AVC Video Compression Standard[J].IEEE Transactions actions on Circuits and Systems for Video Technology, 2003,13(7):620-636.

[12] 蒋刚毅,黄大江,王 旭,等.图像质量评价方法研究进展[J].电子与信息学报,2010,32(1):219-226.

编辑 索书志

High Definition Endoscope Video Processing System Based on Multi-core Processor

HE Can1,2,CHEN Yaowu1,2

(1.College of Biomedical Engineering and Instrument Science,Zhejiang University,Hangzhou 310027,China;

2.Zhejiang Provincial Key Laboratory for Network Multimedia Technologies,Hangzhou 310027,China)

A solution of embedded endoscope video processing system based on TILE-Gx multicore processor is designed.The system supports 2-channel input and output port for 1080p60 HD video data and real-time H.264encoding/ decoding of YCbCr422 format video.FPGA is applied to realize the input/output port of video data.4 pieces of TILE-Gx processors are applied to encode/decode,another TILE-Gx processor is applied to the system management,video mixing, and hard disk storage.Experimental results show that,the performance of encoding and decoding fulfills the requirement of high definition and real-time of endoscope,and the image quality reaches H.264 High Profile level.

endoscope;TILE-Gx processor;multicore processor;High Definition(HD)video processing;Field Programmable Gate Array(FPGA);H.264 encoding and decoding

1000-3428(2014)111-0001-05

A

TP391

10.3969/j.issn.1000-3428.2014.11.001

中央高校基本科研业务费专项基金资助项目;浙江省重点科技创新团队基金资助项目(2011R09021-06)。

何 灿(1990-),男,硕士研究生,主研方向:嵌入式系统;陈耀武,教授、博士生导师。

2013-11-29

2013-12-24E-mail:canhe890@zju.edu.cn

中文引用格式:何 灿,陈耀武.基于多核处理器的高清内窥镜视频处理系统[J].计算机工程,2014,40(11):1-5.

英文引用格式:He Can,Chen Yaowu.High Definition Endoscope Video Processing System Based on Multi-core Processor[J].Computer Engineering,2014,40(11):1-5.