布尔差分故障检测算法在FPGA上的实现

2014-06-01张云桃孟宪民

张 敏 张云桃 孟宪民

(哈尔滨工业大学(威海)信息与电气工程学院1,山东 威海 264209;山东卡尔电气股份有限公司2,山东 威海 264209)

0 引言

故障测试是信息产品制造的重要组成部分。在科学技术高度发展的今天,测试工作处在各种先进装备系统设计和制造的首位。据资料显示,目前测试成本已达到所研制设备成本的50%甚至70%。如何使诊测更加快捷和准确是一项重要的研究课题[1]。

传统的故障诊断是一项十分复杂的工作。测试的对象数量庞大,如待测电路的输入与输出变量可能多达数十个甚至上百个,分支庞杂;电路响应是组合的,而且在大多数情况下是时序的;需要观察的逻辑位于芯片内部,不可能直接测量它们的逻辑电平与输入输出波形。

现代数字系统故障诊断的基本思想是在输入端加载激励信号,在输出端得到响应;根据激励和响应的对应关系以及电路的拓扑关系,确定故障点。其实现的关键是测试向量的生成,即在输入端加载激励信号,使输入故障通过电路内部的故障点反映出来。找到故障的测试向量后,采用数字系统故障诊断进行故障检测。

由于采用FPGA的电子系统更具设计灵活性,其根据需要更改内部逻辑来满足硬件外围电路要求;而故障测试算法具有逻辑的完备性,可以大大提高参试性能和准确度,因此将两者相结合来进行故障诊断。由于FPGA中的逻辑单元是可编程的,因此可针对布尔差分法定制测试逻辑软件,而不必做出任何物理硬件变动[2]。

1 实现方案设计

方案具体实现过程如下。

首先针对布尔差分算法特性,构造一个具体数字电路进行故障分析及故障检测。

然后利用算法,求出电路各个节点以及各种故障的测试矢量,使得输入故障在输出端表现出来。将测试矢量作为故障电路的激励,观察输出端的响应,并与该输入下正常电路的输出值进行比较,若输出结果与真实值相反,则测试矢量生效;否则,测试矢量失效。将生效的测试矢量记录下来,作为下一步进行电路故障检测时的电路激励。

最后计算出每一种故障下各个节点的故障列表,建立检测故障所需要的电路模块,包括故障仿真模块、分频模块、消抖模块、检测模块等。当将某一故障对应的所有的测试矢量作为输入时,各个节点的逻辑函数值都与故障列表吻合,则确定该电路存在故障,并将故障类型显示在开发板上[3]。

2 算法分析

一阶布尔差分法是用来求解单故障测试矢量集的。如果要求解多故障的测试矢量集,就必须使用高阶布尔差分。这里主要叙述二阶布尔差分及双故障测试矢量的求法。定义函数f(X)为:

式(2)为函数f相对于xi和xj的二阶差分分别为第i个和第j个故障的输入测试矢量,且满足如下关系式:

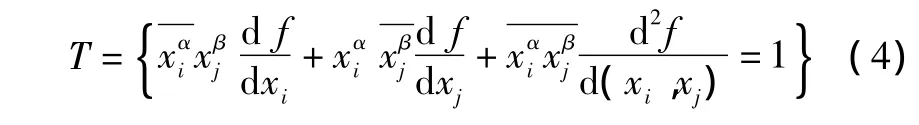

检测双故障 xi(s-a-α)、xj(s-a-β)的测试集为:

式中:α,β∈(0,1);x1=x,x0=1。

3 具体实现

3.1 电路建模

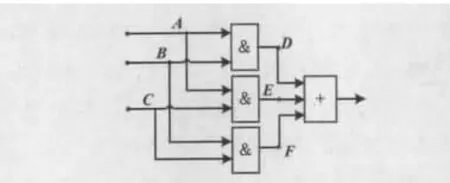

建立的数字电路模型如图1所示。

图1 数字电路模型Fig.1 Model of digital circuit

由图1可以看出,该电路图由3个与门和1个或门组成,一共有6个节点。考虑节点的单固定故障和双固定故障,理论上可以计算出电路中存在的故障有72种。但是,考虑到与或门本身的逻辑功能,有一部分故障是不可测的。

对于与门来说,它的某一个输入端若存在逻辑固定低电平故障,则它的输出端在正常情况下应该是逻辑低电平。但是,假如这个与门的输出端同时也出现逻辑固定低电平故障,则对于这一类双固定故障,它是不可测的。因此,排除这类故障,实际上可测的故障有66种。

3.2 布尔差分法求解测试矢量

测试生成是数字电路故障诊断研究的核心问题之一。将测试矢量作为正常电路的输入,观察电路输出值;在相同情况下,把它们加到故障电路的输入端,若此时故障输出值与正常输出值不一致,则这样的电路输入称为这一类故障的测试矢量。每一个故障可以有多个测试矢量,而每一个电路输入也可以是多个故障的测试矢量[5]。

3.2.1 单故障测试生成

在所设计的电路模型中,共有6个节点,这6个节点都有可能出现故障。而每一个节点出现的故障类型有(s-a-0)型故障和(s-a-1)型故障这两种情况。因此,可能存在的单故障有12个。

布尔差分法求解每个故障的测试矢量步骤如下。

①列出电路输出对每一个故障的一阶布尔差分。

②列出诊断每一个故障的测试矢量的计算公式。

③用Matlab实现每一个故障测试矢量的生成。

④假如需要求解A(s-a-1)故障的测试矢量,图1所示电路的输入Y的逻辑表达式为:

⑥最后,利用Matlab编程实现。

定义矩阵a:

把A0赋值为一个8行3列的零矩阵。对于a中的某一行,它的第一列数表示为A输入,第二列数表示为B输入,第三列数表示为C输入。接着,把a中的每一行元素代入求解故障A(s-a-1)的测试矢量集的方程中。把满足这个方程的第n行元素相应地赋值给A0矩阵中的第n行元素。运行程序后,可以从矩阵A0中得出故障A(s-a-1)的测试矢量集[6]。

由于矩阵A0中第一行本身就是零元素。因此,赋值结束后,第一行仍然是零元素,不能确定这一行元素是否为故障A(s-a-1)的一个测试矢量。最直接的办法是将这一行的元素代入测试矢量集的方程中进行验证,如果满足,则这一行也属于故障A(s-a-1)的一个测试矢量;反之,则不属于。同理可求解出其他11种单故障的测试矢量集。记录这些测试矢量,以备试验需要[7]。

3.2.2 双故障测试生成

设计的电路中存在54种可检测的双故障。而求解双故障的测试矢量集的方法步骤与单故障的求解过程类似。

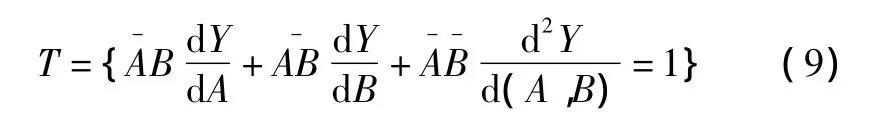

假设需要求解故障A(s-a-1)、故障B(s-a-1)的测试矢量集,则Y相对于节点B的一阶布尔差分为:

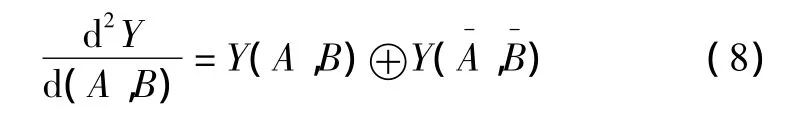

Y对于A、B节点的二阶布尔差分为:

故障A(s-a-1)、故障B(s-a-1)的测试矢量集为:

则故障A(s-a-1)、故障B(s-a-1)的测试矢量集为T={001,010,100}。

采用Matlab解测试矢量集的过程与单故障类似,同样需要定义矩阵a,以及用来存储测试矢量集的零矩阵A1、B1,然后将矩阵a经过循环代入测试矢量集方程,把符合条件的行元素赋值给矩阵A1、B1中相应的行。最终可以从矩阵A1、B1中得出故障A(s-a-1)、故障B(s-a-1)的测试矢量集。同理可以解出其他双故障的测试矢量集。

在求解双故障过程时,不管两个节点在电路中有任何逻辑关系,它们的二阶布尔差分都必须把这两个节点看成是独立变量,否则就会得出错误的测试矢量[8]。

4 FPGA实现

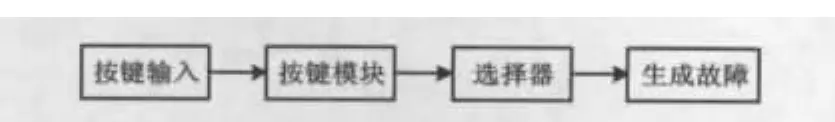

在QuartusII上建立模块,实现故障仿真、故障检测和显示的功能。其中涉及到的模块有消抖模块、分频模块、伪随机序列生成模块、按键模块、故障生成模块、电路模块、检测模块和显示模快。总体设计模块流程图如图2所示。

图2 总体设计模块流程图Fig.2 The whole design module flowchart

4.1 伪随机码生成器

利用测试矢量来进行故障检测,设计中就必须考虑如何自动生成所有的测试矢量。对于3输入的逻辑电路,它的所有可能输入有8种。用伪随机码生成器来模拟电路的输入。3级m序列生成器如图4所示。

图3 3级m序列生成器Fig.3 The generator of 3-layer m sequence

4.2 故障仿真模块

利用开发板上的按键来生成所需要的故障。基于这个思想,设计了1个3选1选择器来仿真逻辑固定高电平故障或逻辑固定低电平故障。此外,按键模块还有1个输入。在操作过程中,通过按键输入来改变其输出值,利用这些输出值来控制选择器的工作状态。

状态机及其设计技术是数字系统的重要组成部分。在设计中,定义了133种状态,其中66个是故障状态;另外66个是故障进入下一个状态的中间态;还有一个状态是初始状态,即此电路正常,没有任何故障。故障仿真模块的原理框图如图4所示。

图4 故障仿真模块原理Fig.4 Principle of fault simulation module

4.3 检测模块

对于某一故障,当输入为它的一个测试矢量时,记录此时各个节点的逻辑值作为这个故障的故障列表信息;当所有测试矢量都列表填入故障列表中时,故障列表信息就完备了。

每一个故障的故障列表与其他故障都是不同的。利用这种完备的故障列表信息,可以准确地确定这个故障的类型。将所有故障的完备故障列表信息存入检测模块,它的输入端用于接收各个节点的逻辑值信息,并对这些输入进行判断,如果电路出现的故障列表与某个故障的故障列表信息一致,则说明电路中存在这个故障。检测模块的工作原理框图如图5所示。

图5 检测模块原理框图Fig.5 Principle of the detection module

4.4 显示模块

设计所用的开发板FPGA是EP2C8Q208C8,开发板的8个动态数码管是共阳型。设计中用到了6个数码管。通过动态显示模块,将检测模块检测到的故障类型在4个数码管上加以显示,另外两个数码管用来显示故障标号。

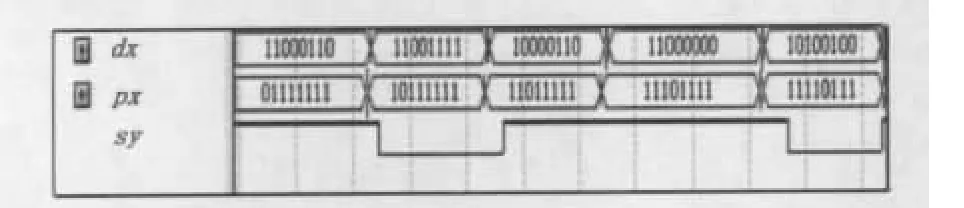

故障C(s-a-1)、E(s-a-0)采用QuartusII波形仿真后得到的界面如图6所示。图6中,dx代表段选管脚的输入值,px代表片选管脚的输入值。将整个电路编译后下载到开发板,数码管可以动态显示出C1E0,表示检测到电路中存在该故障。

图6 故障波形图Fig.6 Fault waveforms

5 结束语

布尔差分法是生成故障测试矢量的重要方法,利用它们可以求解出任何一种逻辑电路的故障测试矢量,包括时序逻辑电路和组合逻辑电路[9]。由于工作量的问题,本设计选择的是对较为简单的组合逻辑电路进行故障分析与检测。利用状态机以及选择器的组合,成功地设计出一种可以仿真故障的方法。该方法能够按照设计者的意愿来生成任何一种故障,避免了通过编程仿真带来的麻烦;其次,以伪随机码生成器的输出作为电路的模拟输入,不仅可以实现设计要求,而且提高了设计的准确性以及检测结果的权威性[10]。

[1]秦福星,周庆年,安江波,等.基于测试向量的数字电路故障诊断[J].船电技术应用研究,2010(10):47-48.

[2]郭希维,苏群星,谷宏强.数字电路测试中的关键技术研究[J].科学技术与工程,2006(18):2903-2906.

[3]黄考利,连光耀,魏忠林.基于仿真级数的故障知识获取方法研究[J].兵工学报,2005(4):573-576.

[4]杨士元.数字系统的故障诊断与可靠性设计[M].北京:清华大学出版社,2000:29 -35.

[5]Su Wei,Dong Nanping,Fan Tongshun.The development of interface adapter in the digital circuit fault diagnosis system based on VXI[J].Power Electronics and Intelligent Transportation System(PEITS),2009(9):431 -434.

[6]周继承,黎飞,肖庆中.数字电路故障诊断[J].应用科技,2008(2):29-32.

[7]吴丽华,李涛,邹海英,等.多故障测试生成的一种简化算法[J].电机与控制学报,2008(3):350-353.

[8]Su Wei.Research for digital circuit fault testing and diagnosis techniques[J].IEEE Transactions on Test and Measurement,2009:330-333.

[9]余党军,郑茂生,陈偕雄.基于D算法的组合电路单故障检测的代数方法[J].杭州电子工业学院学报,2000,20(6):373 -378.

[10]陈永刚,张彩珍.组合电路的故障测试生成D算法研究[J].兰州铁道学院学报,2002(6):14-16.