基于VHDL之CPU设计与实践

2014-05-16徐爱萍张玉萍涂国庆

徐爱萍, 张玉萍, 涂国庆

(武汉大学计算机学院,湖北武汉 430072)

基于VHDL之CPU设计与实践

徐爱萍, 张玉萍, 涂国庆

(武汉大学计算机学院,湖北武汉 430072)

随着大规模可编程逻辑器件的发展,EDA技术已成为硬件系统电路设计的重要手段。基于EDA技术的计算机组成原理整机实习通常在Quartus II仿真平台上实现。早期均采用Block Diagram的设计方式,虽然设计过程直观,但仿真调试困难,难以完全调试成功。本文研究了基于VHDL的灵活方便的CPU设计过程,该设计由取指、指令译码、指令执行、存储器接口、通用寄存器组和寄存器输出六个组成部分,最后通过调试软件直接观察寄存器的值来验证了设计的准确性。本研究方法对改革该课程的整机实习,发挥学生的主动能动性,提高学生的自主创造能力具有很好的指导意义和实际参考价值。

计算机组成原理;CPU设计;整机实习;VHDL

0 引言

计算机组成原理课程是计算机专业的一门重要专业基础课程,它在计算机类专业的课程中起着承上启下、软硬件兼容的重要作用[1]。本课程的基础课程是“数字逻辑电路”,在该课程实验中学生受到过器件测试、单元电路设计,分析等方面的训练,在本实验课的后续课程“微机系统与接口技术”中,学生将进一步学习一些外围电路芯片的开发应用。因此,计算机组成原理课程主要着眼于计算机硬件系统的设计方法,介绍计算机的基本组织以及内部各组成部件如何协调工作。为了加强该课程的实践性教学环节,培养和训练学生在硬件方面的设计和动手能力,本课程结束后为学生开设整机实验,要求设计一个能执行一个指令系统的CPU,让学生在理论与实践相结合的基础上,加深对整机概念的了解[2],掌握控制器设计的方法与技术,从而提高学生自行设计、调试分析的独立工作能力。随着大规模可编程逻辑器件的发展,EDA技术已成为硬件系统电路设计的重要手段[3-8]。基于EDA技术的计算机组成原理整机实习通常在Quartus II仿真平台上实现[9]。早期均采用Block Diagram的设计方式,虽然设计过程直观,但CPU仿真调试困难。本文研究了一个8位CPU设计实例,揭示了基于VHDL的CPU设计的方法与技术并调试成功,对学生自主完成基于VHDL的CPU设计具有很好的指导意义。

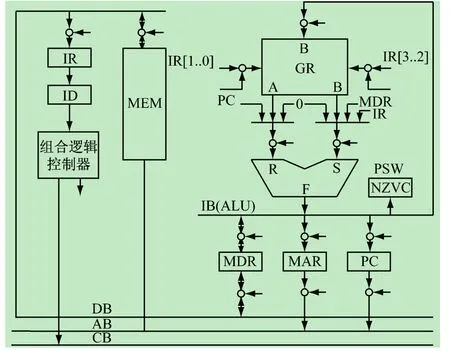

1 设计实例要求

中央处理器由控制器、运算器和总线组成。运算器由算术逻辑单元ALU、通用寄存器GR、程序状态字寄存器PSW和ALU输入端的选择器组成。控制器是全机的指挥中心,由程序计数器PC、指令寄存器IR、地址寄存器MAR、数据寄存器MDR、指令译码器、时序系统和组合逻辑信号发生器组成。程序计数器PC用以指出下条指令在主存中的存放地址,每取一个指令字PC增1;指令寄存器IR用来保存当前正在执行的一条指令的代码;地址寄存器MAR用来存放当前CPU访问内存单元的地址;数据寄存器MDR用来暂存由内存储器中读出或写入内存的指令或数据;指令译码器分别对操作码字段、寻址方式字段、地址码字段进行译码,向控制器提供操作的特定信号;时序部件用来产生各种时序信号节拍周期信号,它由统一时钟CLK分频得到;组合逻辑控制器根据IR的指令、PSW中的状态信息以及节拍,产生控制整个计算机系统所需的各种控制信号。它接收从控制器送来的命令并执行响应的动作,负责对数据的加工和处理。系统总线是CPU与主存储器MEM相联的总线,它包括地址总线AB、数据总线DB和控制总线CB。本研究拟设计的CPU结构图如图1所示[10]。

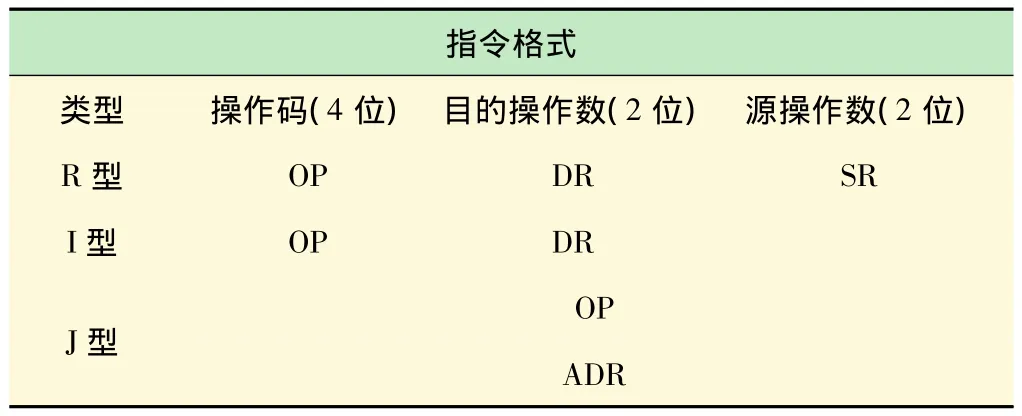

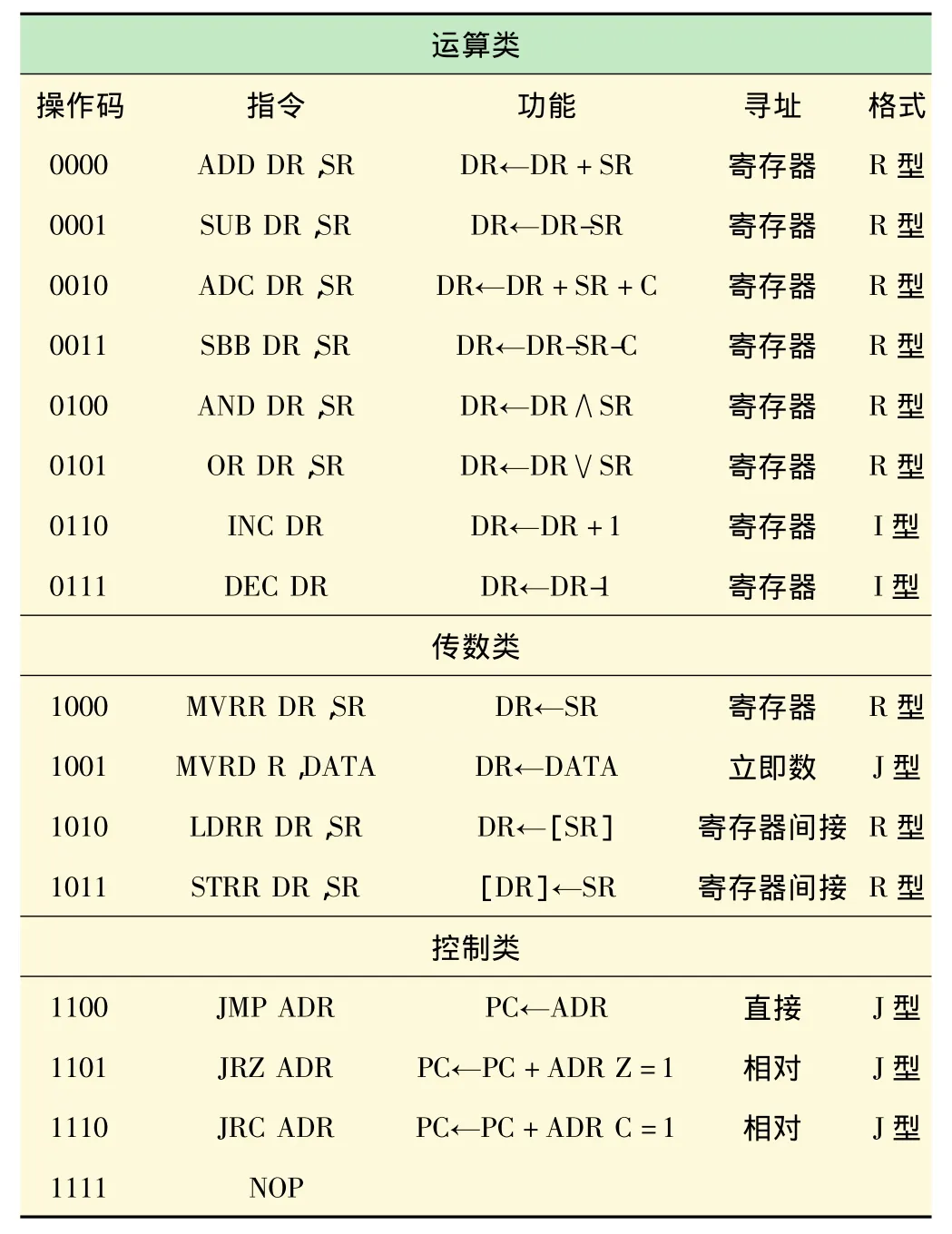

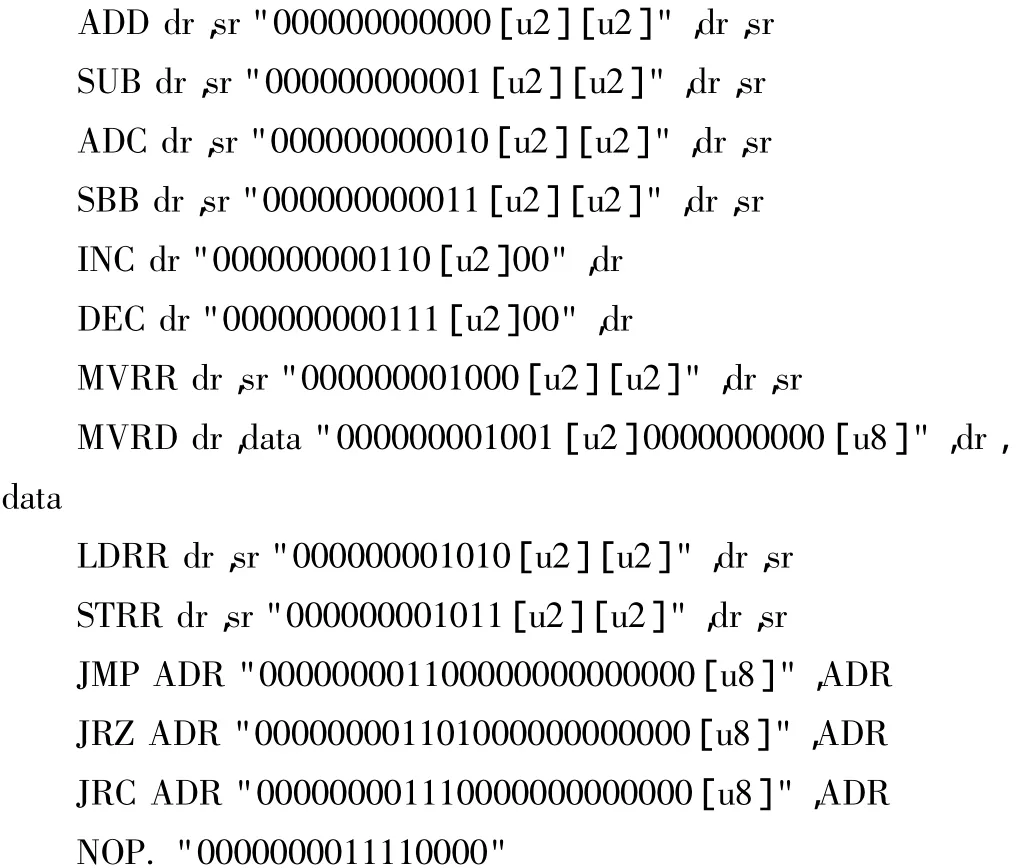

本研究设计的指令系统包含传送类指令、算术运算类指令、逻辑运算类指令和转移指令。本指令系统优先选取使用频率最高的一些简单指令,安排大多数指令在一个机器周期内完成;采用LDRR/STRR结构,即:只有LDRR(取数)和STRR(存数)两种指令可以访存,其余指令只能对存放在寄存器中的操作数进行处理;采用较少的寻址方式和单、双字长指令格式;控制部件采用可使速度提高的组合逻辑来实现。指令系统格式如表1所示,基本CPU指令集如表2所示。

2 实验CPU总体设计

2.1 时序节拍的设计

图1 RISC CPU结构图

表1 指令格式

表2 基本CPU指令集

实验CPU中控制器的时序设计为3个节拍t1、t2和t3,供实验CPU各部分使用。对单字长指令,t1节拍取指,对双字长指令,通过做标记在第二个t1节拍取指令的第2个字;t2节拍的上升沿将从存储器取出的指令写入指令寄存器IR中并根据指令寄存器IR的内容进行指令译码,然后根据译码得到的控制信号进行运算和其他操作;t3节拍对存储器进行读、写操作,在t3的下降沿将运算结果写入目的寄存器、改变标志位并改变PC的值并为取下条指令做准备。由于取指和存储器读写阶段都要访问存储器,速度较慢;而指令译码和运算都由CPU本身完成,因此取指阶段和存储器读写阶段各占一拍时间,指令译码和运算共占一拍时间。

2.2 CPU的总体构成

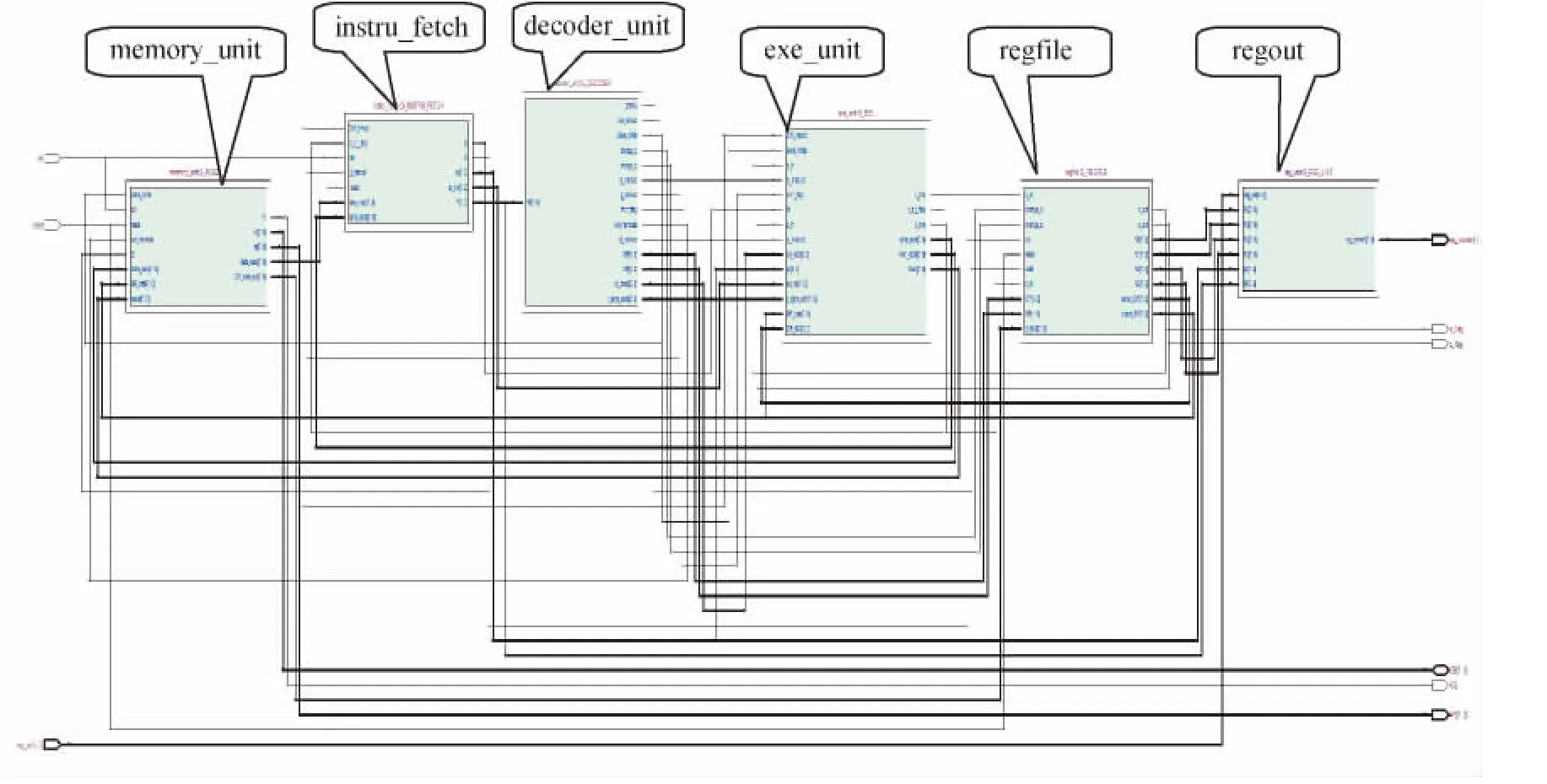

本研究的CPU由取指部分instru_fetch、指令译码部分 decoder_unit、执行部分 exe_unil、存储器部分memory_unit、通用寄存器组 regfile和寄存器输出regout 6个部分组成。程序包exe_cpu_components将各低层设计实体作为元件存储,供各设计实体使用。顶层设计实体exe_cpu完成6个组成部分的连接[11]。

(1)通用寄存器组(regfile)。通用寄存器组内包含4个8位寄存器,它是一个具有1个写入端口、2个读出端口的通用寄存器组。写入端口将指令执行后得到的目的寄存器的值在t3下降沿写入目的寄存器中。只有具有写目的寄存器功能的指令执行结束时才写目的寄存器。通用寄存器组的两个读出端,一个是目的寄存器读出端口,一个是源寄存器读出端口,从这两个端口读出的内容供执行部分exe_unit和存储器部分memory_unit使用。

(2)取指部分(instru_fetch)。取指部分首先在复位信号reset为低时将PC复位为0,在一条指令执行结束后,根据指令执行的结果在t3的下降沿改变PC的值;然后将从存储器读出的指令的第一个字在t2的上升沿送至指令寄存器IR;最后计算PC+1的值,为双字指令取第二个指令字做准备。

(3)指令译码部分(decoder_unit)。指令译码部分根据指令寄存器IR的值产生实验CPU所需要的各种控制信号,其中规定:SR[1..0]为源寄存器号;DR[1..0]为目的寄存器号;op_code[2..0]为控制 ALU进行8种运算操作的3位编码;zj_instruct为l表示本条指令是条“JZ ADR”指令;cj_instruct为1表示本条指令是条“JC ADR”指令;lj_instruct为1表示本条指令是条“JMP ADR”指令;DRWr为1表示在t3的下降沿将本条指令的执行结果写入目的寄存器;Mem_Write为l表示本条指令有存储器写操作,存储器的地址是源寄存器的内容;DW_instruct为1表示本条指令是双字指令;change_z为1表示本条指令可能改变Z标志;change_c为l表示本条指令可能改变C标志;sel_memdata为1表示本条指令写入目的寄存器的值来读自存储器;r_simp_addr为计算条件转移指令转移地址所需要的8位相对地址。它是从第2个指令字中读出的转移指令中的8位绝对或相对地址,在基于VHDL所设计的组台逻辑型CPU中指令译码器主要由逻辑判断语句来实现。

(4)执行部分(exe_unit)。执行部分完成:① 加法、减法、带进位加、带进位减、与、或、异或和数据传送这8种算术逻辑运算并临时将运算结果存放在result中;根据运算结果产生进位标志,临时存放在c_tmp中;根据运算结果产生结果为0的标志,临时存放在z_tmp中。② 产生存储器读写所需要的存储器地址Mem_Addr,该存储器地址在tl节拍时选择pc,在双字指令时选择pc_inc,在LDRR指令时选择SR内容,在STRR指令时选择DR内容。③ 产生条件转移指令(JC和JZ)所需要的转移标志c_z_j_flag(为l表示转移)和转移地址r_simp_addr。

(5)存储器部分(memory_unit)。存储器部分主要完成对存储器的读写,它是CPU和TEC_CA实验台上存储器的接口部分,该部分向实验台上的存储器送出8位存储器地址总线ar、8位双向数据总线ob、读写信号rw,当rw为l时对实验台上的存储器进行读操作;当rw信号为0时对实验台上的存储器进行写操作。试验台上的存储器由两片静态存储器6116和少量附加电路构成。在TEC_CA实验台上,两片6116并联构成8位字长的存储器,6116所需的片选信号cs为低信号,读信号oe由rw反相产生,写信号we直接选用rw。存储器地址ar来自执行部分,写信号Mem_Write由指令译码部分产生,当Mem_Write为1时在t3节拍完成写操作,其余情况下均进行读操作。对于单或双字长指令在t1节拍完成读指令的第1个字;对于双字指令,在t3节拍完成读指令的第2个字;对于JMP指令,在t3节拍读出转移地址放在data_read中;对于MVRD指令,在t3节拍读出立即数DATA放在data_read中;对于LDR指令在t3节拍读出存储器的值,放在data_read中;对于STRR指令,在t3节拍将源寄存器的值写入存储器中;在t3下降沿写入目的寄存器时,若是LDRR指令写入的数据来自存储器,其他指令写入的数据则来自执行部分送来的运算结果result。

(6)程序包(exp cpu compenents)。程序包exp_cpu_components把实验CPU中除顶层设计实体exp_cpu以外的设计实体作为元件(component)予以说明,供实验CPU中的其他设计实体作为元件予以引用。

(7)顶层设计实体(exe_cpu)。顶层设计实体exe_cpu把6个二级设计实体memory_unit、instru_fetch、decoder_unit、exe_unit、regfile 和 regout作为元件引用,每个例化一次,用信号把它们连接起来,构成实验CPU。exp_cpu所定义的clk为外部输入的时钟、reset为外部输入的CPU复位信号(低电平有效)、ar为向外部输出的8 b存储器地址总线;ob为8 b双向存储器数据总线;rw为向外部输出的存储器读写信号,当为高电平时对存储器进行读操作,当为低电平时对存储器进行写操作。

在一个工程中,较低层的设计实体相当于元件,与一块印制板上的电路差不多,顶层设计实体对较低层设计实体每例化一次,相当于在印制板上安放一个元件,而顶层设计实体中的信号相当于印制板上的连线[12]。因此,在一个工程中,如果有一个非顶层设计实体从来没有被其他设计实体例化过,那么这个设计实体在这个工程中就是多余的。顶层设计实体中除了包括由较低层设计实体构成的元件外,通常还有一些由process语句、信号赋值语句等构成的其他独立电路块,通过信号把元件和独立电路块连接起来,最后形成如图2所示的CPU完整设计图。

图2 CPU完整设计图

3 调试与测试

设计好 CPU工程并编译成功后,直接点击Quartus II工具栏的Programmer按钮,在Mode框中选择默认的 JTAG下载方式,确保下载硬件为ByteBlasterII[LPT1],如果不是的话,就点击Hardware Setup按钮来设置,完成上述过程后,选中需要下载的sof文件,点击Start开始下载到“WT-1型计算机系统硬件综合实验平台”,下载后打开调试软件,然后分别加载测试程序和规则文件,与表2所定义的指令系统对应的规则文件[13]如下:

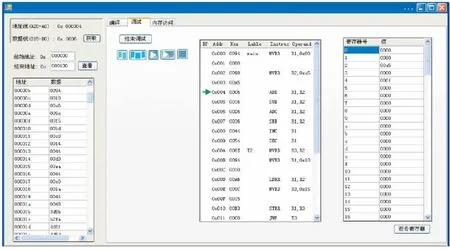

在调试软件中编译成功后再下载到内存,最后开始调试,通过查看寄存器的值来检测指令的功能是否成功,测试界面如图3所示,左边为测试程序在内存中的编码,中间是调试程序,右边是每条指令执行后的结果。“MVRD R1,0x80”指令执行完后,R1寄存器的内容为“0080”;“MVRD R2,0xa5”指令执行完后,R2 寄存器的内容为“00a5”;测试程序正执行到“ADD R1,R2”指令(见中间的绿色箭头),相加结果在指令执行完后将存入R1寄存器。

4 结语

本文研究了一个开放式CPU的设计过程,研究结果表明基于VHDL的计算机组成原理的整机实习为学生提供了一个灵活方便的计算机系统CPU设计的平台[14],优化了计算机整机实习设计,本文所设计的CPU结构、指令系统和指令格式都可以由学生进行个性化定义[15],而在实现技术方面学生可以利用HardCopy技术来实现,这一切在传统的教学内容、实验模式和实验手段上是没有的,是对传统计算机组成原理整机实习的彻底改革,使学生在了解计算机组成原理和软件设计技术的同时,学会了计算机硬件设计技术,这是一个合格的计算机专业学生本应具备的基本知识,离开了硬件设计,自主创新能力的培养便无从谈起,本设计方法充分提高了学生自行设计、调试和分析解决的能力,实现了计算机组成原理课程整机实习的全新改革。

图3 CPU测试界面

[1] 张 磊,郑 榕,田军峰.计算机组成原理理论实验教学无缝结合的新方法[J].实验室研究与探索,2013,32(5):168-171.

ZHANG Lei,ZHENG Rong,TIAN Jun-feng.Seamless Combination of Theoretical and Experimental Teaching for Computer Organization[J].Research and Exploration in Laboratory,2013,32(5):168-171.

[2] 马汉达,赵 蕙.计算机组成原理实验教学改革[J].计算机教育,2010,9(10):30-33.

MA Han-da, ZHAO Hui.Reform on Experiments Teaching of Computer Organization Principles[J].Computer Education,2010,9(10):30-33.

[3] 戚 梅,张 鹏.EDA技术在《计算机组成原理》实验教学中的应用[J].电子设计工程,2011,19(17):1-3.

QI Mei,ZHANG Peng.The Application of EDA Technology in Computer Principles Experiment Teaching[J].Electronic Design Engineering,2011,19(17):1-3.

[4] 李丽萍,盛琳阳.基于EDA技术的计算机组成原理实验课开放性教学模式研究[J].计算机教育,2010.5(10):55-57.

LI Li-ping,SHENG Lin-yang.Research on Open Educational Model of Technology Computer Composition Principle Experiment Class Based on EDA[J].Computer Education,2010.5(10):55-57.

[5] 陈 媛,黄贤英.基于EDA技术的计算机组成原理实验教学探索,重庆工学院学报[J].2007,21(2):136-138.

CHEN Yuan, HUANG Xian-ying. Exploration on Experimental Teaching of“Principle of Computer Organization”Based on EDA Technology[J].Journal of Chongqing Institute of Technology,2007,21(2):136-138.

[6] 翟文正,管功湖.EDA在《计算机组成与结构》课程设计中的实践与探索[J].微型电脑应用,2009,25(12):10-13.

ZHAI Wen-Zheng,GUANG Gong-hu.The Practice and Exploration of EDA in Curriculum Design of《Computer Organization &Architecture》[J].Microcomputer Applications,2009,25(12):10-13.

[7] 谭小兰,莫海燕,陈 多.基于EDA的计算机组成原理实验教学方案[J].湖南工程学院学报,2011,21(3):93-96.

TAN Xiao-lan,MO Hai-yan,CHEN Duo.Teaching Scheme of the Experiment on Principles of Computer Organization Based on EDA[J].Journal of Hu Nan Institute of Engineering,2011,21(3):93-96.

[8] 张 亮.应用EDA技术改革“计算机组成原理”课程设计[J].计算机教育,2009(9):40-42.

ZHANG Liang.Applying EDA Technology to Reform Curriculum Design of“Principle of Computer Organization”[J].Computer Education,2009(9):40-42.

[9] 陆明洲.基于Quartus II的计算机组成原理实验改革探索[J].高校实验室工作研究,2010,12(4):16-17.

LU Ming-zhou.The Reform and Exploration of the Experiment on Principles of Computer Organization Based on Quartus II[J].GAO XIAO SHI YAN SHI GONG ZUO YAN JIU,2010,12(4):16-17.

[10] 王爱英.计算机组成与结构[M].北京:清华大学出版社 2007:176-184.

[11] 潘 松,潘 明.现代计算机组成原理[M].北京:科学出版社,2007:112-138.

[12] 王艳萍,吴 兵.基于VHDL语言的CISC-CPU系统设计[J].山东理工大学学报,2009,23(4):79-81.

WANG Yan-ping,WU Bing.Design for CISC-CPU based on VHDL[J].Journal of Shandong University of Technology(Natural Science Edition),2009,23(4):79-81.

[13] 汤志忠,杨春武.开放式实验CPU设计[M].北京:清华大学出版社,2006:1-63.

[14] 汤书森,马义德.现代计算机组成原理课程特点与实验教学新模式探索[J].高等理科教育,2012:146-149.

TANG Shu-sen,MA Yi-de.On the Characteristics of Curriculum of Modern Computer Organization Principle and its New Model of Experimental Teaching[J].Higher Education of Sciences,2012:146-149.

[15] 方恺晴,张洪杰,方 红.关于提升“计算机组成原理实验"课程教学质量的探讨[J].实验室研究与探索,2008,27(3):97-100.

FANG Kai-qing,ZHANG Hong-jie,FANG Hong.Discussion on Enhancing the Teaching Quality aboutComputerComposition Principle Experiment[J].Research and Exploration in Laboratory,2008,27(3):97-100.

The CPU Design and Practice Based on VHDL

XU Aiping,ZHANG Yuping,TU Guoqing

(School of Computer,Wuhan University,Wuhan 430072,China)

With the development of Large large scale programmable logic devices,the EDA technology has became the an important means of the design on hardware system circuit.In general,the whole internship of the computer composition principle based on EDA is realized on by the simulation platform of Quartus II.In the early,the design approach of Block block Diagram diagram was used in practice.The design process is intuitive,but the simulation and debugging is are difficult and can't succeed completely.In this paper,the a flexible and convenient design process on CPU is researched.The design is composed of six parts that are instruction fetch,instruction decode,instruction execution,memory interface,general register and register output.At last,the accuracy of design is validated through register observed directly by debug software.It possess very good guiding significance and actual reference value to reform the whole internship of this course,plays aan active initiative androle for improve improving the independent creative ability of students.

computer principle;central processing unit design;whole internship;VHDL(Vhsic Hardware Description Language )

TP 332

A

1006-7167(2014)05-0120-05

2013-07-26

武汉大学计算机学院教学实践改革项目

徐爱萍(1962-),女,湖北武汉人,博士,教授,研究方向:组成原理课程教学与实践、Web服务、时空统计。

Tel.:13971471468;E-mail:xap1464@126.com