三维芯片中TSV链式冗余修复电路的设计与实现*

2014-03-23赵振宇刘海斌

袁 强,赵振宇,窦 强,李 鹏,刘海斌

(国防科学技术大学计算机学院,湖南长沙410073)

YUAN Qiang,ZHAO Zhen-yu,DOU Qiang,LI Peng,LIU Hai-bin

(College of Computer,National University of Defense Technology,Changsha 410073,China)

1 引言

随着超大规模集成电路的快速发展及应用要求的不断提高,传统的二维平面集成电路芯片在集成规模、速度和功耗等方面已经遇到发展瓶颈,迫切需要引入新型器件、新型工艺来满足更高要求。三维集成技术的出现使得这些问题的解决成为可能。硅通孔TSV(Through Silicon Via)[1]作为三维芯片中不同层之间的垂直互连结构,具有高密度、低功耗、高带宽等特点。采用TSV技术不仅能提供大量的互连资源、有效地降低延时和功耗,而且能避免相关的成本、设计复杂度增加等问题,使得摩尔定律继续适应于集成电路的发展,甚至可以超越摩尔定律。

然而当前的TSV技术还未完全成熟,在TSV制作或晶圆绑定过程中会出现一些失效TSV,这些失效TSV会导致由其互连的模块失效甚至整个三维芯片的失效,这会降低芯片的良品率[2],带来巨大的成本开销。因此,采用具有修复失效TSV功能的设计对提高三维芯片的良品率和降低芯片成本都具有极大的帮助。

目前国内外已经有很多研究机构和芯片厂商关注三维芯片中TSV可靠性研究并做了大量相关的工作,较为突出的有IBM、IMEC、MIT、Duke大学、ITRI、清华大学和合肥工业大学等,他们的研究主要集中在冗余修复结构上面。文献[3]提出了一种双倍TSV冗余结构,该结构虽然修复率较高但面积开销很大,且相邻TSV之间的信号易产生串扰。文献[4]提出了TSV链式冗余结构,通过将多个TSVs划分并互连为一条链,同时在每条链上增加一个冗余TSV,实现多个TSV共用一个冗余TSV来进行故障修复。文献[5]在文献[4]的基础上进行了改进,两者原理基本相同,只是为了减少信号移位带来的时序影响,在TSV两端加入了两个缓冲器(Buffer)。文献[6,7]分别提出了多链式的冗余结构和基于交叉开关的链式冗余结构。两种结构都是采用将多个TSVs划分成一条TSV链,然后增加冗余TSV进行冗余修复,但它们都存在每次只能修复单条TSV链中的一个失效TSV的不足。针对这一不足,通过对TSV失效率的分析和预估,在综合考虑了修复率和面积开销(多路选择器MUX、冗余电路)等因素之后,本文提出了一种基于TSV链式结构的单/双冗余修复电路结构,能够在单条TSV链上同时修复一个或两个失效TSV,并进行了冗余修复电路的设计与实现,通过实验说明了其功能的正确性,根据失效率预估表也表明该结构具有较高的修复率。

2 TSV失效分析

TSV是三维芯片中引入的新型互连结构,它在传统的二维芯片中并不存在。因此,需要考虑三维芯片的制作或加工处理过程中是否会产生TSV故障,这些故障是否会引起TSV失效,以及如何去统计TSV失效分布等,这些都是值得研究的课题。

2.1 TSV失效原因

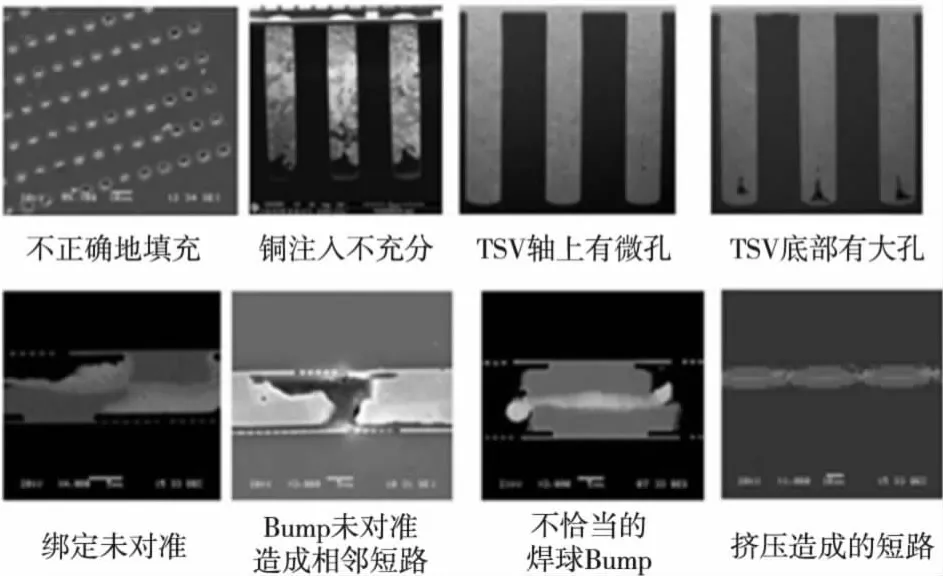

目前,受限于TSV制作和芯片封装工艺,TSV失效主要由绝缘层短路、凸点开路和延迟故障三种缺陷引起。

在绑定前TSV的制作过程中,绝缘层生长瑕疵和侧壁裂痕、绑定材料电阻变化等都可能造成TSV缺陷,导电铜注入不均,易产生空隙造成TSV开路缺陷。晶圆绑定阶段,绑定压力过大容易造成TSV断裂或裂纹,绑定层表面氧化或污染等都可能造成TSV失效。晶圆堆叠时,由于TSV直径非常小(3μm~5μm),不易全部准确地对准,可能会造成大量的TSV失效,相邻TSV之间的信号干扰是造成串扰故障的主要原因。综合以上分析,如图1所示为IMEC(Interuniversity Microelectronics Center)提供的产生失效TSV的可能情况[8]。

Figure 1 Reasons of producing failure TSV from IMEC图1 产生失效TSV的原因(IMEC)

2.2 TSV失效率分析

由于三维芯片结构可以应用于多核处理器、片上网络NoC(Network on Chip)、IP模块等各种不同设计,因此三维芯片各层的TSV数量规模一般不同,少则成百,多则上万。据相关研究[9]表明:现今封装工艺下,单个TSV的失效率大约为10-4~10-5。假设相邻TSV之间的失效是相互独立的,由二项分布概率公式可得:

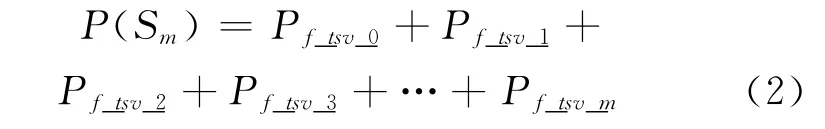

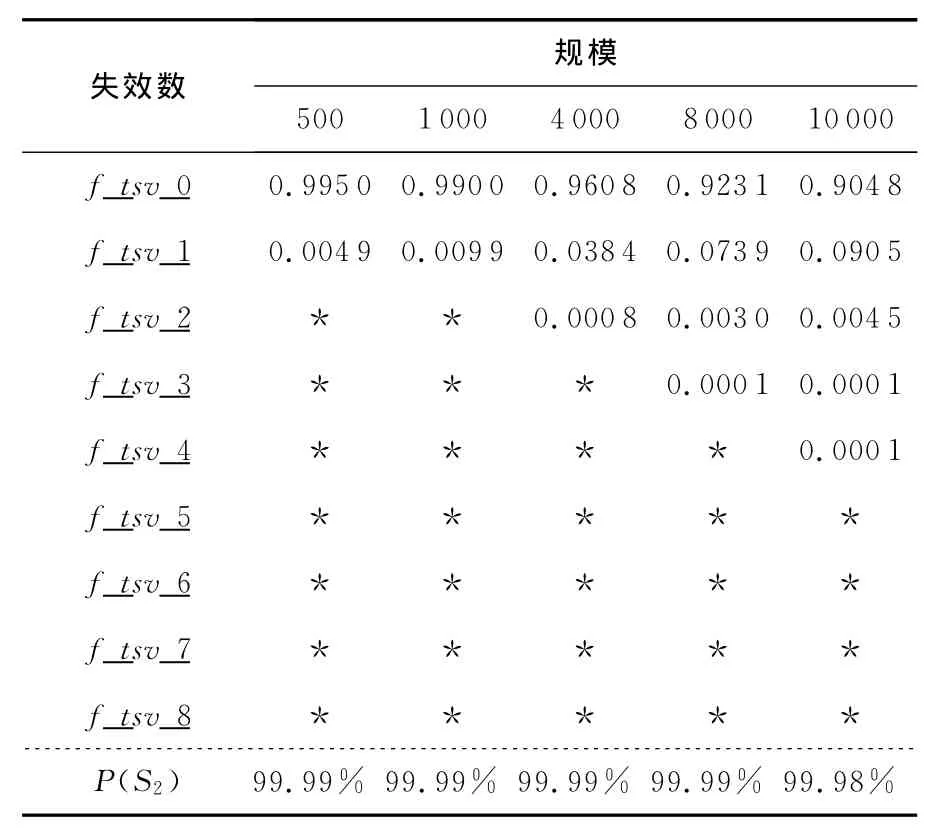

其中,F为三维芯片中单个TSV的失效率;N为三维芯片中TSV总数;Pf_tsv_n为三维芯片中出现n个TSV失效时的概率。同理,可以得到三维芯片的整体修复率,即:

P(Sm)为不采用任何冗余方案时,整个三维芯片中失效TSV数≤m时的修复率。根据公式(1)和公式(2)可计算出三维芯片中TSV数量规模分别为500、1 000、4 000、8 000、10 000时,整个三维芯片中失效TSV数n≤2时的修复率P(S2),使用Matlab工具计算,其结果分别如表1、表2所示。

Table 1 The P(S2)of failure TSV number≤2 in whole 3D chip when not using any redundancy scheme and the failure of single TSV is 10-5表1 当单个TSV的失效率为10-5时,整个三维芯片中失效TSV数n≤2时的修复率P(S2)(不采用任何冗余方案)

Table 2 The P(S2)of failure TSV Number≤2 in whole 3D chip when not using any redundancy scheme and the failure of single TSV is 10-4表2 当单个TSV的失效率为10-4时,整个三维芯片中失效TSV数n≤2时的修复率P(S2)(不采用任何冗余方案)

由表1和表2可知,在三维芯片中,随着失效TSV数量n的变化,其所影响芯片的整体修复率也各不相同。其中“*”表示该值非常小,可忽略不计。

由此可见,可以根据三维芯片内的TSV总数来预估失效TSV的个数。例如,假设单个TSV的失效率为10-4时,当TSV数量规模N为4 000时,所确定的失效TSV个数n为2,因此只要确保能修复这两个失效TSV,就可以使三维芯片的整体修复率至少达到99.21%。

3 TSV链式冗余修复结构

3.1 TSV链式单冗余修复结构

TSV链式单冗余结构是指将三维芯片中的多个TSVs互连成一条链,单条TSV链式上只增加一个冗余TSV的链式结构。

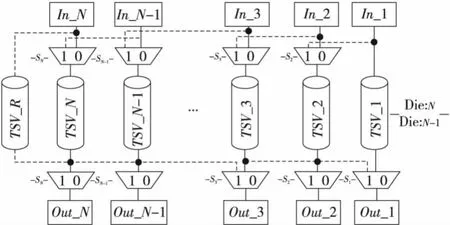

三维堆叠芯片中相邻堆叠层结构图如图2所示,TSV_1、TSV_2、TSV_3、…、TSV_N-1、TSV_N分别代表TSV链式上从右到左的各个信号TSV,每个信号TSV两端分别增加一个二选一多路选择器(MUX2);TSV_R代表增加的冗余TSV,其两端不需增加MUX2,且第一个信号TSV输入端可以节省一个MUX2,当TSV正常时,MUX2选择0端口传输信号,当TSV失效时,MUX2选择1端口传输信号,图2中的实线和虚线分别表示TSV正常和失效时的传输路径。

Figure 2 Sketch map of single-redundancy TSV chain structure图2 TSV链式单冗余结构示意图

当该结构工作时,三维芯片上下层模块之间的功能信号通过MUX2进行选择传输,MUX2的选择是由修复控制电路决定的。其工作原理为:通过芯片测试后得到TSV链上的每个信号TSV失效情况及其故障定位,产生控制信号去控制修复电路对TSV链进行冗余修复。当其中某个信号TSV失效时,利用控制信号将通过故障TSV的初始信号转移到相邻无故障的TSV中传输。以此类推,直到该TSV链式结构的最后一个初始TSV信号转移到备用的冗余TSV中进行传输,使得故障TSV能够修复。

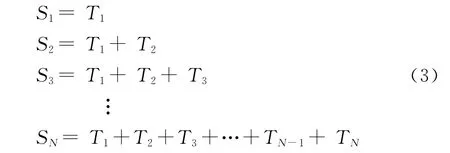

如图3所示为TSV链式单冗余修复结构的控制电路,T1、T2、T3、…、TN-1、TN分别表示TSV链式中经芯片测试后产生的各个TSV控制信号。SN表示MUX2的控制信号输入,根据信号传输路径可以推导出控制信号的表达式如(3)所示:

Figure 3 Control circuit structure of single-redundancy TSV chain图3 TSV链式单冗余结构的控制电路图

3.2 TSV链式双冗余修复结构

TSV链式双冗余结构是指将三维芯片中的多个TSVs互连成一条链,单条TSV链上增加两个冗余TSV的链式结构。

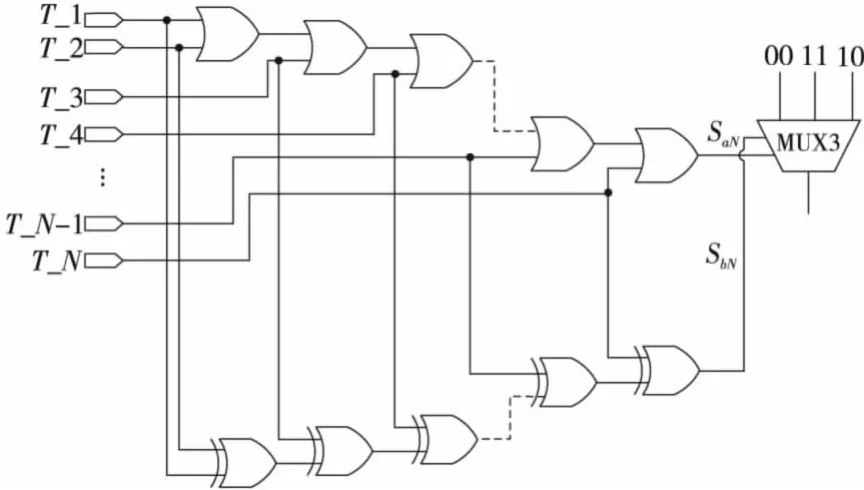

如图4所示,该结构是基于TSV链式单冗余修复结构进行的改进设计,通过在一条链上增加两个TSV,然后采用三选一多路选择器(MUX3)来控制TSV信号传输路径。其主要思想类似于TSV链式单冗余修复结构,同样是将通过故障TSV的信号转移到相邻无故障的TSV中进行传输,以此完成故障TSV的修复。然而,对于TSV链式双冗余修复结构,其不仅要能够修复TSV链上单个TSV失效,而且还需要修复TSV链中两个TSV同时失效的情况。显然这将增加修复电路的复杂性,同时给设计带来挑战。

综合考虑以上因素,本文设计出了TSV链式双冗余修复电路结构,其工作原理:当信号TSV都无故障时,MUX3选择00端口传输信号;当有一个TSV失效时,MUX3选择11端口传输信号;当有两个TSV同时失效时,MUX3选择10端口传输信号。如图4所示,当TSV链中信号TSV出现故障时,其右边无故障的信号TSV将按实线正常传输信号,而通过故障TSV的信号将会依次转移到左边无故障的TSV中进行传输(虚线标识路径)。

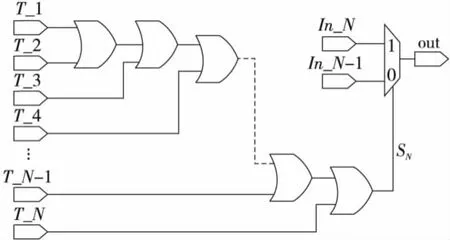

TSV链式双冗余修复结构的控制电路如图5所示。

Figure 5 Control circuit structure of dual-redundancy TSV chain图5 TSV链式双冗余结构的控制电路图

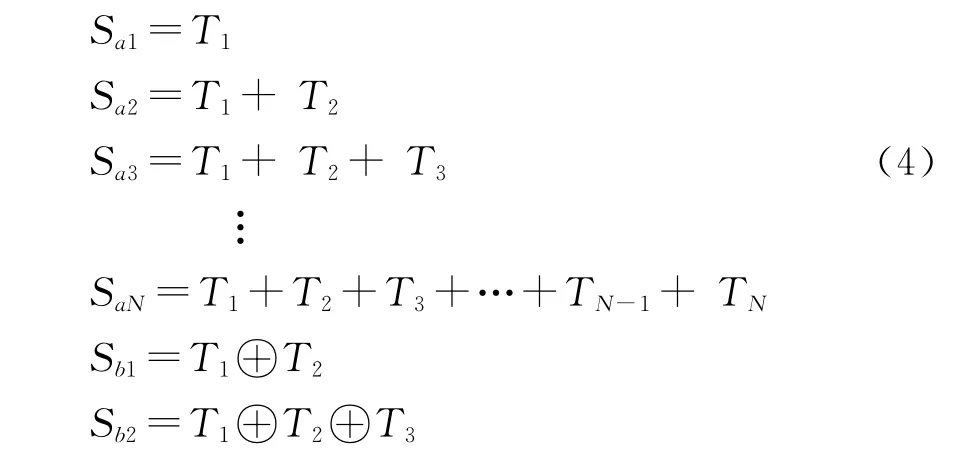

T1、T2、T3、…、TN-1、TN分别代表控制电路的输入端口(芯片测试后产生),SaN、SbN为MUX3的使能控制端口(如图6所示),根据TSV的失效情况及传输路径,可以推导出MUX3的使能控制信号SaN、SbN表达式分别如公式(4)和公式(5)所示:

Figure 4 Sketch map of dual-redundancy TSV chain structure图4 TSV链式双冗余结构示意图

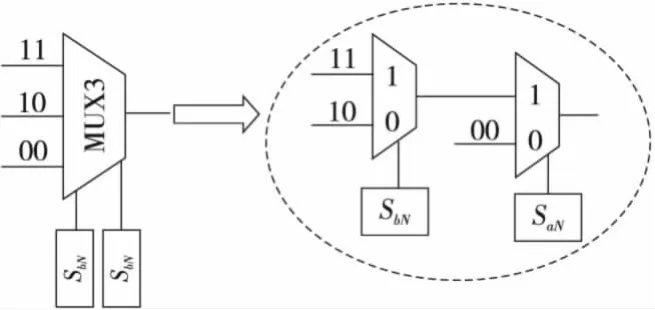

如图6所示为MUX3的内部电路结构,当SaNSbN=00时,表示TSV没有故障时的信号传输路径端口;当SaNSbN=11时,表示有一个失效TSV时的信号传输路径端口;当SaNSbN=10时,表示有两个失效TSV时的信号传输路径端口。

Figure 6 Internal circuit structure of MUX3图6 MUX3的内部电路结构

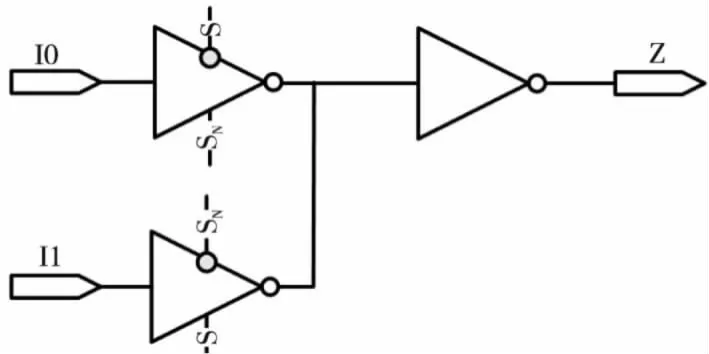

MUX3由两个MUX2构成,MUX2的内部电路结构如图7所示。该结构相比而言面积开销较小,延时较优。

Figure 7 Internal circuit structure of MUX2图7 MUX2的内部电路结构

4 仿真与分析

4.1 单冗余仿真实验

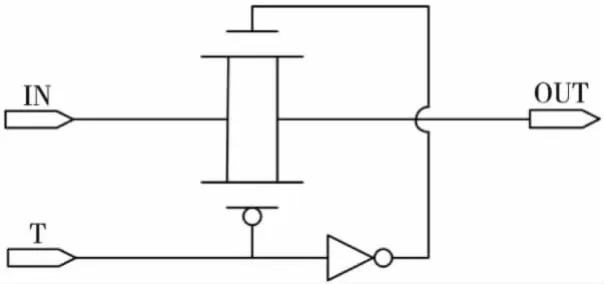

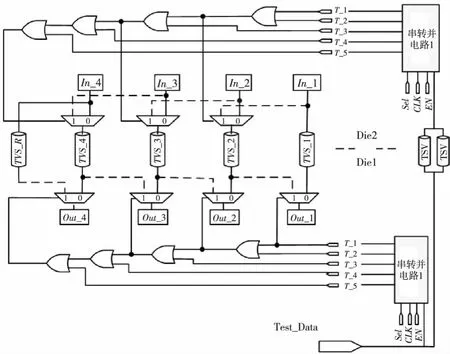

本实验基于典型的两层堆叠三维芯片,利用Virtuoso和HSPICE工具,选取的TSV链中信号TSV数量都为4,分别进行TSV链式单冗余修复电路仿真和双冗余修复电路仿真实验。其主要的单冗余修复电路如图8所示,由于业界目前没有统一的TSV模型标准,本文实验在不影响设计目标的前提下,TSV采用传输门结构(如图9所示),当TSV正常时,传输门导通,当TSV失效时,传输门关闭。传输门的控制信号同样由T_1、T_2、T_3、T_4、T_5控制,当它们为0时导通,相反为1时关闭。

Figure 9 Internal circuit structure of TSV图9 TSV的内部电路结构

利用HSPICE进行仿真,当施加给TSV链上四个信号in〈1〉、in〈2〉、in〈3〉、in〈4〉输入电压波形如图10所示,遍历TSV无故障及有一个失效的情况下,其输出仿真结果如图11所示。从图11中可以看到模拟输出电压结果out〈1〉、out〈2〉、out〈3〉、out〈4〉与输入电压波形功能一致,图中出现了一定的延时及电压降(0.9 V~0.899 998 V),主要是由于控制电路为组合逻辑,这验证了电路功能的正确性。

Figure 8 Single-redundancy circuit structure of TSV chain with 4 signal TSVs图8 含4个信号TSV的TSV链式单冗余电路结构

4.2 双冗余仿真实验

Figure 10 Input simulation wave chart of single-redundancy TSV chain structure图10 TSV链式单冗余结构仿真输入波形图

Figure 11 Output simulation wave chart of single-redundancy TSV chain structure图11 TSV链式单冗余结构仿真输出波形图

Figure 12 Dual-redundancy circuit structure of TSV chain with 4 signal TSV图12 含4个信号TSV的TSV链式双冗余电路结构

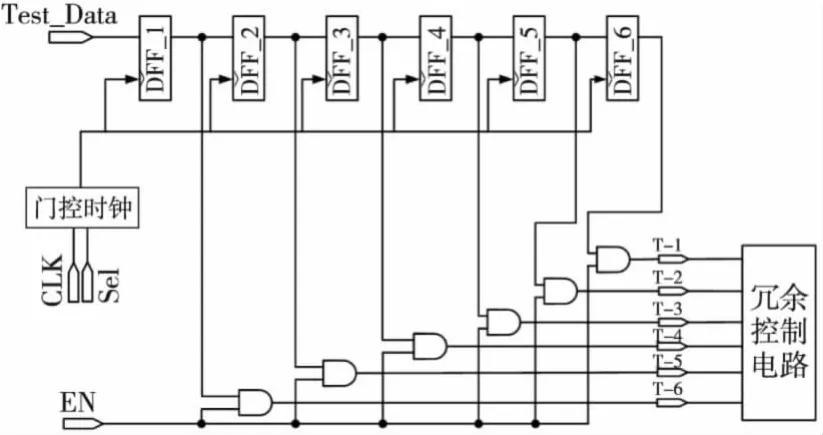

实验基于四个信号TSV、两个冗余TSV进行链式冗余结构设计,其双冗余修复电路如图12所示。芯片测试后经过测试电路中的扫描链扫描出串行的测试数据,如0100010、000001等,这时需要将其通过串转并电路2(图13所示),将串行输入转换为并行输出并以此作为冗余控制电路的输入,测试数据Test_Data经过CLK和使能EN端控制,前五拍处于保持状态,在第六拍进行并行输出;同时Test_Data需要从Die1传输到Die2,在设计时采用Double TSV结构,确保了信号传输的可靠性。

Figure 13 Internal structure of series transform parallel circuit图13 串转并电路的内部结构

值得注意的是,由于控制电路为组合逻辑,它不具有存储记忆功能,设计中通过门控时钟控制时钟CLK的工作通断,不仅可以降低功耗,而且还可以使触发器中的数据保持不变。同理,图8中的串转并电路1,设计时只需要五个DFF和五个AND2门便可构成。

利用HSPICE进行仿真,TSV链上四个输入信号in〈1〉、in〈2〉、in〈3〉、in〈4〉的输入和输出波形如图14所示,当遍历TSV无故障、有一个TSV失效、有两个TSV同时失效时的所有情况下,其输出仿真结果如图14所示,通过对比输入和输出波形可以看出,控制电路功能正确,且达到预期的修复目的。此外,本实验中未使用的MUX3端口统一接地处理。

5 结束语

本文提出了一种针对三维芯片中失效TSV的链式双冗余修复方案,并对TSV链式单冗余/双冗余修复电路进行了设计与功能实现。该方案基于TSV链式单冗余结构,通过多增加一个冗余TSV来完成两个故障TSV的修复;此外,TSV链式双冗余还考虑到其中一个冗余TSV失效的情况,并能对其进行修复。实验结果表明,该冗余修复电路功能正确,同时通过逻辑门的复用,降低了控制电路的面积开销,根据失效率估算统计表可知,该结构可以使三维芯片整体修复率达到91.97%以上,从而提高了芯片的成品率并确保了芯片的高可靠性。

Figure 14 Input and output simulation wave chart of dual-redundancy TSV chain structure图14 TSV链式双冗余结构仿真输入和输出波形图

[1] Banerjee K,Souri S J,Saraswat K C,et al.3-D ICs:A novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration[J].Proc of the IEEE,2001,89(5):602-633.

[2] Xu Qiang,Li Jiang,Eklow B,et al.Yield enhancement for 3D-stacked ICs:Recent advances and challenges[C]∥Proc of Asia South Pacic Des Autom Conference,2012:731-737.

[3] Lung Chiao-ling,Chien Jui-hung,Shi Yi-yu,et al.TSV faulttolerant mechanisms with application to 3D clock networks[C]∥Proc of SoC Design Conference(ISOCC),2011:127-130.

[4] Loi I,Mitra S,Lee T H,et al.A low-overhead fault tolerance scheme for TSV-based 3D network on chip links[C]∥Proc of the IEEE/ACM International Conference on CAD,2008:598-602.

[5] Hsieh A-C,Hwang T-T,Chang M-T,et al.TSV redundancy:Architecture and design issues in 3D IC[C]∥Proc of IEEE/ACM Design,Automation,and Test in Europe,2010:166-171.

[6] Wang Wei,Dong Fu-di,Chen Tian,et al.3D-SIC TSV faulttolerant scheme based on multi-chains[J].Computer Engineering and Applications,2012,48(20):75-80.(in Chinese)[7] Wang Wei,Dong Fu-di,Fang Fang,et al.Multi-chain type configurable fault-tolerant scheme in 3D-SIC[J].Electronic Measurement and Instrument,2012,26(2):126-131.(in Chinese)

[8] Noia B.Pre-bond and post-bond test solutions for 3D stacked ICs[Z].Durham:Duke University,2012.

[9] Miyakawa.A 3D prototyping chip based on a wafer-level stacking technology[C]∥Prcoc of Design Automation Conference,2009:416-420.

附中文参考文献:

[6] 王伟,董福弟,陈田,等.一种多链式结构的3D-SIC过硅通孔(TSV)容错方案[J].计算机工程与应用,2012,48(20):75-80.

[7] 王伟,董福弟,方芳,等.3D-SIC中多链式可配置容错结构[J].电子测量与仪器学报,2012,26(2):126-131.