CMOS工艺中NPN bipolar的开发

2014-03-22崔金洪

崔金洪

(深圳方正微电子有限公司,广东 深圳 518116)

CMOS工艺中NPN bipolar的开发

崔金洪

(深圳方正微电子有限公司,广东 深圳 518116)

由于技术的迅速发展与突破,使集成电路的制造得以在短短的60年间,单一晶粒已经可以容纳数千万个电晶体的超大型集成电路。其主要工艺为CMOS工艺,原因是它有功耗低、集成度高、噪声低、抗辐射能力强等优点,但是传统bipolar工艺有频率高、功率大的优点,因此提出在CMOS中集成三极管、二极管。论述了在0.5 μm CMOS工艺中集成NPN bipolar的方法以及各个关键技术指标的确定。

互补型场效应晶体管;双极;实验设计;击穿电压

1 引言

CMOS(Complementary Metal-Oxide Semiconductor)集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通、另一个管截止的状态,电路静态功耗理论上为零。CMOS集成电路工作电压范围宽,供电简单,供电电源体积小,基本上不需稳压。由于其功耗很低,内部发热量少,且线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。CMOS集成电路抗辐射能力强,基本器件是MOS晶体管,属于多数载流子导电器件。各种射线、辐射对其导电性能的影响都有限,特别适用于制作航天及核实验设备。其可控性好,CMOS集成电路输出波形的上升和下降时间可以控制。接口方便,因为CMOS集成电路的输入阻抗高、输出摆幅大,所以易于被其他电路所驱动,也容易驱动其他类型的电路或器件。而与CMOS工艺相比bipolar工艺较老,bipolar工艺虽然没有CMOS工艺的以上优点,但是bipolar器件可以用电流控制,可用于高频、大功率等应用。所以这里要在0.5 μm CMOS工艺流程中加入zener二极管与bipolar三极管。

2 CMOS集成NPN方法

2.1具体方法

这里用N+对应三极管的发射极,N阱对应三极管的收集极,缺少P型基区,在栅氧氧化前增加P型基区光刻和注入,形成图1所示结构。

2.2三极管测试方法

表1是三极管测试的业界标准。

表1 三极管业界标准

图1 三极管结构剖面图

2.3实验一

在P型基区注入步骤做不同注入剂量实验,具体方案见表2。

表2 P型基区注入剂量拉偏

由表2可见只有3号和4号片能测试出Beta在P型基区注入步骤做不同注入剂量实验时,可见剂量选在5×1013~7×1013可以测试出放大倍数。3号片P型基区注入能量40 keV、剂量5×1013的输出特性曲线见图2。

图2 输出特性曲线

2.4实验二

在P型基区注入步骤做不同注入能量实验,具体方案见表3。由表3可见1~3号片能测试出放大倍数,1号片条件较优,从表3的放大倍数变化趋势可见,P型基区注入大导致放大倍数小,需要减小在P型基区的注入剂量。1号片P型基区注入能量60 keV、剂量2×1013的输出特性曲线和放大倍数与IC的关系曲线如图3。

表3 P型基区注入剂量拉偏

图3 输出特性曲线和放大倍数与IC的关系曲线

2.5实验三

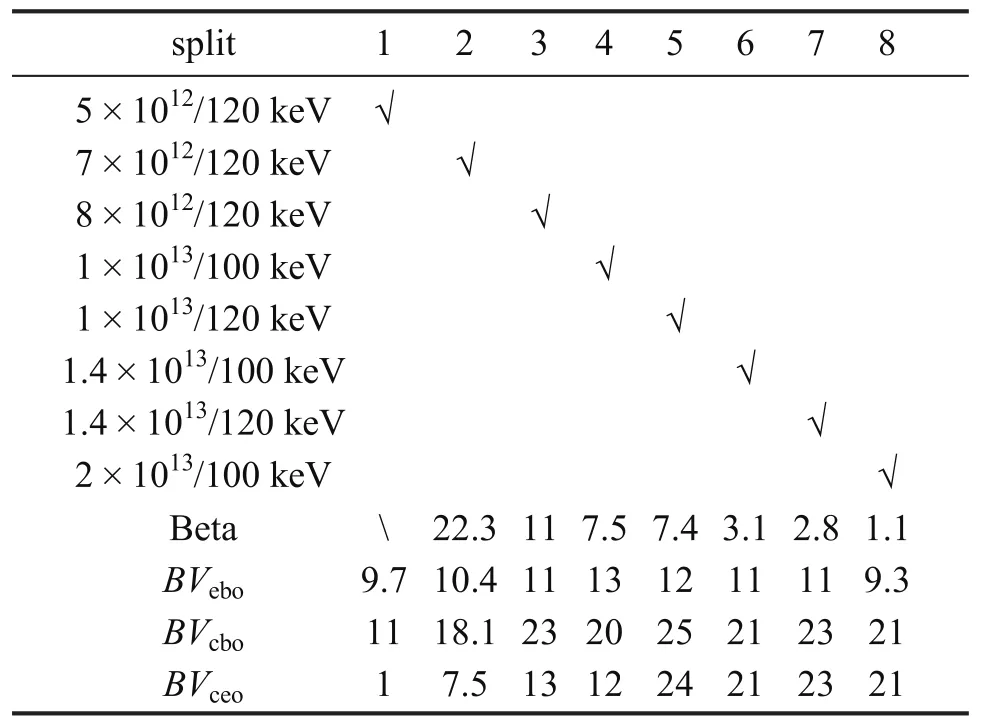

表4 P型基区注入剂量和能量拉偏

在P型基区注入步骤做不同注入能量和不同注入剂量实验,具体方案见表4。

由表4可见2号片P型基区注入能量120 keV、剂量7×1012满足三极管测试标准。1号片由于基区穿通而无法测试出放大倍数。

Beta=22.3 @Vce=5 V &Ib=1 μABVebo=10.4 V ;BVcbo=18.1 V;BVceo=7.5 V

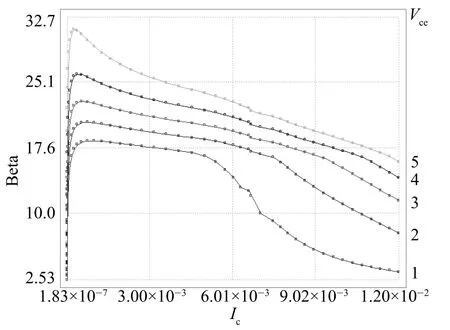

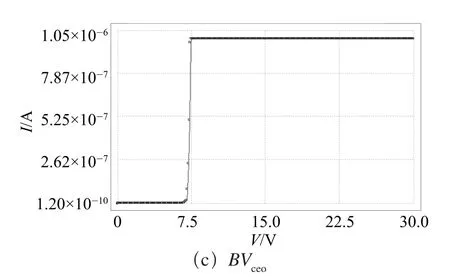

2号片P型基区注入能量120 keV、剂量7×1012的输出特性曲线和放大倍数与IC的关系曲线以及BVebo、BVcbo、BVceo曲线依次如图4~图6所示。

图4 输出特性曲线

图5 放大倍数与IC的关系曲线

图6 BVebo、BVcbo、BVceo曲线

3 结论

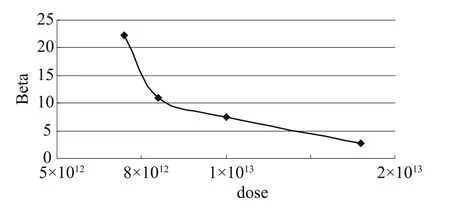

在CMOS中集成NPN三极管,可以用N+对应三极管的发射极,N阱对应三极管的收集极,在栅氧氧化前增加P型基区光刻和注入,形成基区,P型基区注入能量120 keV、剂量7×1012满足参数设计要求。由实验数据可得放大倍数与P型基区注入剂量的关系如图7所示。

图7 放大倍数与P型基区注入剂量的关系曲线

[1] R JACOB BAKER. CMOS集成电路设计手册[M]. 北京:人民邮电出版社,2014. 181-213.

[2] Alan Hastings. 模拟电路版图的艺术[M]. 北京:电子工业出版社,2012. 262-307.

[3] S M SZE. 半导体器件物理[M]. 西安:西安交通大学业出版社,2008. 186-215.

The Development of CMOS Technology in NPN Bipolar

CUI Jinhong

(Founder Microelectronics International Co.,Ltd.,Shenzhen518116,China)

Due to the rapid development of growth and breakthrough technology, the manufacture of integrated circuits in a short span of 60 years, single grain can accommodate tens of millions of transistors ultra large integrated circuit, and the main process of the CMOS process, because it has low power consumption, integration high, low noise, the advantages of strong ability of resisting radiation, but the traditional bipolar technology has the advantages of high frequency, power, so want to integration in the CMOS tube triode, diode. The paper discusses the method of integration of NPN bipolar in 0.5 μm CMOS process, the shutdown technology index.

CMOS; bipolar; DOE; BV

TN305

A

1681-1070(2014)11-0034-03

崔金洪(1985—),男,辽宁本溪人,工程师,主要研究方向为集成电路工艺、器件可靠性。

2014-08-07