快速恢复外延二极管用硅外延片的工艺研究

2014-03-22王文林李明达

王文林,李 扬,陈 涛,李明达

(中国电子科技集团公司第46研究所,天津 300220)

快速恢复外延二极管用硅外延片的工艺研究

王文林,李 扬,陈 涛,李明达

(中国电子科技集团公司第46研究所,天津 300220)

利用化学气相沉积方法制备所需硅外延层,通过FTIR(傅里叶变换红外线光谱分析)、C-V(电容-电压测试)、SRP(扩展电阻技术)等多种测试方法获取外延层的几何参数、电学参数以及过渡区形貌。详细研究了本征层生长工艺与外延层厚度分布、电阻率分布以及过渡区形貌之间的对应关系。采用该优化设计的硅外延材料,成功提高了FRED器件的性能与成品率。

快恢复二极管;硅外延片;本征层生长;过渡区

1 引言

随着高频大功率半导体器件研发和制造技术的快速发展,其在电子电路中的应用越来越多样化,尤以IGBT(绝缘栅双极型晶体管)、VDMOS(垂直双扩散金属-氧化物半导体场效应晶体管)为代表的功率开关器件在生活中的应用愈加广泛和深入,其需求量十分巨大[1~2]。随着开关器件的工作频率和性能的不断提高,采用快速恢复外延二极管(Fast Recovery Epitaxial Diode,FRED)与之配套,可以避免主开关器件的电热击穿,进而提高了器件的可靠性和使用寿命。因此对其快速开通和高速关断能力提出了越来越严格的要求,同样也面临着巨大的挑战[3]。采用肖特基势垒二极管虽具有极低的通态压降和反向恢复时间,但因耐压普遍低于200 V而难以在高压领域应用[4]。而采用PIN结构的FRED,其耐压值最高可达几千伏,反向恢复时间可低于30 ns,已在脉宽调制器、变频调速器、超声波电源以及各种开关电源等电子电路中发挥着重要的作用,并向更短反向恢复时间、更大电流容量、更快开关速度、更低导通电压以及更高工作电压的方向发展[5]。因此FRED器件的研究开发和应用将极大推动新型高频大功率半导体器件的快速发展,受到了国内外多所研究机构的高度重视和积极参与,具有十分重要的现实意义[4~6]。

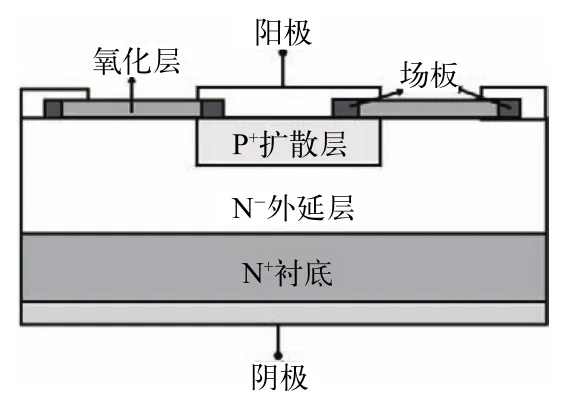

目前硅材料仍是制备FRED的关键基础材料,这主要源于硅材料储量丰富、价格低廉、工艺简单。硅基PIN结构FRED的典型剖面图如图1所示,主要由重掺杂的阳极P+扩散层、本征I区以及重掺杂的阴极N+衬底三部分组成[7]。中间I基区通常由低掺杂的N-外延层代替,具有很高的电阻率。相对于双扩散片,使用外延片作为基片可以使FRED器件展现更好的一致性、更高的耐压性能、更快的恢复时间以及更低的正向压降。

图1 FRED典型剖面结构示意图

外延层质量的好坏直接影响到器件的性能、成品率和可靠性。随着器件小型化和集成度的提高,对高质量的硅外延片的需求也愈发迫切。目前国内功率FRED器件常用硅外延片的直径为127 mm、152.4 mm,随着外延片表面积的增大,表面颗粒、结晶质量、外延层厚度和电阻率参数及其均匀性的严格控制技术尤为关键。为承受高反向电压,PN结的耗尽层主要位于N-外延层。同时在外延层参数设计时不仅需要考虑满足击穿电压的要求,还要尽量降低反向漏电流。为保证器件的性能、成品率和可靠性,通常要求外延层电阻率和厚度的径向偏差尽可能小,并具有极低的表面颗粒和晶格缺陷密度。此外,外延层与硅衬底接触形成的过渡区结构应平滑、陡峭,同时过渡区宽度应尽量缩短以降低导通电阻。相反,过宽的过渡区会严重降低外延层的有效厚度,减小外延片的击穿电压,增加参数的控制难度,进而造成器件成品率的下降。

目前普遍认为采用CVD(化学气相沉积)技术在重掺As的硅衬底上制备均匀分布的高阻外延层较为困难[9],这是由于两个原因造成的:(1)FRED用外延片的外延层掺杂浓度(~l014cm-3)与衬底的掺杂浓度(~l019cm-3)相差5个数量级,衬底向外延层的固态扩散成为影响外延层过渡区宽度的主要因素;(2)外延生长时的气相自掺杂效应也会使衬底与外延层界面处的杂质浓度过高,造成边界层加宽,减少了外延层的有效厚度。现有研究表明,在外延生长初期先高温淀积本征层可显著改善过渡区结构,尤其可以明显降低厚外延层生长时的纵向扩散效应[8]。本文通过调节本征层生长工艺,有效阻止了衬底杂质从表面、背面和边缘处的逸出及向外延层的扩散,减弱了纵向自掺杂效应,最终使过渡区结构达到理想效果,并满足器件使用要求。

2 工艺试验

2.1外延设备

本文沉积硅外延层的设备为PE-2061S型常压桶式外延炉,基本结构如图2所示。该外延炉采用高频感应的加热方式,具有维护简单、生产效率高的特点,尤其适合厚外延层的生长。外延炉内以立式桶状高纯石墨基座作为加热感应体,由8个中心对称的正梯形侧面组成,每个侧面分三排,共可放置24片127 mm硅抛光片。基座的旋转速度设定为4 r/min。

图2 外延炉结构示意图

2.2衬底材料与外延结构

为满足FRED器件的指标要求,本文选用高质量的进口硅衬底进行外延生长,以期得到高质量的外延片。衬底材料选用重掺As的N型单晶硅抛光片,其直径为125 mm,晶向为<111>,晶向偏离度为4.0°±0.5°,厚度为525±15 μm,电阻率小于0.003 Ω·cm,径向电阻率变化≤15%。本工艺制备的外延层导电类型为N型,直径为125 mm,厚度设计为38±2.0 μm,径向厚度变化≤3%,电阻率设计为18±2.0 Ω·cm,表面径向电阻率变化≤5%。

2.3工艺技术

本文采用常压外延工艺,反应室压力维持在0.1 MPa。同时结合多晶硅质量转移技术,即在外延生长之前用高纯度HCl在高温下对石墨基座进行腐蚀处理,以去除基座表面残余的沉积物。为了进一步抑制基座上的杂质向外挥发,本文采用高纯度三氯氢硅(SiHCl3)作为硅源,在石墨基座表面淀积一层20 μm厚的非掺杂多晶硅。随后,将衬底紧贴放置在包硅处理后的基座片坑内。在外延生长中,先采用3 L/min的高纯HC1进行5~10 min的气相抛光,随后在H2气氛下对衬底进行1 130 ℃的高温烘焙,烘焙时间为3 min,以去除硅衬底表面的残留杂质,得到的洁净表面可满足外延生长对晶格质量的要求。同时基座表面上的多晶硅向衬底背面迁移,阻止了背面杂质的进一步蒸发,完成自背封效应。该效应减少了自掺杂的影响,可以使外延层电阻率的均匀性得到良好的控制。外延生长中采用的反应气体为SiHCl3和H2,起主要载气作用的H2经纯化后的纯度为99.999 99%,作为硅源的SiHCl3纯度为99.95%,其本征电阻率高于1 000 Ω·cm。由于SiHCl3常温下为液态,采用H2鼓泡的形式成为气态进入反应室。衬底表面发生的主要化学反应为[10]:

采用两步外延生长工艺进行所需外延层的生长。第一步外延生长是在硅抛光表面生长近本征层,对衬底片表面及边缘进行包封处理。采用的工艺参数如下:生长温度设定为1 130 ℃,H2流量设定为320 L/min,硅源流量设定为15 L/min。为研究本征生长工艺对外延层表面质量、几何参数和电学参数的影响,本文将近本征层生长工艺的时间分别设定为1 min、2 min和3 min。近本征层生长结束后,采用320 L/min的高流量H2对反应室吹扫5 min,使杂质浓度降到最低,从而减小了外延生长的自掺杂效应。

第二步外延生长即在生长有近本征外延层的表面继续生长一层电阻率和厚度符合器件要求的掺杂外延层。生长温度设定为1 130 ℃,H2流量设定为320 L/min,硅源流量设定为28 L/min,生长速率控制在1.1 μm/min,直至预定的外延厚度为止。选用合适的生长温度和生长速率以保证外延片表面质量的同时维持较高的生产效率。外延生长时掺杂剂采用PH3,流量设定为33.7 sccm。

3 实验结果及分析

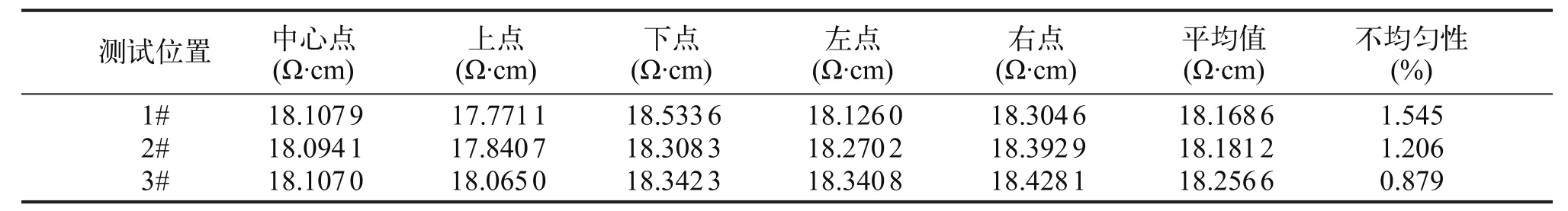

本文选取基座固定位置的外延片进行表面质量、几何参数和电学参数的测试。对本征生长时间分别为1 min、2 min和3 min的硅外延片,对应命名为1#、2#和3#样品。外延层的表面质量采用CMM-70E金相显微镜观测。外延层厚度利用Nicolet 6700傅里叶变换红外光谱仪(FTIR)测量,分辨率为0.001 µm。测试位置选取硅片的中心点及4个距边缘10 mm的测试点,如图3所示,外延层厚度测试结果如表1所示。外延层的表面电阻率利用SSM 495汞探针C-V测试仪同样进行5点法测试,分辨率为0.000 1 Ω·cm,测试结果如表2所示。对于本文制备的N型外延层,C-V测试前需在表面生长极薄且致密的氧化层。具体方法为:样品首先在20%浓度的HF溶液中浸泡3 min以除去表面的自然氧化层,然后把样品置于85 ℃下浓度为15%的H2O2溶液,浸泡10 min后取出。

图3 外延片的测试位置

采用金相显微镜观测到硅外延片的表面平滑、光亮,其表面无雾、划道、沾污、层错、崩边、裂纹、桔皮及滑移线等缺陷。根据表1和表2所示的参数结果,获得的各测试片的厚度不均匀性小于1%,电阻率不均匀性小于2%,完全满足FRED器件的制作要求。同时表2表明随着本征生长时间的有效延长,电阻率的不均匀性明显开始降低,当本征生长时间到达3 min时,不均匀性可低于1%。因此延长本征生长时间可显著改善外延层表面电阻率的均匀性。

表1 不同本征生长时间的测试片厚度

利用SRP 2000型扩展电阻测试仪分析了外延片的纵向载流子分布。根据国际半导体设备和材料协会(SEMI)标准,本文对过渡区宽度的定义为:衬底载流子浓度的90%所对应的厚度至外延层载流子浓度的110%所对应的厚度。

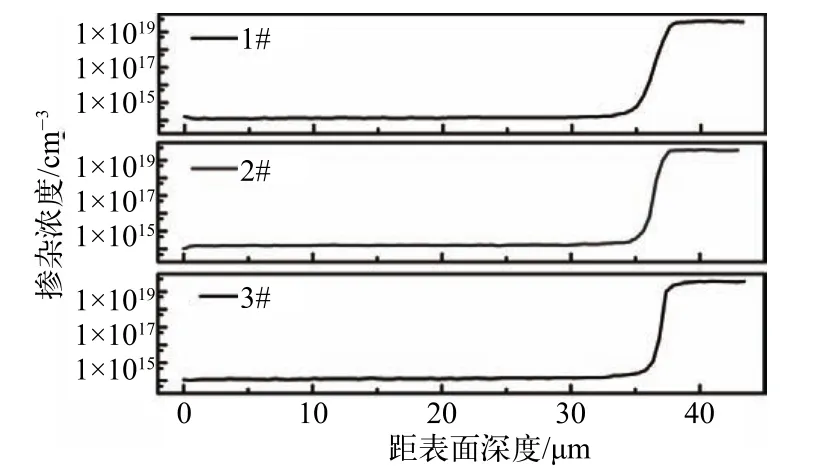

图4所示为本征生长工艺分别为1 min、2 min和3 min时获得的外延层掺杂浓度纵向分布曲线。图中1#、2#、3#样品的过渡区宽度经测试分别为3.11 µm、2.56 µm和2.03 µm,均可满足FRED用外延片的技术要求。而不同规格样品过渡区宽度之间的差异主要来源于自掺杂效应,因而强烈影响了外延层纵向载流子浓度分布的均匀性。图中3#样品的衬底与外延层界面处的过渡区宽度最窄,这是由于本征生长时间的有效延长显著减少了外延生长过程的自掺杂效应,载流子浓度梯度变化更加陡直,减小了过渡区的宽度。

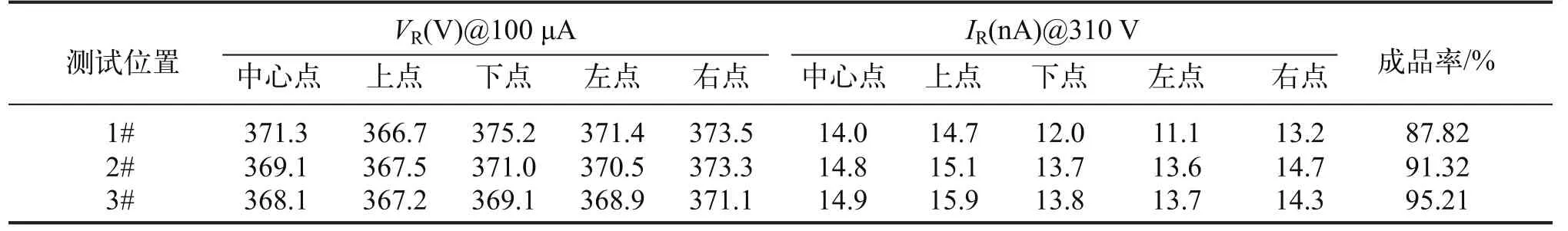

利用以上三种规格的硅外延片制备的FRED器件经厂商测试,其反向击穿电压(VR)和反向漏电流(IR)的测试结果如表3所示。各规格外延片均可满足FRED器件的要求,其中3#样品由于片内电阻率及厚度参数一致性更好,使其击穿压降和漏电流的分布更加均匀,因而最终提高了FRED器件的性能与成品率。

图4 外延层的纵向载流子分布

表2 不同本征生长时间的测试片的表面电阻率

表3 不同规格外延片制备的FRED器件的击穿电压(VR)和漏电流(IR)测试值

4 结论

本文主要研究了快速恢复外延二极管用硅外延片的制备方法,主要通过调节本征生长工艺的方法,有效地降低了自掺杂效应,改善了电阻率分布的不均匀性,同时缩短了过渡区的宽度。现已成功地研制出满足器件所需的硅外延材料,外延层晶体结构完整,厚度不均匀性<1%,电阻率不均匀性<1%,过渡区宽度<3 µm,进而有效提高了FRED器件的性能与成品率。

[1] 薛兵. 功率VDMOS用硅外延材料的制备[J]. 甘肃科技,2011,27(6):9-10.

[2] 马林宝,顾爱军. 功率VDMOS器件用硅外延材料研制[J]. 电子与封装,2011,11(9):38-42.

[3] 韦文生,戴瑜兴,张正江,等. PIN型快速恢复二极管的研究与应用[J]. 材料导报,2012,26(10):17-20.

[4] 张海涛,张斌. 大功率快速软恢复二极管概述[J]. 半导体情报,2001,38(3):1-8.

[5] 尹启堂,李玉柱,安涛,等. 双基区大功率快恢复二极管的研究[J]. 半导体技术,2010,35(2):129-132.

[6] J Vobecky, V Komarnitskyy, V Zahlava. Molybdenum and low-temperature annealing of a silicon power P-i-N diode [J]. Microelectronics Reliability, 2011, 51: 566-571.

[7] S M Kang, T J Eom, S J Kim, et al. Reverse recovery characteristics and defect distribution in an electronirradiated silicon p–n junction diode [J]. Materials Chemistry and Physics, 2004, 84:187-191.

[8] 王海红,高翔. 外延参数稳定性控制方法[J]. 电子与封装,2014,14(4):38-41.

[9] 徐非. 功率VDMOS器件用N/N+型外延层过渡区的研究[J]. 科技创新导报,2013,31:26.

[10] 王文林,闫锋,李杨,等. CVD法制备高质量硅外廷片的工艺研究[J]. 科技信息,2013:435-437.

The Research of the Process on the Silicon Epitaxial Wafers Used for the Fast Recovery Epitaxial Diodes

WANG Wenlin, LI Yang, CHEN Tao, LI Mingda

(China Electronics Technology Group Corporation No.46Research Institute,Tianjin300220,China)

Using the method of chemical vapor deposition(CVD), the required silicon epitaxial layer was prepared, and the geometry parameter, the electricity parameter as well as the transition region morphology was analyzed by using some testing methods such as FTIR(Fourier-Transform Infrared Spectrophotometry),C-V, SRP(spreading resistance profile)and so on. The relationship between the intrinsic layer growth process and the thickness distribution, resistivity distribution as well as transition topography of epitaxial layer was studied in detail. With the optimized design of silicon epitaxial material in the paper, the performance and yield of FRED were successfully improved.

fast recovery diode; silicon epitaxial wafer; growth of intrinsic layer; transition region

TN304

A

1681-1070(2014)11-0037-04

王文林(1960—),男,天津人,高级工程师,现在中国电子科技集团公司第46研究所工作,主要从事硅外延工艺技术的研究和产品开发。

2014-08-07