基于VPX的6U信号处理系统设计

2014-03-22苟欢敏

苟欢敏,薛 培,杨 芳

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于VPX的6U信号处理系统设计

苟欢敏,薛 培,杨 芳

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

VPX总线标准具有带宽高、实时性强、拓扑结构灵活、通用性强、抗恶劣环境能力强等优点,代表着新一代军用综合信息处理平台系统的发展方向[1]。设计一种基于VPX标准的6U信号处理系统,该系统提供了高带宽,支持串行Rapid IO以及PCIE等高速数据传输,为数据的高速交换提供了可能,满足了现代雷达、图像等信号处理系统对带宽和数据处理能力的要求。

信号处理;VPX;串行Rapid IO;PCIE

1 引言

随着信息技术的发展,对于信号处理系统处理器的处理能力、系统数据带宽、系统可重构能力提出了更高要求[1],尤其在蓬勃发展的电信、航天和航空领域。传统的总线结构已不适应当前系统的要求[2]。基于VPX标准的信号处理平台具备强大的信号处理、数据处理能力,以及I/O能力和高性能网络交换能力。正因如此,VPX标准代表了新一代综合信息处理平台系统的发展趋势和方向[3]。

2 VPX总线介绍

高速串行VITA46总线标准,相对于VME总线架构而言,具有更大的数据吞吐能力和交换能力、更好的散热性能和更高功率的插槽,充分满足了信号处理系统对带宽和运算处理能力的要求。VPX标准全部采用高速高密度接插件,串行可达10 Gbps,大幅度提高了系统带宽及系统设计的灵活性,支持高速串行Rapid IO、PCIE通信协议等,定义了交换槽,支持集中式及分布式等交换方式[4]。VPX总线标准具有以下突出优点和先进性:

(1)具备强大的I/O能力和高性能网络交换能力来支持更高的背板带宽,为信号处理提供了足够的带宽和处理能力。VPX标准可全面支持当前的高速串行互联标准,这些标准包括SRIO、PCIE、Rocket IO、G bit Ethernet等,同时大大增加了用户可定义的I/O针数,为未来的升级扩展提供了充分的空间。(2)VPX标准对VPX板卡的外形尺寸、背板的拓扑结构、支持各种串行标准协议时的电源插座等都作了详细的定义,这为信号处理平台的通用化打下坚实基础。(3)VPX标准专门针对关键高性能系统制定,其优秀的散热性能和高可靠的连接器带给系统超强的稳定性,同时具有结构坚固紧凑、磁兼容性好、强化电路板和超大功率设计等特点[3]。

3 信号处理系统设计

本文在VPX总线标准体系下,构建了一种新型的高性能处理系统,系统采用多块板卡并行处理、以完成实时处理任务,各板卡通过VPX背板实现内部数据交互。整个系统采用全网络结构,通过SRIO、PCIE、Rocket IO、CAN、RS-422、LVDS和GPIO等接口进行内部数据连通,既能保证高的传输带宽,又具有高的可靠性[5]。整个系统组成包括VPX机箱、接口板、信号处理板和CPU板。VPX机箱采用5U加固式机箱,电源采用双冗余电源设计,VPX板卡通过带定位销、导轨安装。所有板卡安装在VPX机箱内部[4]。系统处理流程为:数据输入到接口板,然后接口板将处理后的数据传送到多块信号处理板,信号处理板再将处理后的数据传送给接口板输出。

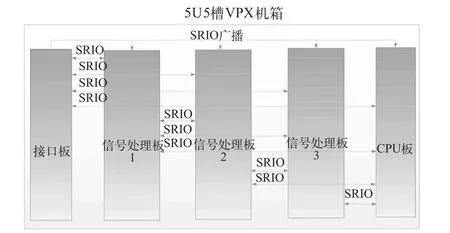

3.1整体方案

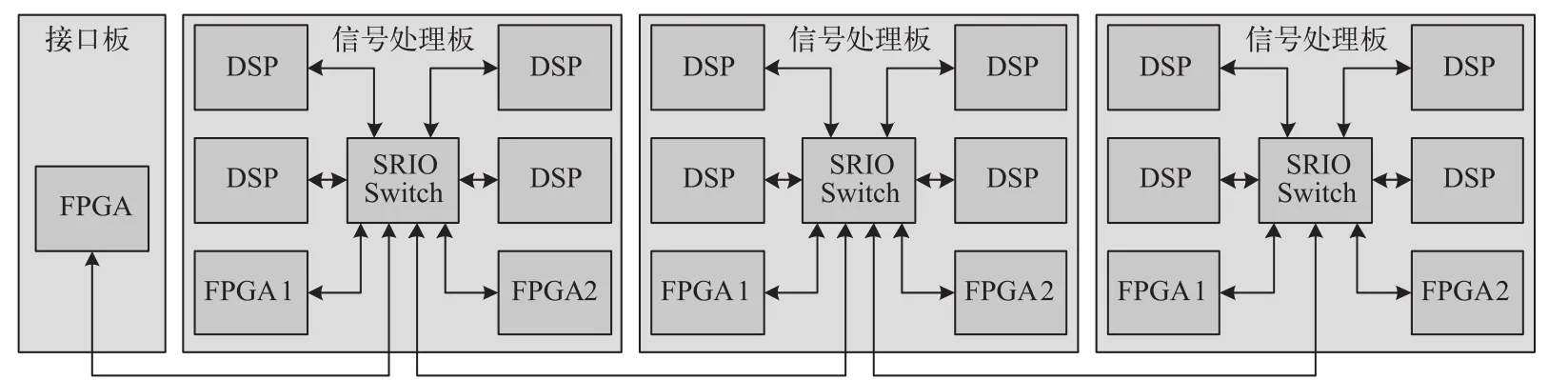

信号处理系统采用1块接口板+3块信号处理板+1块CPU板的结构进行设计。各板卡之间采用6U 5槽VPX背板进行连接。接口板负责完成对外对内的信息传输和指令交互,3块信号处理板主要完成相应的信号处理,接口板和信号处理板间通过SRIO网络进行图像的广播式传输和指令信息的点对点交互,CPU板实现对信号处理板上DSP的程序加载及监控,信号处理系统连接架构如图1所示。

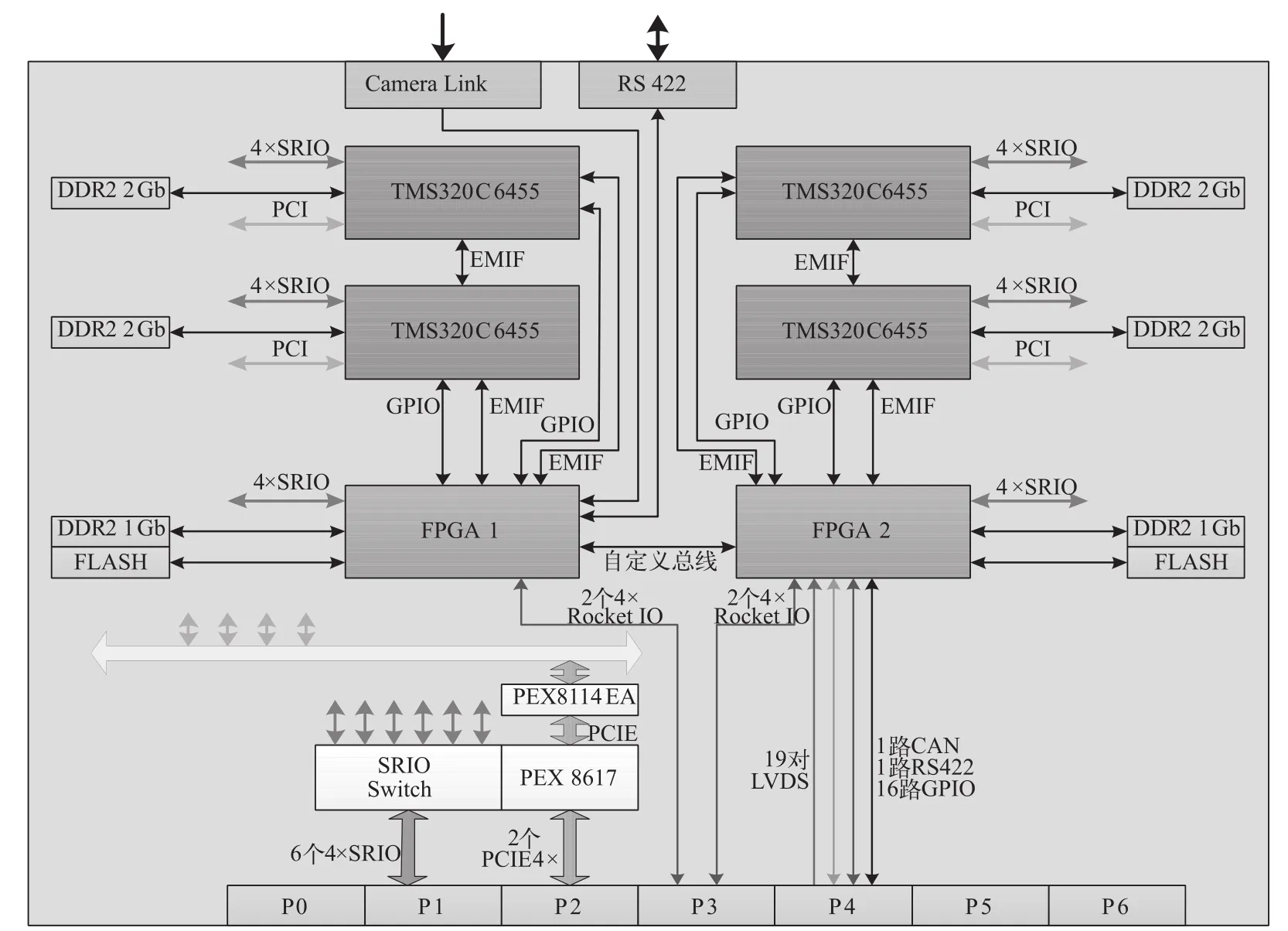

3.2接口板设计

接口板主要实现对外、对内的接口通信功能,将接收到的信息发送给信号处理板进行处理。接口板以两块FPGA为核心,通过FPGA完成对控制命令的解析分发和信号数据流的传递,板内还需要DDR存储器完成信息存储操作,以实现对数据的缓存处理。接口板结构框图如图2所示。

图1 信号处理系统连接架构框图

3.3信号处理板

信号处理板是信号处理的核心组件,实现3块信号处理板进行相应的信号处理。信号处理板采用4 DSP+2 FPGA架构,FPGA与DSP间通过SRIO 交换芯片连接,并与背板的SRIO信号相连,形成可以数据交互的SRIO网络,方便数据传输。信号处理板结构如图3所示。

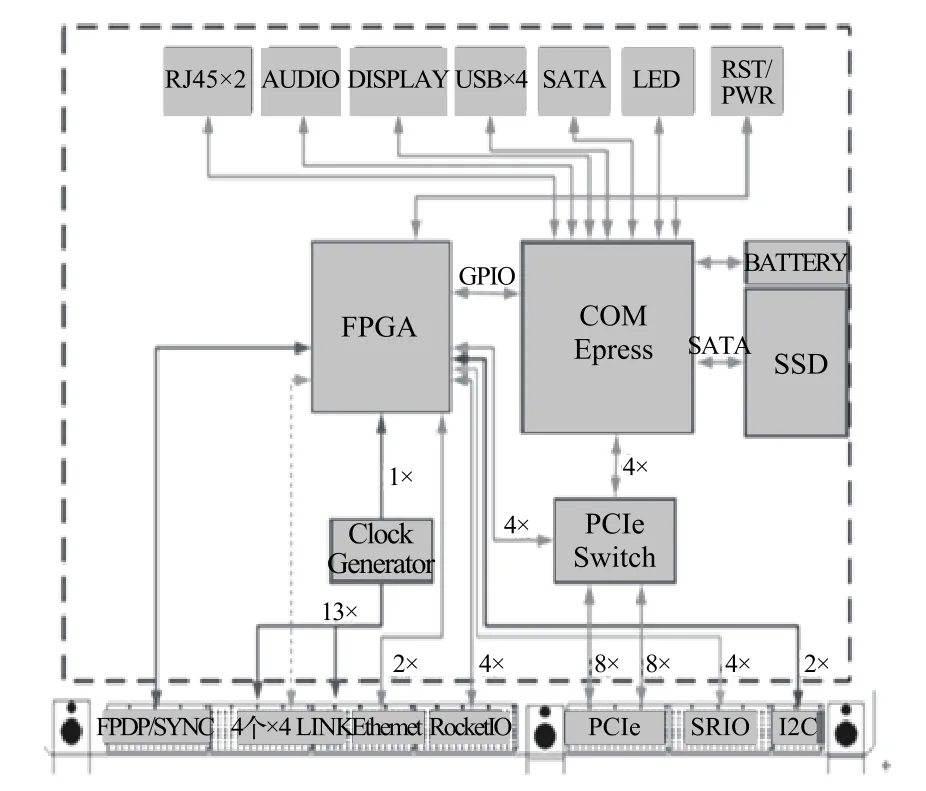

3.4 CPU板

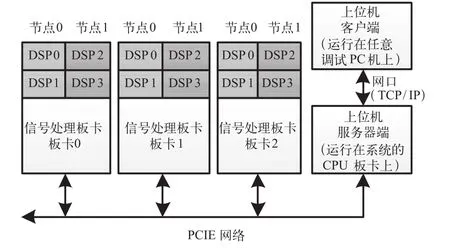

CPU板是系统调试的重要手段。CPU板通过PCIE网络可以实现对信号处理板卡上DSP程序加载、读写内存等调试操作,每个信号处理板上的DSP也可以通过PCIE网络将处理结果上传到CPU板进行结果显示,方便系统调试。CPU板结构图如图4所示。

3.5内部接口设计

内部接口是通过各板卡底板接插件和VPX背板实现内部数据交互,主要包括SRIO网络、PCIE网络、Rocket IO接口、CAN接口、RS-422接口、LVDS接口和GPIO接口进行内部数据连通。背板信号连接关系如图5所示。

SRIO网络是信号处理系统内部数据交换的核心,通过利用SRIO 交换芯片与VPX背板设计SRIO的全网络结构来实现接口板上的FPGA与信号处理板的FPGA、DSP间的数据交互。

通过进行相应的芯片配置,保证SRIO网络传输速率2.5 Gbps,内部SRIO网络连接如图6所示。

图2 接口板结构框图

图3 信号处理板结构框图

3.6机箱背板设计

机箱是整个信号处理系统的安装平台,应该严格保证系统的结构坚固、工作稳定、散热充分等要求。该系统由5U 标准19”VPX机箱、6U 5槽定制VPX背板、定制模块电源组成,并采用高性能风导冷散热设计,满足高性能应用需求。

图4 CPU板结构框图

图5 VPX背板连接框图

图6 内部SRIO网络连接示意图

3.6.1 机箱设计

机箱采用高强度铝镁合金型材,机箱内安装定制VPX背板,支持5块标准6U VPX板卡,由机箱前部水平插拔;机箱内部的导冷卡架,用于安装导冷板卡和散热。机箱电源采用定制模块电源,支持18~36 V宽电源输入,工作稳定、可靠。电源供电方式采用螺柱接线形式,满足冲击、振动等恶劣环境要求。

3.6.2 背板设计

背板遵循VITA46,支持6U欧洲标准卡,在机箱内水平安装,采用水平插卡方式;支持Serial Rapid IO、PCI Express等高速串行协议;背板支持的速率为2.5 Gbps。背板布局示意图如图8所示。

图7 机箱结构示意图

图8 背板布局示意图

4 系统验证

本文所设计的信号处理系统最终实物如图9,主要完成显控系统和光电前端间的指令分发与图像传输,并对图像信息进行实时处理,同时本信号处理系统需要具备灵活性、可拓展性、易实施性、体积小、质量轻、功耗低等特点。

图9 信号处理系统实物图

4.1 SRIO网络测试

系统内Rapid IO的互连关系如图10所示。系统中有3片交换芯片互联,通过对交换芯片不同类型ID分配来实现不同的数据流功能。通过测试,配置不同数据流模式,实现了接口板FPGA向3个DSP板的12片6455和6片FPGA广播发送同样的数据;系统内1片接口板FPGA、12片6455和6片FPGA不定时的点对点互相发送数据;接口板FPGA向其中1片DSP0发送数据,DSP0预处理后,广播发送到其他11片DSP和6片FPGA;可见接口板和信号处理板间通过SRIO网络可以可靠地进行图像的广播式传输和指令信息的点对点交互。

4.2 PCIE网络测试

信号处理板通过CPU板采用PCIE总线进行调试,其中通过上位机软件可以进行信号处理板卡的DSP程序加载、复位,信号处理板读写DSP内存功能,信号处理板内存数据图像化显示。使用上位机软件对信号处理板卡进行测试的示意图如图11所示。

图10 Rapid IO的互连关系图

图11 上位机软件测试示意图

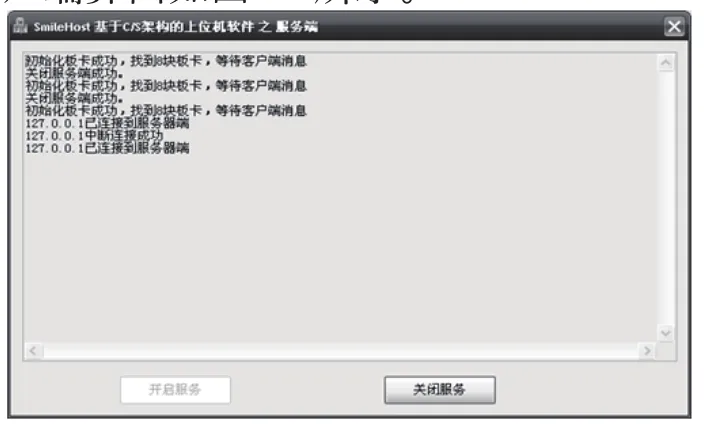

服务器端界面如图12所示。

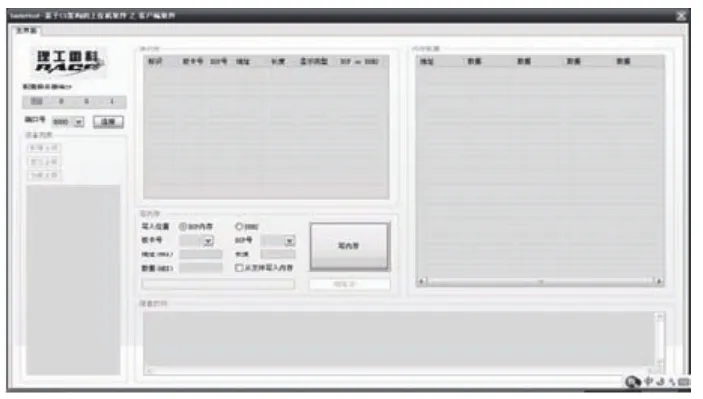

客户端界面如图13所示。

图12 服务器端界面

上位机软件的测试过程如下:

(1)服务器端开启服务,查看开启日志判断是否开启成功;(2)客户端与服务器端通过IP地址建立连接;(3)客户端扫描系统中的板卡个数、每个板卡的DSP个数,建立设备列表。

通过设备列表对DSP程序进行加载、服务、读写DSP内存等操作,可见通过PCIE网络,CPU板可以实现多信号处理板卡之间的数据传输。

5 结束语

本信号处理系统平台完成高速信号进行实时处理,采用Rapid IO以及PCIE等高速数据传输,使得板卡间的数据得以大量传输,系统设计需要具备灵活性、可拓展性、易实施性、体积小、质量轻、低功耗等特点[8]。本系统平台已经在某项目的信号处理系统中得到了很好的应用。

图13 客户端界面

[1] 翟彦彬,蒋志焱,张保宁. 大规模Rapid IO协议交换的FPGA实现[J]. 现代雷达,2011, l2(12).

[2] 郑东卫,陈矛,罗丁利. VPX总线的技术规范及应用[J]. 火控雷达技术,2009, l2(4).

[3] 蒋迺倜,张玉喜,任延平,潘瑞云. 基于VPX标准的主动雷达信号处理系统设计[J]. 雷达与对抗,2012, 6(2).

[4] 李宾,马晓川,鄢社锋,杨力. 基于VPX标准的Rapid IO交换和Flash存储模块设计[J]. 声学技术,2011, 12(6).

[5] 池凌鸿,史鸿声. OpenVPX总线及其在雷达信息处理的应用[J]. 雷达科学与技术,2013, 8(4).

[6] 吴静,王洪,汪学刚. 基于VPX6-460的多处理器通信设计[J]. 电子技术应用,2013, 39(11).

[7] 王学宝. 基于VPX标准的PMC/XMC载板设计[J]. 计算机测量与控制,2010, 18(8).

[8] 李宏,史鸿声. 基于VPX的3U信号处理平台的设计[J]. 中国科技信息,2012, 12(12).

A Design of 6U Signal Processing System Base on VPX

GOU Huanmin, XUE Pei, YANG Fang

(China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China)

VPX bus with high bandwidth, good real-time performance, fl exible topology structure, strong generality, and hush environment resistance is introduced. It is becoming the development direction of a new generation of the military comprehensive signal processing system. A design of 6U signal processing system base on VPX, provide high bandwidth, support serial Rapid IO and PCIE. It makes high speed data exchanging impossible.

signal process; VPX; serial Rapid IO; PCIE

TN402

A

1681-1070(2014)11-0021-05

苟欢敏(1985—),女,陕西西安人,硕士,2010年毕业于南京航空航天大学,现就职于中国电子科技集团公司第58研究所,主要从事模块电路的设计研究。

2014-07-07