MCU芯片Multi-Sites测试中几个值得关注的问题

2014-02-26张凯虹

陈 真,陆 锋,张凯虹

(1. 江南大学物联网工程学院,江苏 无锡 214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

伴随着计算机技术、通讯技术和微电子与固体电子技术等的交叉发展,微控制单元(Micro Control Unit,MCU)也得到了飞速发展。MCU芯片具有面积小、功耗低、低成本、高性能等特点,现阶段已经广泛地应用于工业自动化、仪器仪表、信息通信、军事装备等各领域。

随着应用需求的不断提升,MCU芯片的电路性能和复杂性增加,频率越来越高,芯片测试成本上升,而测试成本的主要来源是测试时间;若想在半导体集成电路测试行业立于不败之地,就要保证在测试结果的一致性前提下压缩芯片的测试时间,以降低测试成本。Multi-Sites测试是最佳解决方案之一。但在Multi-Sites测试中,保证各项性能参数精确、可靠成为MCU芯片测试的一大挑战。

2 MCU芯片Multi-Sites测试方法

MCU芯片的主要测试参数包括:直流参数测试、交流参数测试和功能测试。直流参数测试主要包括开路/短路(Open/Short)测试、输出高/低电平(VOH/VOL)测试、输入高/低电流(IIH/IIL)测试、输入漏电流测试、输出短路电路IOS测试、输出高阻电流(IOZH/IOZL)测试和电源电流测试等;功能测试用于验证芯片是否能完成设计所预期的工作或功能。Multi-Sites测试的实现方法有两种:一种是软件方式,另一种是硬件方式。

2.1 软件方式

用软件方式实现MCU芯片Multi-Sites测试具体方法大体如下:测试直流参数和交流参数采用串行测试,与单Site测试的效率相同;功能测试时,把多个芯片当作一个芯片来测试,测试结束后,根据Fail的数据(不良的TEST CHANEL等)来判断哪些芯片不良。所以,用软件方式实现MCU芯片Multi-Sites测试,有以下方面的不足:

(1)测试效率比单Site测试有所提高,但是其直流参数和交流参数的测试效率与单Site测试相同;

(2)有些功能测试不能实现Multi-Sites测试,比如,测试PATTERN中有MATCH PATTERN的就不能实现Multi-Sites测试;

(3)在功能测试时,若Fail的长度超过测试机的FAIL MEMORY深度时,也不能实现Multi-Sites测试;

(4)对工程测试员而言,编写测试程序难度较大,出错的概率非常高。

由于以上原因,许多用软件方式实现Multi-Sites测试的测试机,在实际使用时往往只做单Site测试。真正能实现Multi-Sites测试的测试机是在硬件上下功夫。

2.2 硬件方式

能实现Multi-Sites测试的测试机都采取模块化设计,每个Site必须具备独立的SEQ和控制进程,能做到同时开始,但不一定同时结束。以台湾德律科技公司所生产的TR-6836集成电路测试机[1]为例,它采用模块化设计,以FPGA组件为设计主轴,将SEQ与Timing Generator、Format分别设计在不同FPGA中,以一个SEQ控制8个PIN Waveform Format FPGA,最高测试频率达到33 MHz,Per-pin lever set,16组Timing Set,Per-pin Timing Generator,4组Driver/Compare marker,Pattern Memory 4~8 MB。以分布式控制系统理念,开发可独立的Pin Electric Board(PEB),每8 Pin可供应一个Site使用,系统可同时并行测试8 Sites。

3 测试中几个值得关注的问题

3.1 直流参数测试

MCU芯片直流参数包括开路/短路(Open/Short)测试、输出高/低电平(VOH/VOL)测试、输入高/低电流(IIH/IIL)测试、输入漏电流测试、输出短路电路IOS测试、输出高阻电流(IOZH/IOZL)测试和电源电流测试等。在进行直流测试之前,应该保证进行预处理的向量正确无误,还要选择合适的精确测量单元(PMU)或电源提供单元(DPS)。

3.2 功能测试

功能测试用于验证MCU是否完成设计所预期的工作和功能。基本测试过程是应用有序或随机的数据组合测试图形,以MCU规定的速率作用于DUT,并比较MCU的输出与预期数据图形,观察两者是否相同,以此判定MCU功能是否正常。当执行功能测试时,需要考虑到DUT性能,还要检查环境温度、DUT电源电压最大值/最小值、输出电平、输出负载电流、输出参考电流、测试频率/周期、时钟/建立时间/保持时间/控制信号、输出波形格式、输出时序时间、向量序列等。

有些向量对外部条件的影响非常敏感,有时在某种特定条件下测试结果发生变化。比如,对某个功能反复测试一百次,其中有一次没过,当这种情况发生时,测试工程师需要对原因进行分析。这时就要根据芯片的相关资料进行分析与试验:比如尝试在上电时预置某些管脚的状态,然后再进行测试;尝试停在向量不同的位置去测量,即改变测试时的芯片状态;把时钟频率下降一半进行测试;在测量之前断开所有与被测管脚连接的相关资源,只连接“PMU”进行测试等;可以考虑修改采样点等。

3.3 测试方法的实现

3.3.1 信号干扰

测试频率过高会带来一系列的问题,例如信号的串扰、衍射、畸变等[2]。不论什么样的测试板都会产生一定的噪声,我们所能做的只能尽量合理地布局布线以少产生噪声。

在混合信号测试中,设计PCB时要将模拟电路和数字电路分开布局,以减小数字芯片的噪声对模拟电路的影响;应尽量增大电源线和地线的宽度,或采用电源平面与地平面;在芯片电源和地之间接入滤波、去耦电容,注意电容的引线不能过长;对关键信号要采用屏蔽线,以避免其他信号的干扰;为减小信号线上的分布电阻、电容和电感,应尽量缩短导线长度和增大导线之间的距离;模拟电路的接地层,也要和数字电路的接地层分开,最后通过电感连接起来。这样测试出来的效果才会比较好。

3.3.2 探针接触电阻

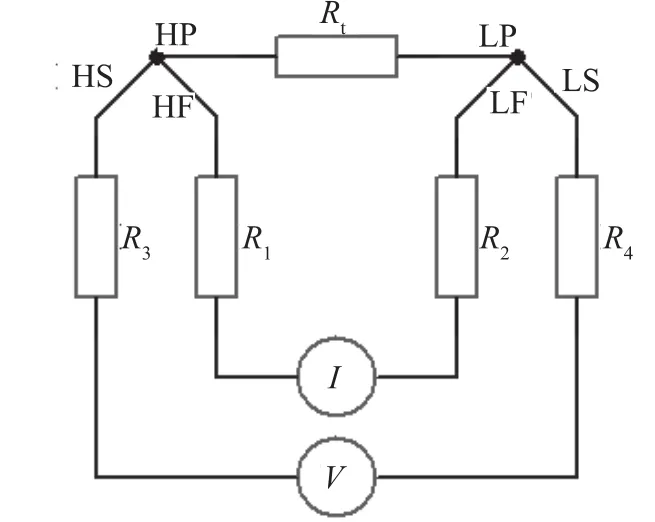

由于在实际生产测试中,探针会不断地被氧化、污染和老化,或针的材料与形状、压点的材料、触点的压力,以及探针的磨损和污染状况等都会导致探针的接触电阻在很大程度上变化。这对于驱动电路参数测试会造成测试误差,因为该测试项要求所有输出端口的探针接触电阻有较高的一致性。为了测量探针和Wafer直接的很小的接触电阻,以减小接触电阻或者消除接触电阻的影响,将所期望的信号准确施加到被测芯片的各个压点上,可采用开尔文连接方式[3](或称四线测试方式)来进行测试,如图1所示。

图1 开尔文四线测试方法

开尔文连接有两个要求:(1)对于每个测试点都有一条激励线F和一条检测线S,二者严格分开,各自构成独立回路;(2)要求S线必须接到一个有极高输入阻抗的测试回路上,使流过检测线S的电流极小,近似为零。图1中R表示引线电阻、探针与测试点的接触电阻之和。由于流过测试回路的电流为零,在R3、R4上的压降也为零,而激励电流I在R1、R2上的压降不影响I在被测电阻上的压降,所以电压表可以准确测出Rt两端的电压值,从而准确测量出Rt的阻值。测试结果和R无关,有效地减小了测量误差。按照作用和电位的高低,这四条线分别被称为高电位施加线(HF)、低电位施加线(LF)、高电位检测线(HS)和低电位检测线(LS)。

具体实施时,只要在原来的基础上多加一根探针与接收线相连接作为测量用,让电流从另外一根与施加线相连接的探针上流过,用施加端施加电压与接收端测试出来的电压值之差除以通过与施加线相连接的探针的电流值,就近似得到了该探针的接触阻抗大小,并且利用该方法可以在压点上获得准确的期望施加电压,保证测试的准确性。

3.4 Multi-Sites测试一致性

在Multi-Sites测试中,验证所测MCU的一致性,可用不同的Site对同一颗芯片进行测试,要求测试结果的差异控制在l%以内。另外,在调试中如果其中某一个Site测试有问题,可以考虑换一个Site来测试这颗芯片,对比测试结果进行判断,或者通过几个Site互换外围芯片或外围DUT来判断是否是外围芯片发生老化、接口出现脱落或虚焊,或者MCU芯片功能是否达到设计要求还是由于噪声干扰引起等。

4 结束语

现在芯片测试受到利润影响,对测试效率和测试成本提出了更高的要求,合理采用测试设备和仪器,参考电路设计中提供的可测性设计,设计科学的测试方法,Multi-Sites并行测试是节约成本、提高效率的新途径。通过大量测试验证,解决测试中存在的各种问题,逐步探索形成了一套适用于生产环境的可靠而有效的Multi-Sites并行测试技术,并在多个实际的MCU测试项目中应用,可推广应用到MCU产品的芯片测试。

[1] TRI. TR6836 User Guide[M]. IC Tester FAE, Test Research Inc.

[2] 张凯虹,陆锋,等. DDS自动测试技术研究[J]. 半导体学,2009(3):262-265.

[3] 赵英伟,庞克俭. Kelvin四线连接电阻测试技术及应用[J]. 半导体技术,2005,30(10).