基于FPGA的SPI接口Flash控制器设计及在存储配置数据中的应用

2014-02-05赵庆平姜恩华

赵庆平,姜恩华

(淮北师范大学 物理与电子信息学院,安徽 淮北 235000)

基于FPGA的SPI接口Flash控制器设计及在存储配置数据中的应用

赵庆平,姜恩华

(淮北师范大学 物理与电子信息学院,安徽 淮北 235000)

介绍了SPI工作原理,给出了一种基于FPGA的SPI控制器的设计方法。利用FPGA丰富的逻辑资源以及产生精确时序的能力,非常方便地对SPI flash进行读写、擦除等操作,从而能快速、准确地存储数据。阐述SPI控制器的设计过程,使用Modelsim进行仿真验证,并用VHDL硬件描述语言进行编程,下载到FPGA开发板上进行测试验证,对SPI接口Flash进行操作。证明了系统设计方法的正确性和可靠性。该方法对FLASH存储控制系统的设计具有普遍适用性,可用于对FPGA配置进行保存。

SPI控制器;FPGA;VHDL设计;Modelsim仿真

1 系统总体方案设计

使用德致伦公司出品的开发板Genesys,该开发板使用的FPGA芯片是xilinx公司的Virtex-5,Virtex-5系列采用第二代高级芯片组合模块(ASMBLTM)列式架构,采用业界一流的65 nm铜工艺技术,支持多达330 000个逻辑单元,6个时钟管理模块,多达1 200个用户接口,提供从1.2 V到3.3 V的广泛的I/O标准范围,高达16.4 Mb的集成模块存储器,与Select IO技术配合使用,简化源同步接口[4]。

Flash芯片采用ST Microelectronics公司的M25P16。该芯片是16 Mbit(2 M×8)串行flash存储器,兼容高速SPI接口。M25P16包含32个扇区,每个扇区有256页,每一页有256个字节。该芯片由2.7 V~3.6 V单电源供电,最大50 MHz工作时钟,100 000次的擦除和重写,可以保持20年时间[5]。

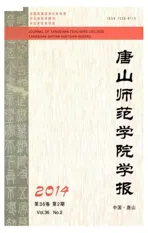

本系统的系统框图如图1所示。

图1 系统总体方案设计

图1中,FPGA作为电路核心,连接上位机和SPI Flash存储器。一方面接收来自上位机PC串口的数据,并将数据存储到Flash中。另一方面,从Flash中读出数据并通过串口发送到上位机。

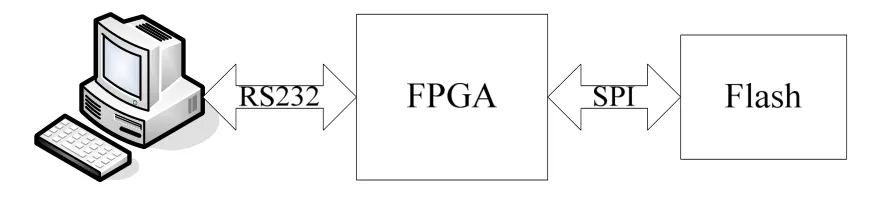

在FPGA芯片中需要构建三个模块,分别是UART控制器,FIFO模块以及SPI控制器。如图2所示。

图2 FPGA内部模块设计

上位机和FPGA之间是通过RS232进行通信的。RS232是PC机通信常用的接口,遵循异步传输标准。RS232采用UART协议,需要在FPGA内构建UART模块,实现数据在上位机和FPGA之间的传输。在FPGA中构建SPI控制器,为flash提供时钟,并对其进行擦除和读写操作。UART和SPI模块的时钟不同,因此需要添加FIFO作为两者之间数据缓冲。因为接收的串口数据被串并转换为8 bits,与之相连的FIFO(即先进先出队列)位宽定为8 bits,深度设为256个单元。

2 SPI接口工作原理

SPI接口可以分为主机(Master)以及从机(Slave)两个部分,其结构框图如图3所示。

图3 SPI接口

主机以及从机之间是通过4根信号线进行连接的,它们分别是CS、SCK、MOSI和MISO。对它们的定义如下:

CS:从机片选信号,由主机控制输出;

SCK:同步时钟信号线,用来对主机和从机的数据传输进行同步,由主机发出控制输出,从机则在SCK的上升沿和下降沿接收以及发送数据;

MOSI:主机作为输出、从机作为输入信号,主机在下降沿(或上升沿)由此信号线发数据给从机,而从机在上升沿(或下降沿)由此信号线接收发来的数据;

MISO:主机输入、从机输出信号,从机在上升沿(或下降沿)通过该信号线发送数据给主机,主机在下降沿(或上升沿)通过该信号线接收该数据[6]。

其工作原理为:当无数据需要传输在主机和从机之间时,主机通过控制SCK输出低电平,CS则输出高电平,SPI总线就会处于空闲的状态;如果有数据需要进行传输时,主机通过控制CS输出为高电平,SCK则输出时钟信号,SPI总线就会处在工作状态;在某个时钟边沿,从机或主机并行发送数据,将数据各自传输到MOSI以及MISO上;而在下一个时钟沿,从机以及主机同时接收数据,各自将MISO以及MOSI上的数据接收并进行存储;而当数据所有全部传输完成后,主机就会控制SCK输出为空闲的电平,CS则输出为无效的电平,而SPI总线就会又回到空闲的状态。到此,一个完整的SPI数据总线传输过程完成[7]。

3 SPI控制器

SPI控制器的设计采用的是verilog HDL硬件语言。Verilog HDL是目前使用非常广泛的硬件描述语言之一。Verilog描述的器件在编译和综合时适应能力强,系统可以自动优化。虽然对应语言的解读性能较弱。但是仿真以后的纠错能力强[8]。

本文设计的SPI控制器主要完成以下两个主要任务:

写flash:将上位机发送来的256字节数据写入flash的某一页中;

读flash:从flash写有数据的一页中读出并传送到上位机显示。

将FPGA配置数据存储在Flash芯片内,重新上电,读取Flash中数据对FPGA重新配置。

写flash操作首先要对flash进行擦除操作,输入擦除指令并等待3 s,然后进行写操作。写操作要输入8位WREN指令、8位PP指令、24位地址,随后输入数据。流程图如图4所示。

图4 写操作

开始时处于检测输入状态idle,当有数据从上位机发送过来,立即进入SPI工作模式;wren指令将写寄存器的写使能位WEL置1,输入擦除指令se和要擦除的页的地址,需要等待3 s,这时写使能位WEL复位为0,重新输入wren指令将WEL位置1;输入页写指令、页写地址和页写数据;完成以后回到检测状态。

读操作相对简单些,输入读指令、读地址之后,数据即从flash中输出。状态如图5所示。

图5 读操作

开始处于检测读使能状态,当允许读,发送读指令和读地址,数据就从flash中输入到FPGA芯片内。经过FIFO传送到上位机进行显示。

4 仿真与调试

本设计采用ISE + modelsim的方法进行联合设计。ISE是赛灵思公司推出的EDA设计软件。它集成HDL代码编辑、原理图编辑,代码编译、综合,工程仿真以及锁定管脚和下载程序的功能。ISE提供了设计开发工具的所有功能,支持Xilinx的全系列逻辑器件产品,并集成了XST综合工具,支持核生成工具和PACE[9]。明导国际公司的Modelsim是目前业界非常优秀的HDL硬件语言仿真软件,它可以提供很好的仿真环境,是目前业界内唯一的实现单内核支持VHDL以及Verilog HDL混合仿真的仿真软件[10]。

写操作的仿真图如图6所示。

图6 写操作仿真图

由图6可以看出,当上位机有数据发送到FPGA的时候,接收放在FIFO中。FIFO存储满之后,FPGA使能SPI控制器开始工作。在scl信号的下降沿准备指令、地址,并从FIFO中读出数据,逐位在scl上升沿输入到flash中。

读操作的仿真图如图7所示。

图7 读操作仿真图

由图7可以看出,当要读取flash中的数据,使能读信号start_read,然后SPI控制器进入读数据状态。在scl的下降沿flash输出数据,在scl上升沿采集到FPGA芯片中,缓存在FIFO中。FIFO写满之后,由串口回传给PC机,进行核对。

由仿真图可以看出,满足了时钟和数据的建立和保持时间,可以避免毛刺的产生。在仿真通过后,将工程下载到开发板上进行运行测试。本文所使用的开发板是德致伦公司设计出品的Xilinx FPGA开发板。下载测试,上位机发送到FPGA写入flash芯片的256字节数据,再用FPGA读出flash中刚刚存储的数据并返回到上位机。如图8所示,完全相同,说明SPI flash读写测试成功。

图8 读取SPIFlash数据

最后,将FPGA编译产生的数据下载到该SPI Flash芯片中,重新上电,系统自动加载硬件数据,实现了FPGA配置数据的掉电不丢失功能。

5 结论

介绍了基于FPGA的SPI控制器的设计方法,使用Digilent公司的FPGA开发板Genesys进行了验证。完成了SPI Flash控制器的逻辑仿真,对SPI Flash的读写进行了验证,并且利用此Flash实现了对FPGA的重新上电的自动配置功能。

本设计在FPGA芯片上实现,具有较高的可移植性,控制器经过简单修改就可以用于控制其它型号的SPI flash芯片,因此具有广泛的适用性。

[1] 李冬梅,王延杰,王长宇,等.基于FPGA的高速实时图像采集和自适应阈值算法[J].吉林大学学报(工学版),2010, 40(2):534-537.

[2] 罗莉,夏军,邓宇.通用SPI Flash控制器的设计与验证[J].计算机工程,2011,37(8):22-27.

[3] 郑川.Step by Step现场可编程门阵列设计入门与进阶[M].西安:西安电子科技大学出版社,2008.

[4] 佟吉刚,张振新.基于FPGA的无线传感器网络节点设计[J].传感技术学报,2009,22(3):417-421.

[5] 关珊珊,周洁敏.基于Xilinx FPGA的SPI Flash控制器的设计与验证[J].电子器件,2012,35(2):216-220.

[6] 赵新雨,许忠仁,付贵增,朱文伟.基于FPGA与单片机的SPI接口的实现[J].工业仪表与自动化装置,2010(2):32-33.

[7] 王松.基于FPGA的串行外围接口SPI设计与实现[J].微计算机信息,2010,26(11-2):117-119.

[8] 王军海.基于Verilog HDL的DDS设计[D].武汉:武汉理工大学,2007.

[9] 孙航.Xilinx可编程逻辑器件的高级应用与设计技巧[M].北京:电子工业出版社,2004.

[10] 范静,陈文艺.基于Modelsim与Matlab/Simulink联合仿真技术的接口与应用研究[J].西安邮电学院报,2010, 15(3):72-75.

(责任编辑、校对:田敬军)

Design of SPI Interface Flash Controller Based on FPGA and the Application in Storing Configuration Data

ZHAO Qing-ping, JIANG En-hua

(School of Physics and Electronic Information, Huaibei Normal University, Huaibei 235000, China)

It introduces the operating principles of SPI (serial peripheral interface) and gives a designed method by using SPI controller based on FPGA (Field Programmable Gate Array). We can expediently read-write and wipe SPI flash to quickly and accurately storage data with rich logical resources and accurate time series making by FPGA. It also expounds the designing process of SPI controller, which utilizes the simulation and verification by Modelsim and uses VHDL hardware description language controller to program, and then download the program to FPGA development board to test and verify and finally operates the SPI interface flash. It is proved that the method is correct and reliable, and has general applicability to the system designing of the FLASH controller and can be used to save the FPGA configuration.

SPI controller; FPGA; VHDL design; Modelsim simulation

TP332.3

A

1009-9115(2014)02-0069-04

10.3969/j.issn.1009-9115.2014.02.020

国家自然科学基金(41275027),安徽高校省级自然科学研究项目(KJ2013Z228),安徽高校省级自然科学研究重大项目(KJ2012ZD06)

2013-11-2

赵庆平(1972-),男,辽宁阜新人,硕士,讲师,研究方向为FPGA及嵌入式系统设计。数据的掉电不丢失。

FPGA(Field Programmable Gat Array,现场可编程门阵列)是在PAL、GAL、EPLD以及CPLD等可编程逻辑器件的基础上发展出来的产物。由于FPGA芯片需要被反复烧写,只能采用一种易于反复配置的结构。目前主流FPGA都采用了基于SRAM工艺的查找表结构。由于FPGA采用SRAM工艺,芯片无非易失性,所依掉电后丢失其内部的逻辑配置[1]。

串行外设接口(Serial Peripheral Interface, SPI)是一种高速度、全双工、同步串行通信接口,主要用于微处理器、微控制器和外围扩展芯片之间的连接[2]。利用SPI Flash大容量、读写速度快、成本低廉以及数据在断电后不丢失的特点,可以将FPGA的配置数据存储于SPI Flash中[3]。

文中采用赛灵思公司的Virtex-5和意法半导体公司的M25P16进行设计。对SPI控制器进行仿真,符合SPI时序要求。与PC机进行通信测试,写入和读出的数据吻合。将FPGA配置数据存储在M25P16中,实现了FPGA配置