600 V VDMOS器件的反向恢复热失效机理

2013-12-26夏晓娟吴逸凡成建兵郭宇锋孙伟锋

夏晓娟 吴逸凡 祝 靖 成建兵 郭宇锋 孙伟锋

(1南京邮电大学电子科学与工程学院,南京 210003)

(2南京邮电大学江苏省射频集成与微组装工程实验室,南京 210003)

(3东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

随着半导体技术的快速发展,功率器件因其输入阻抗高、开关速度快等特性被广泛应用于开关电源及电机驱动等领域[1-6].桥式电路是开关电源的一种重要形式,其主要功耗来源是功率管的开关损耗及与之并联使用的二极管的反向恢复损耗.为了减小二极管的损耗,需降低二极管反向恢复电荷,在高频应用中,可采用并联碳化硅二极管(SiC diode),但是成本较高.在低频应用中,二极管反向恢复的损耗较低,因此一般都直接采用功率开关管寄生的体二极管.

近年来,功率器件体二极管的反向恢复一直是研究热点[7].相关研究表明反向抽取的少数载流子电流是影响器件可靠性的关键因素.文献[8-9]提出了二极管反向恢复过程中的动态雪崩概念,动态雪崩导致电流汇聚而在薄弱点损坏功率器件.文献[10]研究了功率器件终端的电流汇聚和碰撞电离现象,并提出了新型终端结构以提高器件关断过程中的可靠性.以上文献所提及的失效均为雪崩击穿失效,发生在电压较高的工作条件下,而目前尚未有对非雪崩击穿失效的机理研究.

本文详细研究了600 V VDMOS器件体二极管的工作过程,研究发现,当体二极管正向导通时,除原胞区域外,器件的终端区域也会积累大量的少数载流子,此部分少数载流子在体二极管反向恢复过程中,以单股电流的形式从靠近终端位置的原胞流出,这会导致该处p-body区的温度升高,进而造成寄生三极管导通及器件失效.Sentaurus TCAD模拟仿真和实际测试结果均验证了该结论.

1 器件结构

高压VDMOS器件在桥式电路系统中具有广泛应用.图1为典型的半桥电路结构,当功率管Q1导通、Q2关断或Q1关断、Q2导通时,电源通过变压器把能量传递给负载电容,电感L处于充电状态,输出电流增加.当Q1和Q2关断后,二极管D1和D2导通,变压器线圈上的能量通过D1和D2以电流的形式进行泄放,电感L处于放电状态.该电路的功耗主要来源于功率管Q1,Q2的开关损耗和二极管D1,D2的反向恢复损耗.其中,本文中功率管Q1, Q2为功率VDMOS器件,二极管D1,D2为VDMOS器件的体二极管.

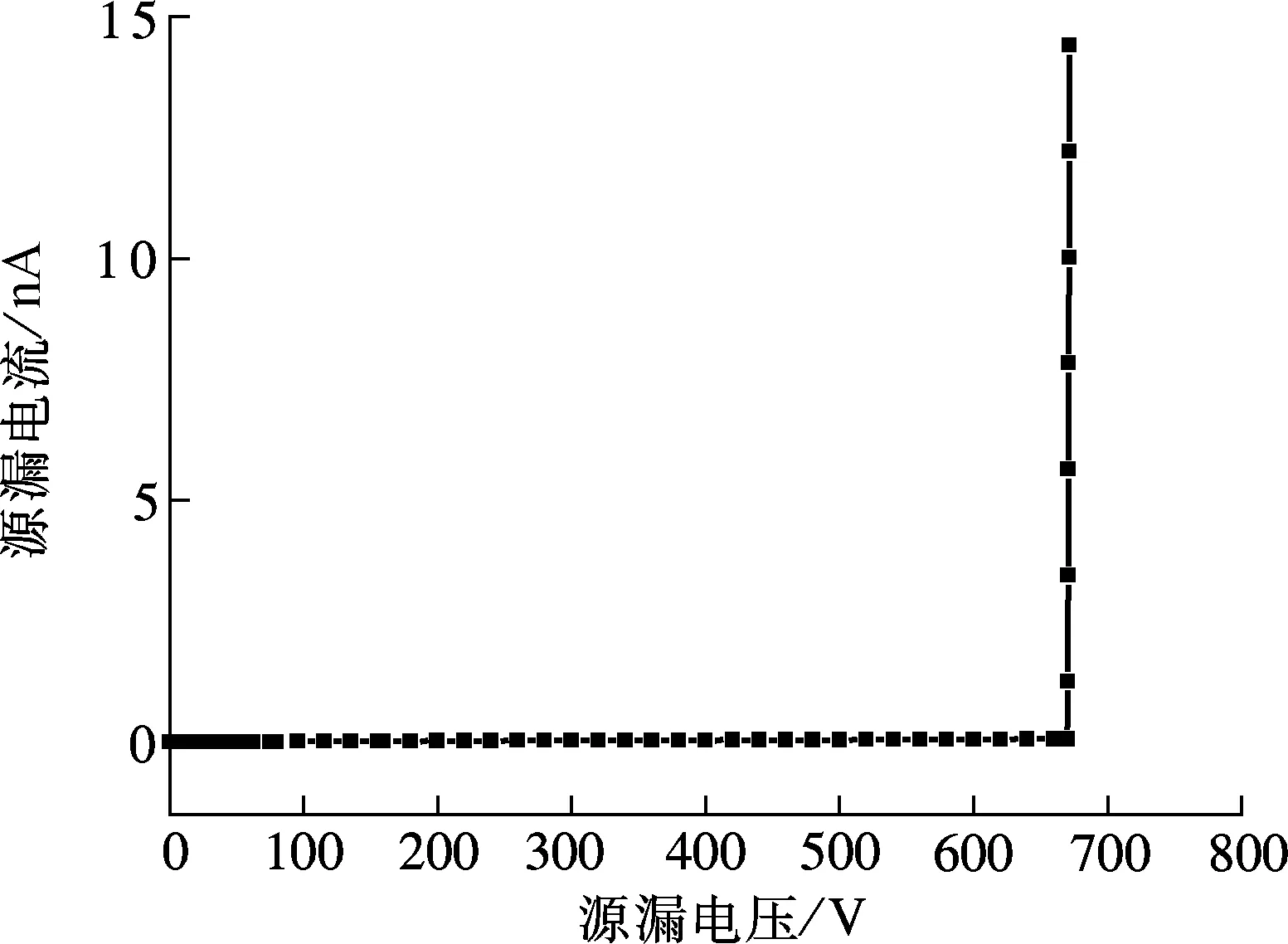

本文所研究的VDMOS器件原胞和终端结构如图2所示.该器件外延层厚度为52 μm,掺杂浓度为7.5×1013cm-2,其原胞区采用了结深为3.6 μm的p-body,注入剂量为5.5×1013cm-2.其终端区通过6个场限环的结构进行水平方向的耐压,每个场限环的结深为4.2 μm,注入剂量为3.0×1014cm-2.本文所研究的600 V VDMOS器件的电流为4 A.芯片采用标准TO-220封装.该器件的击穿电压为670 V,如图3所示.

图1 半桥电路系统工作示意图

图2 VDMOS器件剖面图(单位:μm)

图3 VDMOS器件的击穿电压

2 反向恢复特性

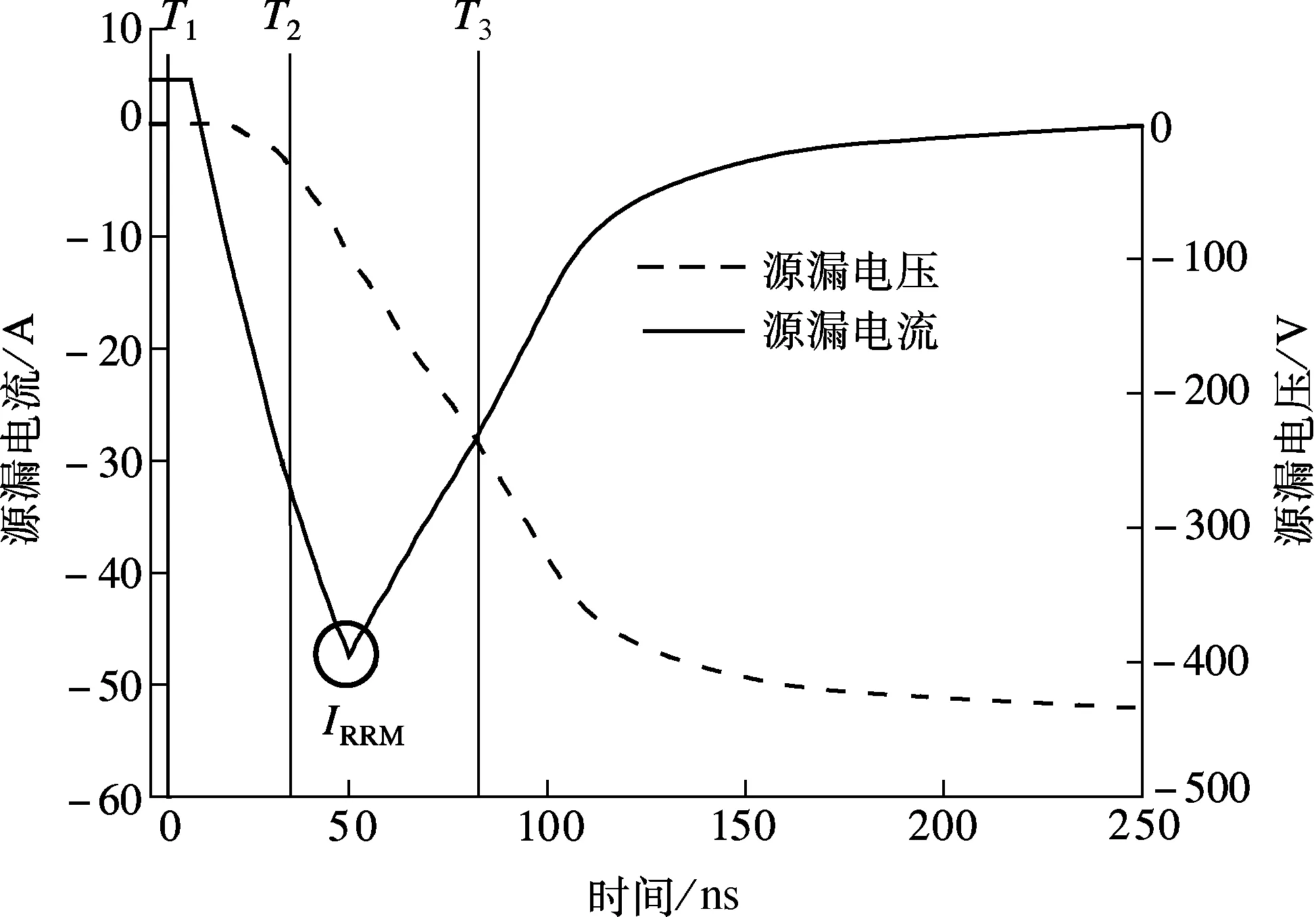

图4为VDMOS器件体二极管反向恢复过程的电流和电压曲线.反向恢复过程主要分为3个阶段:正向导通阶段、体二极管中少数载流子反向抽取的初始阶段和恢复阶段.T1时刻为正向导通阶段,VDMOS器件受到外界电流应力,体二极管正向导通,电流由器件源极流向漏极,此时器件两端电压为正向导通电压,约0.7 V.T2时刻为体二极管中少数载流子反向抽取的初始阶段,由于受到外界电压应力,少数载流子被快速抽取,形成的反向抽取电流以固定的di/dt增加,并在该阶段末达到最大值IRRM.在该阶段中,外延层中的空穴与p-body中的电子形成电势差,使器件漏源电压只能缓慢增加.T3时刻为反向恢复阶段,器件两端电压迅速增加,器件同时承受高电压和大电流,形成高功率区域,导致该区域温度升高,该阶段为器件失效的主要阶段.

图4 VDMOS器件寄生体二极管反向恢复过程的电流和电压曲线

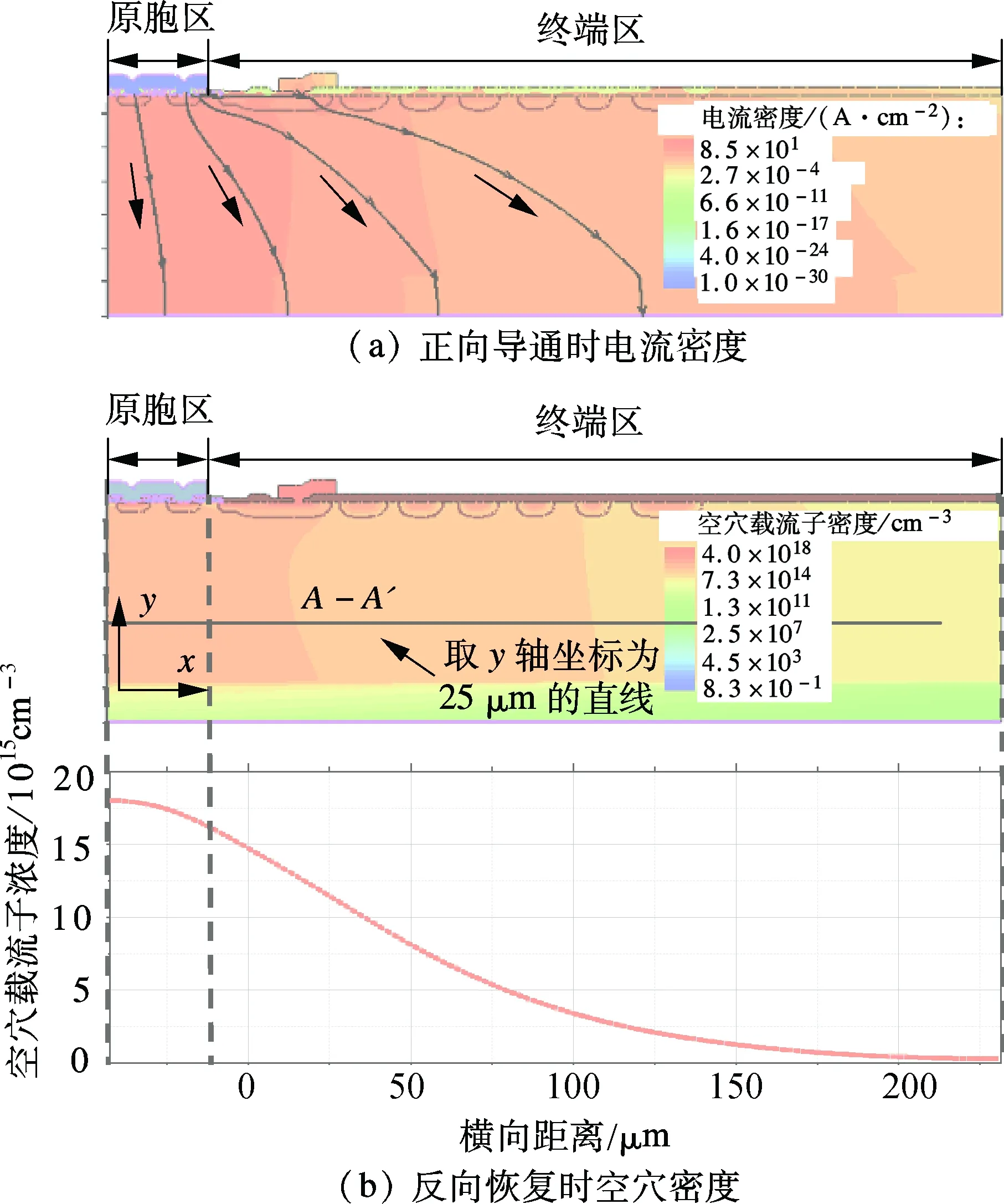

图5为VDMOS器件寄生体二极管正向导通时(图4中的T1时刻)的电流与少数载流子(空穴)的分布情况.此时,器件体二极管处于正向导通状态,空穴载流子由p-body注入到外延层中.电流以源极金属为起点,通过p-body流向漏极,载流子会沿着不同的电流路径运动,如图5(a)中A,B,C,D四个方向,在每个方向上都会有少数载流子注入,使得原本在器件中只起耐压作用的终端区域,也不可避免地贮存了大量的少数载流子.每条路径上少数载流子的分布近似为

(1)

式中,τHL为大注入载流子寿命;La为双极性扩散长度;q为电子电荷电量;d为沿电流路径从p-body到漏极的路径长度;JT为载流子密度.

由图5(b)可知,空穴的浓度由原胞区向终端区逐渐降低,沿图中A-A′线进行分析,可看出原胞区下方的空穴载流子浓度达到1.8×1016cm-3,随着横向距离的增大,空穴的浓度降低,最终稳定在2.7×1014cm-3左右.

图6为体二极管反向恢复阶段时(图4中T3刻)的电流与空穴载流子的分布情况.器件进入体二极管反向恢复后,原本贮存在N型外延层中的空穴载流子被反向抽取,经过p-body区域到达源极金属.终端区贮存的大量载流子将通过最靠近终端区的原胞进行泄放.如图6所示,VDMOS器件在反向抽取过程中,终端区大量的空穴电流流向最外侧的原胞,形成一股大电流,流经p-body区,到达源极金属.此时器件漏源两端的电压达到230 V,该区域就成为高功率区,其功率密度可根据下式计算:

图5 VDMOS器件体二极管正向导通时的电流分布及空穴载流子分布

图6 VDMOS器件在T3时刻的空穴载流子分布、电流密度分布及电场分布

pd=JtotE

(2)

式中,Pd为功率密度,W/cm3;Jtot为该区域的总电流密度, A/cm2;E为该区域的电场强度,V/cm.

高功率区域随着时间的推移会形成焦耳热,导致温度升高,其温度变化为

(3)

式中,P为功率;K和α分别为热传导系数和热扩散系数,其值为1.3 W/(cm·K)和0.8 cm2/s.

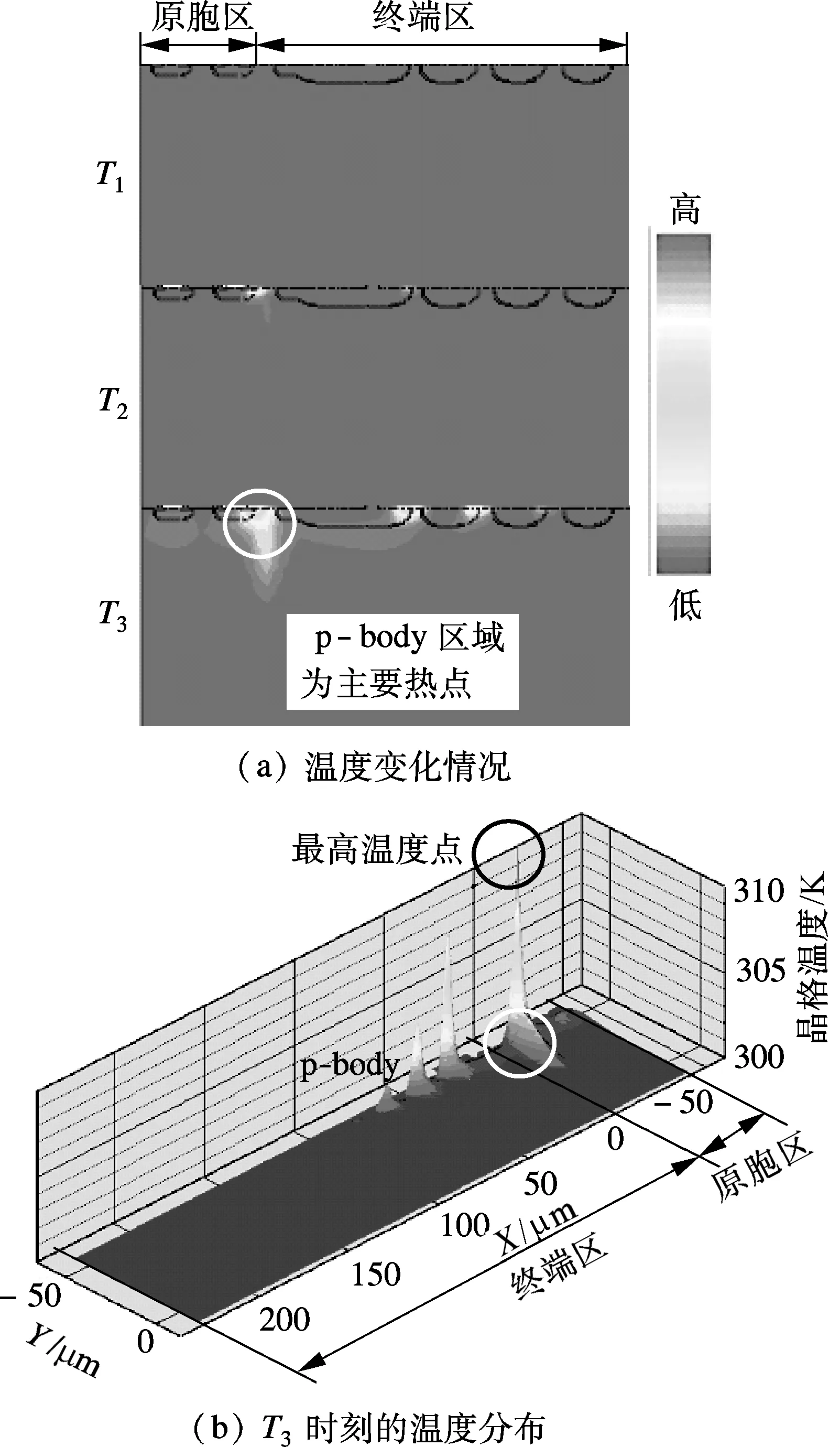

图7为VDMOS器件在反向恢复过程中的温度变化情况.可看出,VDMOS器件的高温部分主要集中在原胞p-body区域.T1时刻为VDMOS器件寄生体二极管正向导通的情况,此时,器件只有4 A的正向电流和约0.7 V的正向导通电压,器件功率很低,不会产生热量,因此温度维持不变.T2时刻为VDMOS器件寄生体二极管中少数载流子反向抽取的初始阶段,器件的反向抽取电流达到30 A,而此时漏源两端耐压仅40 V,器件功率较低,只会产生较少热量,温度开始缓慢升高.T3时刻为VDMOS器件寄生体二极管的恢复阶段,器件的电流和耐压均较高,功率很高,产生较高热量,温度开始明显增加.图7(b)为在T3时刻的三维温度分布图,由图可知,VDMOS器件在p-body区域的温度远高于器件其他部分的温度.

图7 VDMOS器件体二极管反向恢复过程温度变化情况

随着温度的升高,器件寄生三极管基区的电阻增大,内建电势降低,同时伴随着较大位移电流和反向恢复电流,触发寄生三极管的开启,电流发生倍增效应,从而导致器件损坏.寄生三极管基区电阻率ρ、内建电势Vbi与温度T的关系如下:

(4)

(5)

图8 VDMOS器件失效时的电流分布

3 测试结果

图9(a)为600 V 4 A等级的VMODS器件寄生体二极管的反向恢复测试电路.当功率开关管开启时,电源对电感进行充电,电感电流增加;当功率开关管关断后,电感通过被测器件的寄生体二极管

图9 VDMOS器件体二极管反向恢复特性测试

进行续流,使被测器件寄生体二极管处于正向导通状态.当功率开关管再次开启时,电源电压加在被测器件的两端,使被测器件进入反向恢复过程,即本文研究的过程.图9(b)为VDMOS器件发生失效时的电流、电压测试波形,由图可知,器件反向恢复电流的峰值为12 A,当反向恢复电流为5.8 A时,器件失效,发生失效的时刻与图4中的T3时刻相似.这是由于器件的p-body区在高电场和高电流密度下,产生焦耳热,温度升高,使得器件寄生三极管基区电阻增加,内建电势降低,触发寄生三极管开启,进而导致VDMOS器件失效.

图10为VDMOS器件失效的显微照片.可看出器件的失效位置为最靠近终端区域的原胞位置.对比图10和图8,可证实理论分析与实际测试一致,即VDMOS器件在体二极管反向恢复过程中,由于器件寄生三极管开启,使得电流集中汇聚到最外侧的原胞区,并在该处产生大量的焦耳热,最终使器件的最外侧原胞成为薄弱点.

图10 VDMOS器件失效的显微照片

4 结语

本文借助Sentaurus TCAD仿真软件研究了600 V VDMOS器件寄生体二极管的工作过程. 模拟和实验结果表明,在VDMOS器件的寄生体二极管正向导通时,由于电流的流动,终端区会贮存大量的少数载流子,在反向恢复时,贮存的少数载流子会以单股电流的形式被抽取,这股大电流流经p-body区到达源极金属,导致VDMOS器件最靠近终端位置原胞的p-body区域温度升高,触发寄生三极管开启,造成VDMOS器件失效.

)

[1] Baliga B J.Fundamentalsofpowersemiconductordevices[M]. New York: Springer, 2008: 3-5.

[2] Choi W, Young S. Effectiveness of fast recovery MOSFETs to reliability of switching power supplies[C]//InternationalSymposiumonPowerElectronicsElectricalDrivesAutomationandMotion. Pisa, Italia, 2010: 1113-1118.

[3] Srikanth S, Karmalkar S. Charge sheet superjunction (CSSJ): a new superjunction concept [C]//InternationalWorkshoponPhysicsofSemiconductorDevices. Mumbai, India, 2007: 795-798.

[4] Srikanth S, Karmalkar S. On the charge sheet superjunction (CSSJ) MOSFET [J].IEEETransactionsonElectronDevices, 2008,50(11): 3562-3568.

[5] Hirler F, Kapels H. YFET-trench superjunction process Window extended [C]//InternationalSymposiumonPowerSemiconductorDevicesandICs. Barcelona, Spain, 2009: 299-302.

[6] Qian Qinsong, Sun Weifeng, Zhu Jing, et al. A novel charge-imbalance termination for trench superjunction VDMOS [J].IEEEElectronDeviceLetters, 2010,31(12): 1434-1436.

[7] Zhu Jing, Zhang Long, Sun Weifeng, et al. Analysis of the electrical characteristics of 600 V-class electron irradiated fast recovery superjunction VDMOS [J].Solid-StateElectronics, 2013,80: 38-44.

[8] Lutz J, Domeij M. Dynamic avalanche and reliability of high voltage diodes [J].MicroelectronicsReliability, 2003,43(4): 529-536.

[9] Lutz J, Baburske R. Dynamic avalanche in bipolar power devices [J].MicroelectronicsReliability, 2012,52(3): 475-481.

[10] Chen Z, Nakamura K, Terashima T. LPT(Ⅱ)-CSTBTTM(Ⅲ) for high voltage application with ultra robust turn-off capability utilizing novel edge termination design [C]//InternationalSymposiumonPowerSemiconductorDevicesandICs. Bruges, Belgium, 2012: 25-28.