层次化设计方法在数字频率计设计中的应用

2013-12-10刘力

刘力

【摘 要】采用Quartus II开发环境,通过对一个2位十进制数字频率计的设计,介绍了基于EDA技术的数字系统层次化设计方法。结果证明,该设计方法简单,易懂,性能可靠。

【关键词】EDA技术;层次化设计;数字频率计

1.引言

EDA技术是近几年迅速发展起来的计算机软件、硬件和微电子交叉的现代电子设计学科,是现代电子工程领域的一门新技术。它是以可编程逻辑器件(PLD)为物质基础,以计算机为工作平台,以EDA工具软件为开发环境,以硬件描述语言(HDL)作为电子系统功能描述的主要方式,以电子系统设计为应用方向的电子产品自动化设计过程。随着电子设计技术的发展,20世纪90年代EDA技术得到全新的发展。这一阶段的主要特征是采用“自顶向下”的设计理念,实现整个系统设计过程的自动化。

层次化设计就是一种自顶向下的设计方法。这种设计是设计者以系统的要求出发,自顶向下地逐步将设计内容细化,最终完成系统的硬件整体设计。其步骤为:首先设计出一个顶层原理图,然后对系统中的每一个模块采用硬件描述语言或原理图的方式对其功能进行描述。

本文以一个2位十进制频率计的设计,详细说明层次化设计方法的运用。

2.数字频率计设计系统的组成

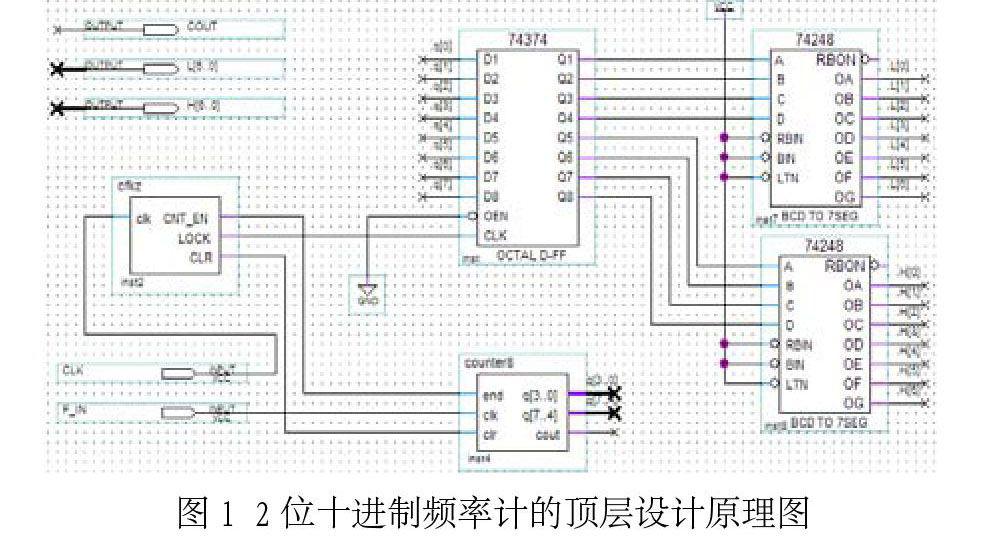

本设计中的数字频率计是一个2位十进制数字频率计,它由3个模块组成:一个测频控制模块cfkz、有时钟使能的2位十进制计数器counter8和锁存译码电路。数字频率计系统的顶层电路原理图如图1所示。

3.各模块电路的设计及仿真

3.1测频控制信号发生器的设计

最简单的频率测量方法就是在1s内对待测信号进行计数。这就要求测频信号发生器cfkz的计数使能信号CNT_EN能产生一个1s脉宽的周期信号,并对频率计的每个计数器的使能端EN进行同步控制。当CNT_EN为低电平时,停止计数,并保持其所计的数;在停止计数期间,首先需要一个锁存LOCK的上升沿将计数器在前一秒钟的计数值锁存进锁存器,由外部的七段译码器译出并稳定显示。锁存信号之后,必须有一清零信号CLR对计数器进行清零,为下一秒钟的计数做准备。高电平时,允许计数。测频控制信号发生器由图2的电路原理图来实现,计数使能信号CNT_EN是一个脉宽为1s、频率为0.5Hz的脉冲,锁存信号LOCK和清零信号CLR相继出现在停止计数以后。

将该模块的电路设计通过Quartus II软件进行输入、编译、逻辑综合和功能仿真,验证设计的正确性。

3.2 2位十进制计数器的设计

该计数器用两片可预置的双时钟十进制可逆计数器74192和两片BCD码7段显示译码器74248组成。计数脉冲是上升沿有效,十位的计数脉冲采用个位最高位取反,是为了使两位更好地保持同步。(该电路模块见图1)

3.3 锁存译码器的设计

该锁存译码器由一片8位锁存器74374及2片七段BCD译码器74248构成。其作用是使显示的数据稳定,不会由于周期性的清零信号而不断闪烁。(该电路模块见图1)

4.顶层电路的设计

使用Quartus II的原理图输入法完成各模块原理图的输入,将各模块进行编译、仿真,再生成各模块的默认电路符号。建立系统顶层原理图文件,调用各模块电路符号,完成图1的顶层电路原理图设计,并进行编译、仿真、硬件测试等。最后将设计结果下载到指定的CPLD芯片,连接硬件电路,最终完成整个系统的设计。

5.结束语

层次化设计方法在现代数字电路设计中有着明显的优势,越来越受到设计者的欢迎。对一个复杂的数字电路系统,若我们采用传统电路设计方法,工作量较大,而且也容易出错。运用自顶向下的层次化设计方法,使设计进一步细化,分模块设计,条理清晰,整个复杂的系统设计变得容易调试,缩短了设计时间,准确性和可靠性大大提高。

参考文献:

[1]廖超平. EDA技术与VHDL实用教程[M].北京:高等教育出版社,2010.6.

[2]康华光.电子技术基础(数字部分)[M].北京:高等教育出版社,2001.

[3]赵永红,等.层次化设计方法在简易钟设计中的应用[J].现代电子技术,2003.

[4]符兴昌,等.EDA技术在数字系统分析中的应用 [J].微计算机信息,2006,5-2:267-269.