基于EDA技术的通用异步收发器设计

2017-01-13张雪

张雪

【摘要】 EDA技术属于现代电子设计技术的核心内容,随着时代的发展在通信领域、电子信息领域均逐渐得到了广泛的应用。另外,信息网络技术时电子信息技术的重要组成部门,掌握信息网络技术的情况下能够获得更加完整的数据、计算机通信概念,便于更好的从事计算机通信、数据通信工作。本文在将EDA技术作为基础技术的情况下,重点分析了通用亦不收发器中多个层面的设计,希望能够更好的应用EDA技术。

【关键词】 EDA技术 通用异步收发器 数据通信

前言:在数据通信系统当中,经常采用串行通信以促使信息数据交换。异步串行通信具有比较高的可靠性,且传输线比较少,能够进行远距离的传输,当前已经能够在计算机以及外设的数据交换方面得到广泛应用。其进行数据传输时一般均需要利用通用异步收发器。与此同时,恰当的利用EDA技术优势对串行通信接口进行设计,能够便于人们更加直观的了解到数据链路层的工作原理,亦能够更加恰当的将其应用到实际当中。

一、EDA技术与通用异步收发器概述

EDA技术即是指电子设计自动化技术,属于将计算机技术恰当应用于电子设计过程的新技术和,已经能够在电子电路设计与方针、集成电路板图设计、可编程器件的编程以及印刷电路板设计等领域得到广泛应用。通用异步收发器简称UART,是一种通用串行数据总线,能够进行双向通信并实现全双工传输和接收。当前,在嵌入式设计当中,通用异步收发器主要用于与计算机进行通信。通用异步收发器在工作当中基本上分为发生和接收两个过程,并且会涉及到奇偶校验位发生器、波特率发生器、顶层模块等模块。

二、基于EDA技术的通用异步收发器的具体设计

2.1奇偶校验位发生器设计

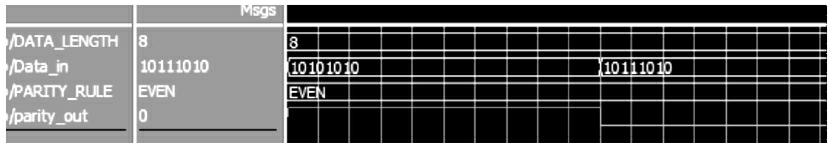

基于EDA技术的通用异步收发器奇偶校验位发生器设计,必须要能够满足以下几个方面的功能:首先,所设计的奇偶校验位发生器,要能够根据奇偶校验规则,即奇校验为ODD,偶校验为EVEN,进行恰当选定后输入相应的串行二进制数据,将校验位进行准确的计算,并且与输入的串行数据校验位进行比较,由此判断数据的正确或者错误。其次,该奇偶校验位发生器必须要能够根据具体的检验规则,准确的为计算机所发送的并行数据添加相应校验位。为了保证该奇偶校验位发生器设计能够满足要求,一般会选用modelsim软件对其进行功能仿真(如图1),并且对仿真结果进行分析。

2.2波特率发生器设计

波特率发生器一般需要为通用异步收发器当中数据接收与发送过程所产生的计数器与串行数据发送中的移位寄存器提供时钟。若要保证数据发送或者接收能够按照RS-232串行通信时序要求进行,则必须要保证波特率发生器所产生的功能与RS-232通信所产生的波特率具有同步时钟[1]。例如,若要波特率为9600bit/s,进行串行数据发生与接收时必须将占空比设置为50%的波特率时钟,数据接收与发送过程中的计数器在计数达到5208*50%=2604并且输出高电平之后,计数达到5208时,输出置低电平且重新计数[2]。

2.3顶层模块设计

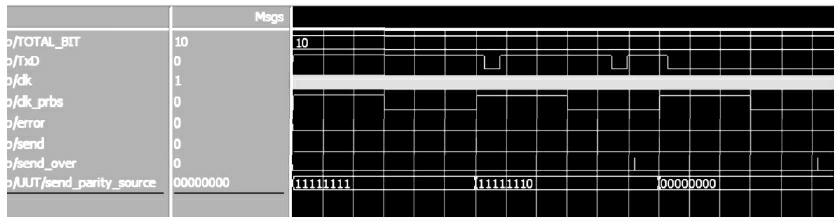

通用异步收发器的顶层模块包括诸多接口定义,主要用于实现收发内和与各个模块之间的相互连接。若通用异步收发器的波特率为9600bit/s,在进行发送功能仿真时将能够得到相应的仿真结果,如图2所示。从该图的相关结果可以发现,TOTAL-BIT是总数据位数,在计算机发送给通用异步收发器的等待TxD口发送数据为01010101,接触send信号后,输出的数据为001010101,该数据当中的第一位为起始位,中间八位则为TxD发送完成以后输出的指示信号,例如在RxD上表示为0101010010,起始位为0,其后则为101010010[3]。

结论:综上所述,利用EDA技术进行通用异步收发器的设计,在一定程度上能够实现异步串行通信功能。对于设计的通用异步收发器各个模块,基本上可以利用modelsim软件进行功能仿真与校验。从整体上而言,基于EDA技术的通用异步收发器具有较高灵活性,在实际的应用当中能够恰当调整波特率发生器分频参数,且能够根据不同的数据帧格式进行不同方式的校验,具有一定准确性和直观性,值得在教学以及实际当中广泛应用。

参 考 文 献

[1]同晓荣,盛仲飙.基于FPGA实现CRC校验功能的通用异步串口通信[J].信息技术,2012,03(04):27-29.

[2]王友瑞,石伟,王志英,等.基于同步EDA工具的异步电路设计流程[J].计算机研究与发展,2012,09(08):2027-2035.

[3]王磊,李超,胡春喜.一种多功能通用异步串行UART接口的设计与实现[J].四川兵工学报,2014,12(03):101-103.