多用户数传下RS+CC级联码应用

2013-10-27刘博,朱江

刘 博, 朱 江

(国防科学技术大学,湖南 长沙 410073)

0 引言

RS+CC级联码因其具有较低的噪声门限、良好的误码特性,被广泛应用于星载交换系统中,其中欧洲的DVB-S系统就采用了RS+CC级联码的编码方案。目前,基于RS+CC级联码原理,已经实现成硬件编译码电路[1-2],其中Xilinx公司已经设计出相关的IP-Core,为系统设计提供了便利。为实现多用户解调[3-4],星载交换系统通常采用FDMA或TDMA传输体制,因卷积码本身的记忆特性,RS+CC编译码器不能像分组码那样直接复用,通常需要进行并行编译码。随用户数增多,硬件规模将变得十分庞大,以至于难以在星载交换机上实现。文中经过比较分析,基于TDMA体制提出通过设计用户帧结构,使得卷积编码器在一定输出一定长度数据流后迫零,消除卷积码编码器的记忆,从而在发射端、接收端只需分别使用一个RS+CC级联码高速编码器、高速译码器就能处理多路低速数据流。第二节分别对传统实现方法和该文提出的实现方法进行了硬件规模、存储空间资源需求进行了分析;第三节针对该文提出的实现方法进行了软件仿真验证,验证了方法的正确性;第四节给出相应的结论。

1 RS+交织+CC级联码原理及实现

星载宽带变速率调制解调器要求实现基于欧洲空间数据系统咨询委员会(CCSDS,The Consultative Committee for Space Data Systems)提出的标准中的 RS (223,255)码+交织+(2,1,7)卷积码和RS (223,255)码+交织+3/4卷积码。其中,3/4卷积码通过(2,1,7)卷积码删余得到。文中重点讨论 RS(223,255)码+交织+(2,1,7)卷积码的实现。

根据CCSDS标准,选择:RS (223,255)码、交织深度为5的分块符号交织、(2,1,7)卷积码。同时,设计考虑兼容标准给出的3/4卷积码。

为了消除卷积码记忆性带来的影响,基于Xilinx FPGA有3种解决方案:①用户间采用并行编译码;②配置卷积码译码器IP-Core为多通道译码模式;③设计用户帧结构,使其能够满足使用单个高速编译码器处理多路并行数据流的要求。下面对3种方案进行硬件规模、传输效率进行分析。

1.1 实现方案分析

目前,Xilinx公司设计出了RS编码器、RS译码器、卷积编码器、卷积译码器(支持最多 32通道译码,可以根据数据速率选择串行、并行结构) 的IP-Core[5-8]。

以用户数 N=4为例,基于 Xinlinx提供的IP-Core,参照数据手册给出的实现结果。针对硬件资源占用最大的RS编码器、RS译码器、卷积码译码器以及存储空间资源需求进行分析、讨论。其中:RS编码器、RS译码器、卷积译码器的实现均基于XC6VLX130T。传输效率的讨论忽略同步头。

1.1.1 基于全并行编译码

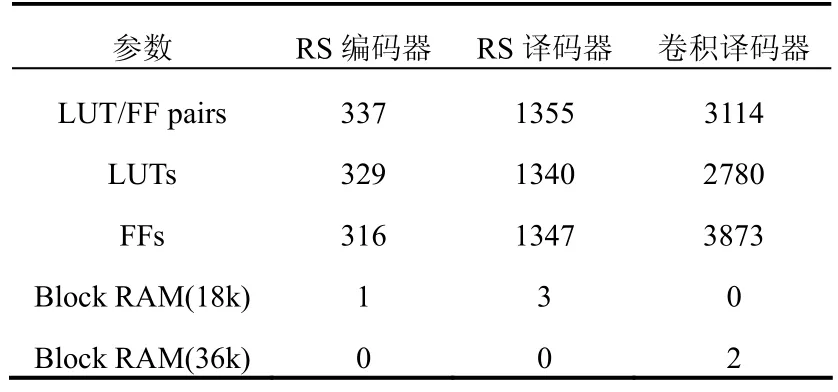

该方案中,卷积译码器不需要采用高速实现。因此,基于串行结构分析,忽略额外存储空间。该方案传输效率为:223/510=43.7%。总体硬件规模[5-8]如表1所示。

表1 四用户全并行实现的硬件规模

不难分析到,因采用了全并行编译码的实现结构。当用户数量增多时,硬件规模线性增长,将变得十分庞大。如果串行实现的卷积译码器无法满足处理要求,则必须采用并行实现的卷积译码器,硬件规模更加庞大。这对于星载交换系统来说,是难以实现的。

1.1.2 基于卷积译码器IP-Core的多通道译码模式

该方案基于单路高速编译码器处理多路低速数据流的思想,利用Xilinx提供的卷积译码器IP-Core本身具备的多通道译码功能,最大可以完成32用户的译码。RS编译码器的IP-Core本身可以实现高速编译码,通过TDM方式可以实现多路低速编译码。这样,不需要对帧结构进行设计。根据数据手册给出的输入输出时序,需要在卷积译码器输入端、卷积译码器输出端、解交织输出端加入缓存,因此硬件规模[5-9]如表2所示。

表2 采用卷积译码器多通道译码模式方案的硬件规模

其中,额外需要缓存空间:21675字节。该方案传输效率为:223/510=43.7%。随用户数增加,硬件规模会有一定增长。存储空间的需求将线性增长,存储空间需求将变得十分庞大。也难以实现在星载交换系统中。

1.1.3 基于帧结构设计

采用TDMA方式,即每个时隙发送/接收一个用户超帧。用户与用户之间应当没有相互干扰,因此,在用户完成卷积编码后需要对编码器迫零。进行卷积编码前,数据帧结构应当满足以下要求:

1)在上一个用户完成卷积编码后,卷积编码器应当回到初始状态(假定为全零)。即,卷积编码器需要迫零。

2)单个用户帧结构应当满足交织器的要求。即,卷积编码前,每个用户帧应当包含5或者5的倍数个RS码字。

3)考虑到设计的帧结构需要同时适应1/2、3/4卷积码编码体制,迫零长度应当为3的倍数。

4)便于处理电路的硬件实现。

基于以上4点,不考虑同步头。4路用户发送的数据合路为单路高速数据流后,结构应当如图 1所示。

图1 四路低速数据流合路以后的帧结构

对于单个用户,进入卷积编码器以前的数据帧结构如图2所示。

图2 进入卷积编码器前的帧结构

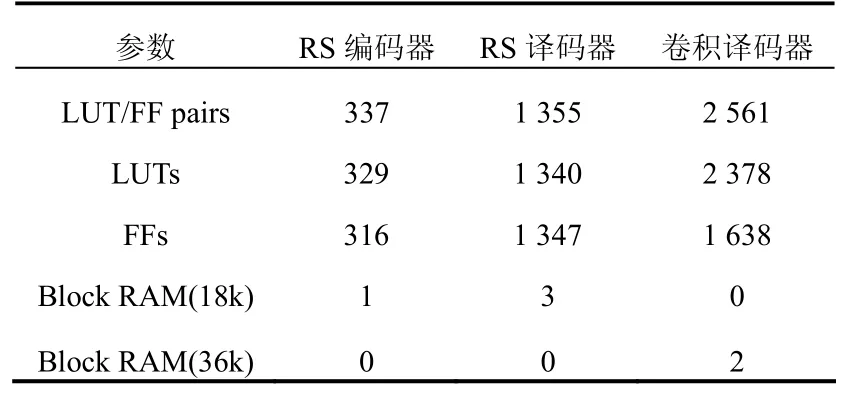

根据上述分析,在卷积编码之前,需要在数据末尾增补3字节全零尾码。因此在卷积编码之前(用于增补全零尾码)、解交织之前、解交织之后需要加入缓存。这里 RS编译码器、卷积译码器需要高速实现,其中RS编译码器IP-Core本身可以达到高速处理的要求,硬件规模[5-9]如表3所示。

表3 单个高速编译码器处理多路低速数据流方案的硬件规模

缓存空间需求:3831 Byte。该方案传输效率为:43.6%。只要用户传输速率满足要求,硬件规模、存储空间的需求均不会有显著的增大。能够满足星载交换系统的应用要求。发射、接收两端硬件实现框图(未画出缓存)如图3所示。

图3 发射端硬件实现框

总控模块主要完成以下功能:①控制选通开关选择1~4号用户的数据,并根据选通的用户控制产生不同的同步序列;②在用户切换期间,关断之后的各模块,切换完成打开各模块;③接收交织、尾码增补、加同步头模块的发出的指示信号,并发出相应的控制信号。同步头采用具有强相关特性的序列,用户间使用长度相同、互不相关的同步序列,以便于接收端进行用户识别,如图4所示。

图4 接收端硬件实现框

总控模块主要完成以下功能:①根据帧同步模块的结果识别对应的用户,并控制选通开关,选择1~4号用户的数据;②接收交织、尾码增补、加同步头模块的发出的指示信号,并发出相应的控制信号;③根据帧同步模块发出的指示信号,控制其余各模块的通断。

2 性能仿真

以 4用户、1/2卷积码为例,映射方式选用BPSK;基于MATLAB搭建仿真平台。仿真至10-3误码率。假设信道为AWGN信道。分别记录相同比特信噪比下,每个用户的输出误码率。做出误码曲线如图5所示,可以有效地对多用户信号进行译码接收。

图5 性能仿真

现将前述3种实现方案性能做以下对比如表4所示。

表4 3种方案性能对比

3 结语

RS+CC级联码因其较低的噪声门限和良好的误码特性[9-12],被广泛应用于星载交换系统中。星载交换系统多采用FDMA、TDMA两种体制,通常与之对应的 RS+CC级联码需要采用全并行编译码或要求卷积译码器具有多通道译码功能。以上两种处理方法随着用户数的增多,硬件规模、存储空间需求将变得十分庞大。这一缺点使得以上两种方案难以星上实现。文中通过硬件资源分析、软件仿真验证,提出通过对用户数据帧结构的设计,使卷积编码器迫零,进而能够使用单个高速编译码器处理多路低速数据流的设计方案。经分析比较,当用户数为4时,该方案硬件规模约为传统全并行编译码方案的25%,也略小于采用多通道卷积译码器的方案;传统的两套方案其硬件规模会随用户数的增多而增大,而文中提出的方案,只要用户数据速率总和在编译码器的处理速率范围内,硬件规模几乎不会增长;且存储器空间需求适中,明显小于采用多通道卷积译码器的方案。较两种传统方案,文中提出的方案几乎没有传输效率的损失。综合以上分析,文中提出的方案硬件规模小、存储空间资源需求适中,只要用户数据速率总和在编译码器的处理速率范围内,硬件规模几乎不会增长,且相比传统实现方案几乎没有传输效率的损失。最适合星上的系统实现。

[1]邓宏贵,黎辉勇,李志坚.RS+交织+卷积码级联纠错的FPGA实现[J].信息与控制,2007,36(06):772-776.

[2]龙昭华,王国锋,雷维嘉.RS-CC的级联编码设计及其嵌入式 FPGA实现[J].计算机工程与设计,2009,30(23):5369-5375.

[3](University of Toledo) KWATRA C S,JAMALI M M.High Speed Hardware Development For FDMA/TDM System[EB/OL].(1992-01-27)[2012-12-24].www.adsabs.har vard.edu.

[4](NASA) IVANCIC D W,BUDINGER J M,STAPIES J E,et al.Multichannel Demultiplexer/ Demodulator Technologies For Future Satelitte Communication Systems[EB/OL].(1992-05-18)[2012-12-24].www.ntrs.nasa.gov.

[5](Xilinx)Xilinx.LogiCORE™ IP Reed-Solomon Encoder v7.1[EB/OL].(2010-07-23)[2012-12-24].www.xilinx.com.

[6](Xilinx)Xilinx.Convolution Encoder v7.0 [EB/OL].(2009-06-24)[2012-12-24].www.xilinx.com.

[7](Xilinx)Xilinx.Viterbi Decoder v7.0 [EB/OL].(2010-06-24)[2012-12-24].www.xilinx.com.

[8](Xilinx)Xilinx.LogiCORE™ IP Reed-Solomon Decoder v7.1[EB/OL].(2010-07-23)[2012-12-24].www.xilinx.com.

[9]CCSDS.TM Synchronization And Channel Coding[S].CCSDS 131.0-P-1.1, Washington DC:CCSDS, 2009:88.

[10]SHU Lin.差错控制编码[M].晏坚译.北京:机械工业出版社,2007:502.

[11]王忠华,王笃文,吴兵.基于深空通信的级联码译码器实现[J].通信技术,2011,44(11):32-34.

[12]张威,徐熙宗,张克,等.RS级联编码在短波通信与卫星通信信道的仿真分析[J].通信技术,2009,42(02):27-29.