基于DDS 快速跳频的时分多信道干扰的实现

2013-10-21刘云光和玉竹

刘云光 和玉竹

(四川九洲电器集团有限责任公司 绵阳 621000)

0 引言

DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。DDS 技术推动了频率合成领域的高速发展,由于其转换速度快、频率分辨率高等特点,大量应用于通信及电子对抗领域,克服了模拟式频率合成技术转换速度慢、频率分辨率低且设置不灵活等缺点[1]。

本文介绍了一种基于DDS 技术的干扰系统实现方法。通过快速调频方式,采用瞄准式干扰,可同时干扰多个信道通信。

1 时分多信道干扰原理

美国哈佛大学米勒(Miller)和里克李德(Licklider)以及英国研究院公开发表的题为“Intelligibility of Voice communications subject to periodic interruptions”的文章均指出:通过试验验证,在同等功率条件下,用一部瞄准式干扰机同时干扰多个工作在不同信道的接收机是可行性的[2]。时分干扰时序图如图1 所示。

图1 时分干扰时序图

研究表明,当时分干扰的中断率为2000 次/s时,干扰时间百分率≥20%,就可以达到破坏通信的目的。在0.5ms 的一个周期中,如果干扰4 个信号,考虑频率转换时间和信号建立时间两个因素,设转换时间为5μs,干扰对象带宽为B=25kHz,信号建立到90%需时为0.7/B=28μs。因此,针对每个信号的干扰时间Tj为92μs。干扰时间百分率为18.4%。

通过以上计算得出,在中断率为2000 次/s 时,如果干扰4 个信号,干扰时间百分率为18.4%(低于20%),无法达到有效的干扰效果。

如果干扰3 个信号,干扰时间百分率为27%。可见,干扰时间百分率>20%,这样干扰效果是很好的。

2 时分多信道干扰实现方式

目前,实现时分多信道干扰的方法主要有两种:一种是只用一个激励源,通过快速改变频率来实现分时干扰;另一种是采用多个激励源,通过电子开关快速切换实现分时干扰。两种方案的系统原理图如图2 所示。

图2 分时干扰系统原理

比较以上两种方案,方案一具有系统结构简单、成本低、可靠性高、电磁兼容性好等特点。激励源由于采用了DDS 直接数字式合成频率源,同时也具备了频率切换速度快,输出波形灵活、杂散小等特点[3]。下面详细介绍方案一中激励源的软、硬件实现方式。

3 基于AD9858 快速跳频激励源的实现

3.1 DDS 原理简介

频率源分为自激振荡源和合成频率源两大类。与自激振荡源相比,合成频率源具有性能指标优越、控制方式简单灵活等优点。直接数字式合成频率源(DDS)的相位噪声、频率步进、跳频速度、调制能力、体积重量及成本等性能指标相比其他合成频率源都具有优势,因此,现代跳频通信及电子对抗系统中的频率源广泛采用DDS 技术。

DDS 技术是一种把一系列数字形式的信号通过A/D 转换成模拟形式的信号的合成技术。其原理框图如图3 所示。

图3 DDS 原理框图

相位累加器在K 位频率控制字FCW 的控制下,以参考时钟频率Fr为采样率,产生待合成信号相位的数字线性序列。将其高P 位作为地址码,通过查询正弦表ROM,产生S 位对应信号波形的数字序列S(n),再由数/模转换器(DAC)将其转化为阶梯模拟电压波形S(t),最后由低通滤波器LPF 平滑为正弦波输出。频率控制字FCW 和时钟频率Fr共同决定了DDS 输出信号的频率Fd。他们之间的关系满足:Fd=FCW/(2N×Fr)。

3.2 系统方案

应用DDS 技术,本文设计了一种快速跳频源,其系统方案原理如图4 所示。

图4 快速跳频设计原理图

3.3 硬件设计

3.3.1 参考时钟源(PLL)设计

AD9858 芯片最高可采用1GHz 参考时钟,内部含有2 分频电路,可选择外部输入参考信号为1GHz或2GHz。本文采用锁相环(PLL)方式合成1GHz 外部参考源供给AD9858 芯片做参考。PLL 的原理框图如图5 所示。

图5 PLL 原理框图

考虑电路的小型化,PLL 采用集成了VCO 的锁相环时钟发生器ADF4360-7。ADF4360-7 是ADI 公司2004 年新推出的一款高性能PLL 芯片,具有很宽的工作频带,输出频率范围为350-1800MHz,且其内部集成了VCO,由外部电感值设定不同的工作频段,方便了锁相环路的设计[4]。

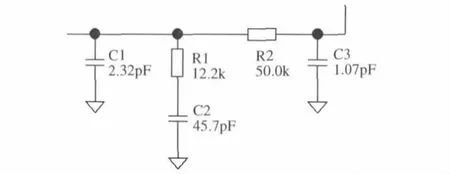

ADF4360-7 组成的PLL 需外部提供环路滤波电路,本文用ADI 公司提供的仿真软件ADI-SimPLL计算出环路滤波电路为的电阻和电容值分别为C1=2.32pF,C2=45.7pF,C3=1.07pF,R1=12.2kΩ,R=50kΩ。环路滤波器结构图如图6 所示。

图6 环路滤波器结构图

ADF4360-7 内部可通过配置R 计数器配置输入预分频器,从而将输入参考信号R 分频得到相应的鉴相频率。本文设计用8MHz 的晶振做为ADF4360-7 的输入参考,并将R 计数器置1,得到8MHz 的鉴相频率。采用较高的鉴相频率有利于提高环路的捕捉时间,降低环路的相位噪声[5]。设定N=125,则B=15,P=8,A=5。输入8MHz 的鉴相频率,则输出频率为125 ×8MHz=1000MHz。

3.3.2 AD9858 电路设计

AD9858 芯片集成了具有1 千兆次/秒采样速率的DDS 电路,10 位的D/A 转换器,数字鉴相器和2GHz 的模拟混频器,并带有8 位并行及SPI 串行控制接口。AD9858 具有并行和串行两种送数方式。为了加快频率设置时间,本文采用并行送数方式。AD9858 有八个双向数据口(D0~D7)、六个地址输入口(ADDR0~ADDR5)、一个读控制口和一个写控制口。数据经双向数据口传输,通过置低读写控制口来控制数据的读出和写入。六个地址输入口用来选择数据需写入的寄存器。AD9858内自带4 个频率寄存器,可预先在4 个频率寄存器中写入4 个频点信息,并通过外部信号控制PS1 和PS0 口选择4 个频率寄存器中的一个输出。AD9858 内部结构如图7 所示。

前文提到采用3 个频点跳频的方式可使干扰时间百分率>20%,起到良好的干扰效果,因此本文设计采用预先写入3 个频点数据,通过单片机控制PS1 和PS0 快速选择频率输出的方式实现对3 个信号的快速跳频干扰。AD9858 的外围电路设计如图8 所示。

图7 AD9858 内部结构框图

图8 AD9858 外围电路图

3.4 软件设计

系 统 MCU 采 用 MICROCHIP 公 司 的dsPIC30f6014A 芯片,该芯片可采用内部时钟,最高工作速度可达30MIPS,则最快机器周期约为33ns。将单片机两个与PS1 和PS0 相连并输出高低电平控制PS1 和PS0 在00、01、10 之间不停切换,从而控制AD9858 在3 个频率寄存器间切换输出预先存入的三个频率信号,实现3 个信号的快速跳频[2]。AD9858 和PLL 都是通过dsPIC30f6014A 控制的,控制的软件流程图如图9 所示。

开机、上电复位后,开始执行初始化程序。首先对PLL 电路进行初始化配置。采用串行方式对ADF4360-7 进行配置,ADF4360-7 的时序图如图10所示。

图9 软件控制流程图

图11 AD9858 时序图

PLL 配置好后为AD9858 提供了1GHz 的参考时钟频率,然后对DDS 进行初始化配置。首先配置控制寄存器(CFR),其次写频率1 到(FTW0)寄存器,频率2 到(FTW1)寄存器,频率3 到(FTW2)寄存器。然后通过PS1、PS0 管脚选择相应频率信号,对应关系如表1 所示。

表1 AD9858 FTW 寄存器对应关系

FTW 为32 位的频率寄存器,通过公式F=(FTW×SYSCLK)/2N计算得出。式中F 为设置频率,单位为Hz;SYSCLK 为参考时钟频率,本文为1GHZ;AD9858 的N=32。计算出FTW 后可根据图11 所示的时序图所示将对应频率写入寄存器。

配置完AD9858 的频率信息后,使用一个循环程序循环不断的选择3 个频率信号输出完成跳频。

3.5 测试结果

利用Aglient N9010A 信号分析仪测试,输出间隔25kHz 的三个点:150.0494MHz,150.0244MHz,149.9994MHz 的快速跳频信号的频谱图如图12所示。

图12 跳频频谱图

4 结束语

由于AD9858 具有频率精度高、频率转换时间快等特点,同时,兼具硬件实现较为简单、控制方式灵活方便、电路可靠性高、成本低等优点。因此,采用这种实现方式实现的激励源可广泛应用于通信对抗、雷达对抗等领域,应用前景广阔。

[1]黄旭.基于单片机和AD9858 的4 频点快速跳频设计[J].国外电子元器件,2005,(3) :8-11.

[2]朱庆厚.通信干扰技术及其在频谱管理中的应用[M].北京:人民邮电出版社,2010.

[3]高泽溪,高成,直接数字频率合成器(DDS) 及其性能分析[J].北京航空航天大学学报,1998,(5) :31.

[4]远坂俊昭.锁相环(PLL) 电路设计与应用[M].北京:科学出版社,2006.

[5]沈伟,基于ADF4360-7 的宽带雷达信号源设计[J].现代雷达,2006,(08) :153-256.