一种任意抽取数字下变频器的设计

2013-09-30袁子乔

袁子乔 刘 翔

(西安电子工程研究所 西安 710100)

0 引言

数字下变频(DDC)是雷达数字接收机的重要组成部分,它位于ADC采样芯片之后,主要功能是:对采样后的中频回波信号进行混频和滤波处理,将其变换至零中频;对零中频数据进行抽取及抗混叠滤波处理,从而降低数据速率以适应后端通用DSP器件对信号实时处理的要求。随着芯片运算速度的提高,大型相控阵雷达采用数字波束形成(DBF)技术进行接收波束控制成为可能,而采用DBF技术,需要大量的采用ADC和DDC通道,因此,将处理过程相对简单但运算量巨大的DDC模块进行ASIC设计,对于降低相控阵雷达接收通道的成本,有着非常重要的作用。

雷达在不同的工作模式下,雷达发射信号的形式和滤波器的抽取率有所不同,需要设计不同频率响应、阶数和抽取率的低通滤波器,因此需要充分考虑不同抽取率下的低通滤波器,实现资源复用,造成了资源浪费。本文基于低通滤波法提出了任意抽取率数字下变频器的架构,该数字下变频器根据数字下变频运算的特点,选取合适的滤波器阶数和工作时钟,使用相同的乘法器资源则可实现多抽取率的数字下变频器,实现了不同模式下的乘法器资源复用,较大程度节约了乘法器资源。

1 低通滤波法实现DDC

图1为低通滤波法实现DDC的原理框图,输入中频信号x(t)的中心频率为f0,带宽为B,A/D采样频率为fs,经A/D采样后,以数字信号x(n)的形式输出。数字信号x(n)与正交的本振信号分别相乘,将信号分为I,Q两路,两路信号再经过低通滤波抽取后,得到正交双通道信号I(n)和Q(n);两路滤波器系数均为 h(n)[1]。

图1 低通滤波法实现DDC的原理框图

由于中频信号中心频率为f0,带宽为 B,位于(fL,fH)之间,则A/D转换器的采样频率fs需要满足带通采样定理:,M=0,1,2,…;M 取能满足fs≥2B的最大整数,则根据fs进行等间隔采样所得到的采样信号x(n),就能准确的恢复出原始信号x(t)[2]。

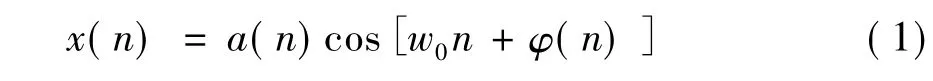

假设采样后的输入信号为:

上式中ω0=2πf0/fs,φ(n)为中频信号的相位信息。本振信号的频率要求与载波频率相等,对输入信号分别乘以正交的本振信号,可得到:

I路:

Q路:

由式(2)、(3)看出:经过数字正交混频后,输出信号包括了我们需要的低频分量,以及二倍载波频率(2ω0)的高频成分,幅度值均为原来的二分之一。利用低通滤波器滤除不需要的高频成分,即可得到需要的基带信号。经数字低通滤波器后得到的信号表达式为:

其中I(n)和Q(n)分别表示信号的同相分量和正交分量。

按照图1的原理框图,设计了数字下变频芯片的框图如图2所示。主要包括:数字正交混频、任意抽取低通滤波器、系数存储器、SPI控制接口。

图2 数字下变频芯片框图

其中SPI接口作为设置芯片参数的接口,在芯片正常工作前,实现对频率控制字、相位控制字、抽取率以及低通滤波器系数的配置。

2 数字正交混频

数字正交混频可以采用查找表+乘法器,或者采用Cordic算法进行向量旋转来实现。基于查找表的NCO需要占用大量的ROM存储器资源,才能保证一定的精度[3]。而基于Cordic算法进行向量旋转不需要使用存储器资源,仅通过多级流水即可实现输入向量的角度旋转,如图3所示。

图3 数字混频模块框图

为了保证数字混频的精确度,设计时Cordic采用16级流水线结构,Cordic的具体实现参见文献[4]。Cordic算法最大能实现[-99.88°,99.88°]之间的角度旋转,而数字混频中向量的旋转角度范围是[0°,360°],因此需要进行输入数据和旋转角度转换,将向量[90°,270°]之间的旋转角度转化为[-90°,90°]之间的旋转角度[4-5]。

表1 输入数据转换表

3 任意抽取低通滤波器

从图4可以看出,从d0至d16、d17至d32使用SRL(移位寄存器)进行数据的延时,延时时钟周期为抽取率,例如2抽取时,延时2个时钟周期,10抽取时,延时10个时钟周期,移位寄存器的深度决定最大抽取率。

反序是将输入数据的顺序以每抽取个数为一组,按照相反的顺序输出。如图5所示的4抽取数据流,以输入顺序的自然数为例,d16为d15延时4个时钟周期得到,而d17为d15延时4个时钟周期,并以4个数据为一组,按输入数据相反的顺序输出,反序部分可以采用移位寄存器或者存储器来实现。

使用移位寄存器产生指定时序的数据流后,可进入乘累加处理环节。当滤波器系数对称时,可通过预先加法将对称位置的数据相加,然后与对应的滤波器系数进行乘累加运算,这样可以减少一半的乘法器资源。另外,由于输入数据率较低,因此可以使用运行在较高时钟速率的乘法器,分时复用进行乘累加运算,乘法器运行速率越高节约的乘法器资源也越多,一般乘法器的工作时钟为输入数据率的整数倍,当然乘法器的最高工作时钟受芯片工艺的限制,需要综合考虑[6]。

图6 任意抽取低通滤波器

本设计在不同抽取率情况下(见图6),输入数据率均为clk1x,滤波器工作时钟为clk2x,低通滤波器采用对称系数,表2给出了不同抽取率下对应的滤波器阶数。

表2 不同抽取率对应的滤波器阶数

图7 数据整理时序图

如图7所示,数据整理是将两个clk1x数据率的数据整合为一个clk2x的数据率的数据,产生标志位flag信号区分d1和d2,产生标志位bypass信号标识一组乘累加运算数据的第一个数。

经过乘法累加器输出后,将数据的时钟域从clk2x变到clk1x,降低8路求和运算速率要求,可以采用3级流水并使用逻辑来实现8路数据的求和。输出结果为输入数据的数字下变频结果。

4 结束语

本文提出了一种采用优化结构实现数字下变频的方法。针对不同抽取率的数字下变频,选取合适的低通滤波器阶数和工作时钟,复用相同的乘法器资源可以实现不同抽取率的数字下变频处理,满足了雷达信号处理大部分情况的使用要求,由于采用优化的结构尽量减小逻辑资源,降低了ASIC芯片的成本和复杂度。

[1]胡广书.数字信号处理理论算法与实现[M].北京:清华大学出版社,2003.

[2]高亚军.基于FPGA的数字信号处理[M].北京:电子工业出版社,2012.

[3]田耘.无线通信FPGA设计[M].北京:电子工业出版社,2009.

[4]吴曙荣.直接数字频率合成器的设计[D].西安:西安电子科技大学,2006.

[5]鲍景富.现代频率合成技术的研究进展[J].电视技术,2007,47(2):1 -5.

[6]迟忠君,徐云,常飞.频率合成技术发展概述[J].现代科学仪器,2006,(3):21 -25.