基于F2812的改进型数字锁相环研究

2013-09-22,,

,,

(1.盐城工学院 电气工程学院,江苏 盐城 224000;2.三一重机有限公司大型挖掘机研究所,江苏 昆山 215300;3.泰州供电公司电力调度中心,江苏 泰州 225300)

1 引言

锁相环是目前使用最普遍的相位同步方法,对于与公共电网连接的变换器,锁相环用来检测电网电压相位,提供计算基准,使变换器与电网同步运行,锁相环性能的优劣将直接关系到变换器的性能和稳定性。随着锁相环技术的发展,锁相环已经广泛用于分布式发电系统(DG),高压直流输电系统(HVDC),静止无功补偿器(SVC)和不间断电源(UPS)等电力电子装置。

目前,实现锁相方法有用于单相的过零点检测法,用于三相的基于低通滤波器(LPF)开环锁相方法,基于dq坐标变换的闭环锁相方法和EPLL锁相法。过零点检测法的优点为原理和结构简单,但文献[1]指出当输入电压在过零点畸变时,锁相环输出在过零点易振荡。基于LPF开环锁相方法可以滤除电网谐波的影响,但LPF降低了系统的动态响应速度[2]。文献[3]指出基于dq坐标变换的闭环锁相方法在三相输入不平衡时,输出存在2次谐波。EPLL锁相法由Karimi和Ziarani提出[4-5],适用单相和三相场合,其可以结合对称分量法解决三相输入不平衡的问题,所以研究价值较大[6]。

本文首先分析了EPLL性能,得出输入信号谐波含量的增加将会降低锁相环抑制谐波能力。其次,在其基础上提出一种改进数字锁相环方法,解决谐波含量变化对抑制谐波能力的影响,并给出数字实现方案,最终基于F2812 DSP进行实验验证。

2 谐波含量变化对EPLL性能影响

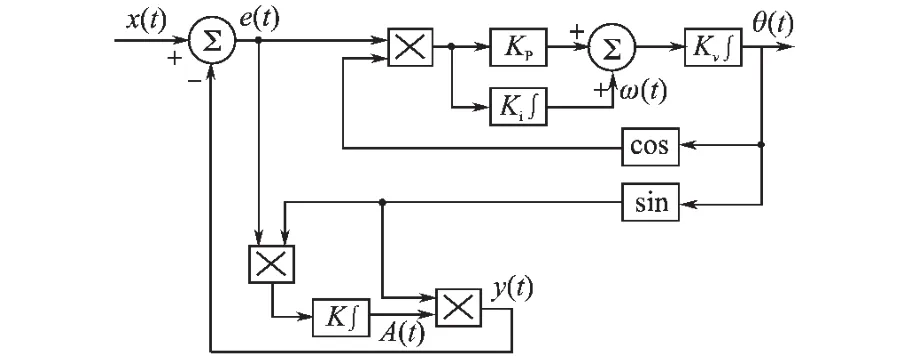

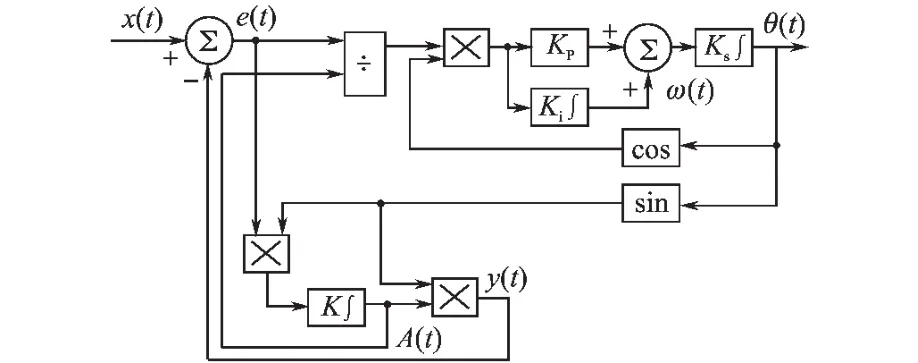

图1给出了 Karimi和 Ziarani提出的EPLL系统结构图,系统由输入信号x(t),基波幅值信号A(t),角频率信号ω(t)和相位信号θ(t)组成。

图1 EPLL系统结构图Fig.1 EPLL system structure

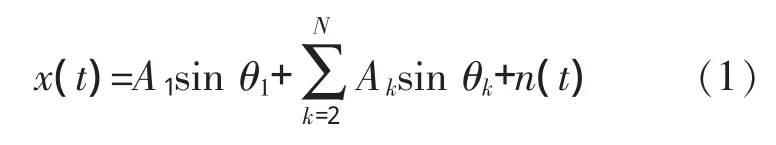

设输入信号表达式为

式中:A1为基波幅值;θ1为基波的相角;N为最大谐波次数;Ak为k次谐波幅值;θk为k次谐波信号相角;n(t)为噪声信号。

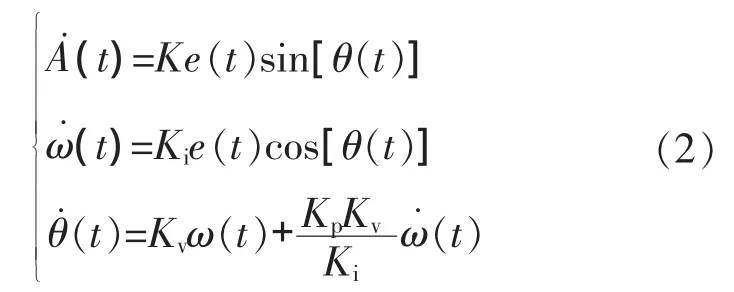

取 A(t),ω(t)和 θ(t)为状态变量,则:

当Kv恒定时,输出相位和参数Kp,Ki有关,对图1进行简化得到相位控制框图如图2所示。

图2等效相位控制框图Fig.2 Equivalent phase control block diagram

图 2 中,θref=ωt+ω0,θ为锁相角。 根据图 2 可以获得系统的开环和闭环传递函数:

根据式(3)分别画出3种情况下开环传递函数频率响应曲线,如图3所示。

图3 开环频率响应曲线Fig.3 Bode plot of open-loop system

图 3中,①对应 Kp=141.4,Ki=10 000;②对应Kp=282.8,Ki=10 000;③对应 Kp=141.4,Ki=10 000。从图3中可以看出,当Kp增大时,相角裕度和截止频率均增加;当Ki增大时,相角裕度减小,截止频率增加。

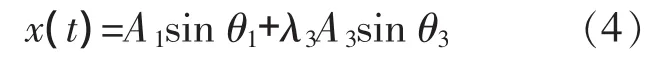

假设系统谐波变化时截止频率均小于5次谐波频率,式(1)可以简化为

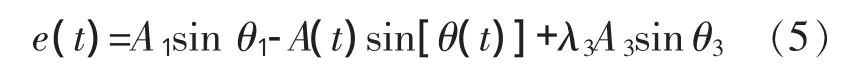

λ3为3次谐波变化因子,e(t)表示为

代入式(2)得:

可见,3次谐波变换因子λ3同样被引入到控制参数中。根据分析可知,当λ3>1时,系统截止频率将会增加,从而使系统谐波抑制能力减小。

3 改进数字锁相环分析及实现

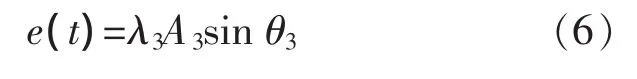

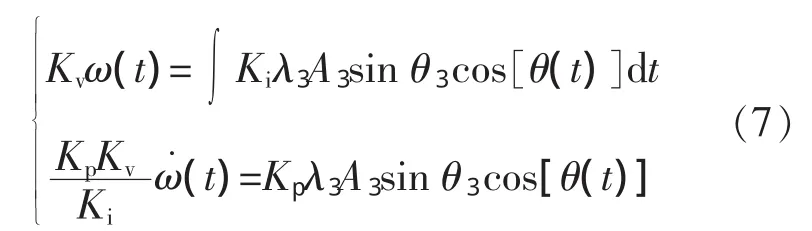

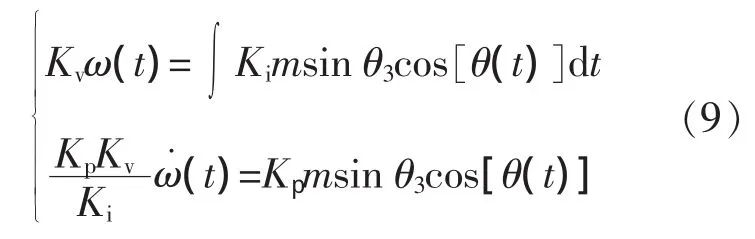

根据上一节分析可知,EPLL系统抑制谐波能力随3次谐波变化因子变化而变化,自适应能力较弱,为了解决这一问题,对其进一步分析,假设3次谐波最大变化值不超过基波幅值,即λ3A3≤A1,对式(6)两边同除以基波幅值 A1得:

令 m=λ3A3/A1,式(7)变化为

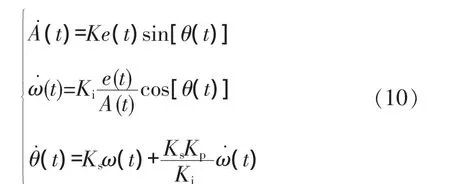

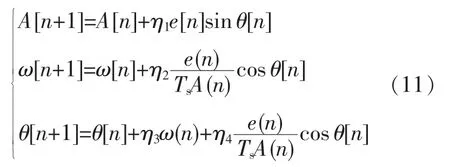

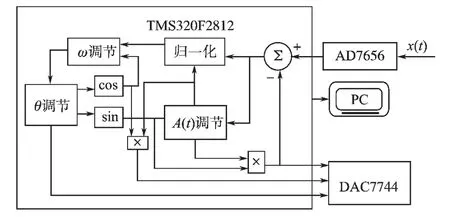

由于m≤1,所以在3谐波变化时,控制参数不会增加,系统抑制谐波能力不会减小。根据上述分析,如果对相位跟踪环节输入信号e(t)进行归一化处理,这样输入信号谐波含量的增加就不会减小谐波抑制能力。根据上述思想提出一种改进数字锁相环方法,其结构框图如图4所示。

图4 改进数字锁相环结构框图Fig.4 Improved DPLL structure

y(t)为基波信号,改进数字锁相环结构框图引入了e(t)/y(t)归一化环节,根据前面的分析知,该锁相方法可以屏蔽输入信号谐波含量变化对系统抑制谐波能力的影响。同样取A(t),ω(t)和θ(t)为状态变量,则:

式(1 0)对应的离散方程为

式中:Ts为采样时间;η1=TsK;η2=TsKi;η3=TsKs;η4=TsKpKs。

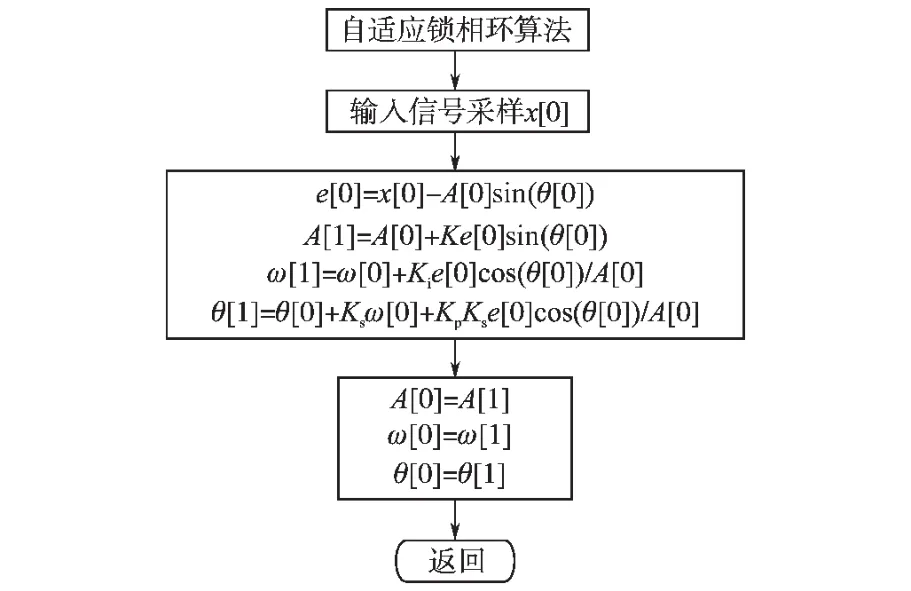

式(11)为实际在F2812内部运行的算法,程序流程图如图5所示。

图5 改进锁相环流程图Fig.5 Algorithm flowchart of improved PLL

4 实验结果及分析

为了验证改进数字锁相环方法的可行性,以F2812为主芯片,搭建实现2种锁相环试验平台,如图6所示。

图6 试验平台框图Fig.6 Block diagram of test platform

系统包括16位AD7656采样,算法实现,16位DAC7744 DA输出和上位机模块。输入信号由可编程交流源提供,实验参数为:基波幅值311 V,基波频率50 Hz,3次谐波含量为基波的20%。当λ3=1.5时,实验结果如图7所示。

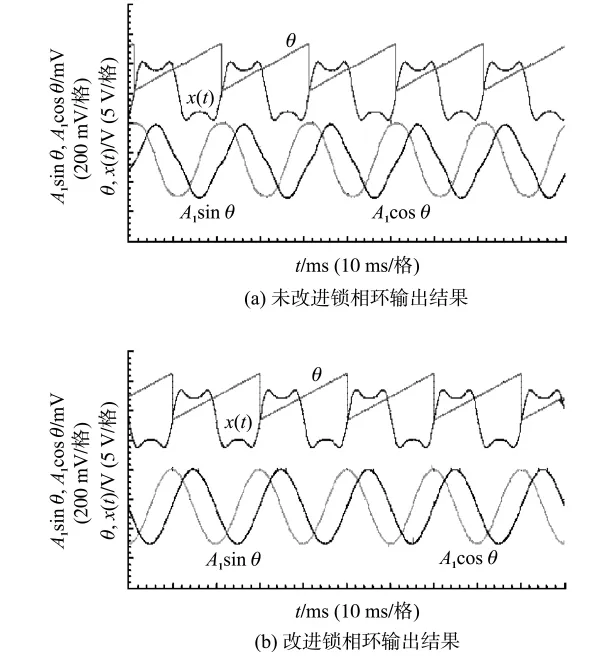

图7 λ3=1.5时,两种锁相环输出结果Fig.7 Experimental results of PLL with λ3=1.5

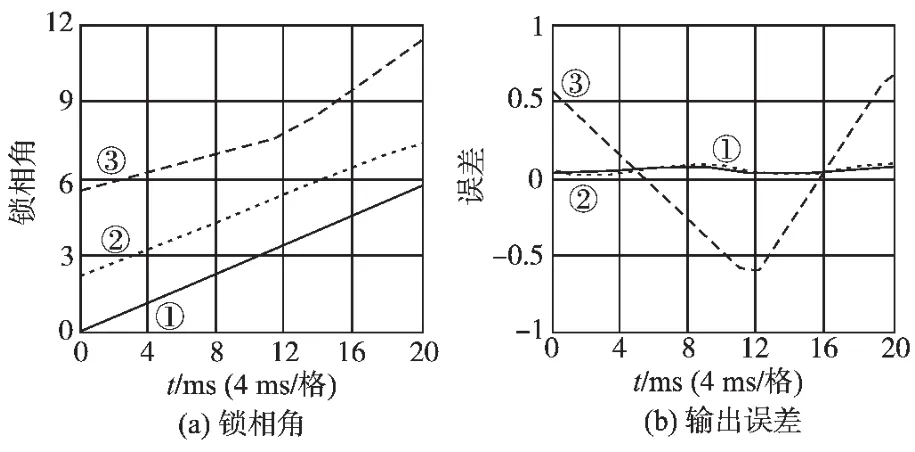

图 7 中,x(t)为输入信号,θ为输出锁相角,A1sin θ和Alcos θ对应DA输出的两路正交信号。实验结果表明3次谐波增加时,EPLL输出发生畸变,而改进锁相环仍能正确锁相,抑制谐波能力更强。当λ3=1.5时,将一个周期2种锁相环输出及误差数据经上位机发送并绘制曲线。改进前后输出锁相角及误差如图8所示。

图8 改进前后输出锁相角及误差Fig.8 Output phase locked angle anderro before and after improved

图8中,①为λ3=1时E P L L输出,②和③分别为λ3=1.5时改进前后锁相环输出,当3次谐波增加时,EPLL误差变大,输出畸变,而改进锁相环能够很好抑制谐波。实验结果很好地验证了前面相关理论分析。

5 结论

本文通过理论分析得出输入信号谐波含量的变化会改变EPLL截止频率,从而影响系统抑制谐波能力的结论。在此基础上提出一种改进锁相方法,该方法具有较强的谐波抑制能力,适用于谐波含量大范围变化场合。最后基于F2812搭建实现2种锁相环的实验平台,通过实验结果对比,验证了改进锁相环的优越性和可行性。

[1]Frede Blaabjerg, Remus Teodorescu, Marco Liserre, et al.Overview of Control and Grid Synchronization for Distributed Power Generation Systems [J].IEEE Transactions on Industrial Electronics,2006,53(5):1398-1409.

[2]孔雪娟,罗昉,彭力,等.基于周期控制的逆变器全数字锁相环的实现和参数设计[J].中国电机工程学报,2007,27(1):60-64.

[3]周国梁,石新春,付超.三相电压畸变条件下软件锁相环分析与实现[J].电力电子技术,2007,41(7): 47-49.

[4]Masoud Karimi Ghartemani.A Novel Three Phase Magnitudephase-locked Loop System[J].IEEE Transactions on Circuits and Systems,2006, 53(8): 1792-1802.

[5]田桂珍,王生铁,林百娟,等.电压不平衡条件下改进型锁相环的设计与实现[J].电力电子技术, 2010, 44(4): 85-89.

[6]谢邦立,蒋金明,李治理.锁相环技术在三相可逆PWM整流器中的应用研究[J].电气传动, 2008, 38(10): 29-32.

[7]张志文,申建强,曾志兵,等.基于新型全数字锁相环的SVG系统 [J].电气传动, 2010, 40(10): 36-39.