基于容栅传感器和单片机的检测系统

2013-09-04梁应选杨明亮

梁应选, 杨明亮

(陕西理工学院(北区)机械工程学院,陕西汉中723003)

0 引言

数显式百分表大多采用容栅式传感器,但由于大多未带微机接口,使其应用受到限制。国内学者就如何应用容栅式传感器和单片机构建检测系统进行了研究,并取得了一定的研究和应用成果[1-2]。但大多都遵循:传感器原理介绍→系统硬件构建→软件编程等基本思路。以上思路固然无误,但对于一线技术开发人员或单片机开发和应用的初学者来说,往往造成的结果是看得懂,做起来难。本文提出了结合容栅传感器原理,先用数字示波器对数显百分表输出信号(CLK信号、Date信号)进行观察,结合观测到的信号加深对原理的理解,再结合原理介绍中数据信号的采样过程,着重分析数显百分表实际显示数据与实际记录的二进制数对应关系。在此基础上,结合已有报道的容栅式传感器数据采集系统成功的经验就如何利用数显百分表为前端传感器,AT89S52单片机做为主控单元构建一个硬件结构简单、实时性强的检测系统,进行方案论证,并择优方案,最终设计构建出较为理想的智能检测系统。

1 容栅式传感器输出信号分析

容栅式传感器输出的电容信号经过容栅集成极芯片的处理可转化为数字信号输出。其中输出信号有4根线,分别为电源线(+1.5 V)、地线(0 V)、时钟控制线(CLK)和串行数据输出线(Date)[3-4]。

CLK为同步时钟信号,在一次数据传送中,开始为54μs的高电平,表示数据即将开始传送。接下来是Date输出两组各有24个宽度为13μs的窄脉冲,前组为绝对数据;后组为相对数据。前后两组数据之间有110μs的高电平作为间隔;最后是75μs的高电平,以示数据传送结束,其输出波形如图1所示。

Date信号为数据信号,它包含了传感器的位移信息。在数据采样时,容栅芯片在CLK信号窄脉冲的下降沿对Date信号进行采样,先后采样两组24位绝对数据和相对数据。

CLK时钟脉冲串的第1组对应的信号是包含基准0的绝对数据;第2组是减去基准0后的实际的位移值,为相对数据。绝对数据计数范围从000000H~FFFFFFH;相对数据有正负区分,可以进行清零。数据采用二进制编码,低位在前,高位在后,最后位为符号位,数据采集以时钟线每次CLK信号负跳变时刻为准进行数据采集。以上信号为非标准串行码,幅值均为1.5 V。绝对数据不能清零(含基准0),相对数据可以清零,故本次我们将直接读取相对数据进行研究。

2 数字示波器对输出数据分析

2.1 数据的读取

在数字示波器上可以观察到如图1所示数显百分表输出波形信号[5-6],CLK一个脉冲下降沿就可以读对应这个脉冲宽度内的Date数据的状态(高电平为1,低电平为0)。表1、2为测量时读到的相对数据的二进制。

图1 容栅式传感器输出脉冲时序图

2.2 数据分析处理

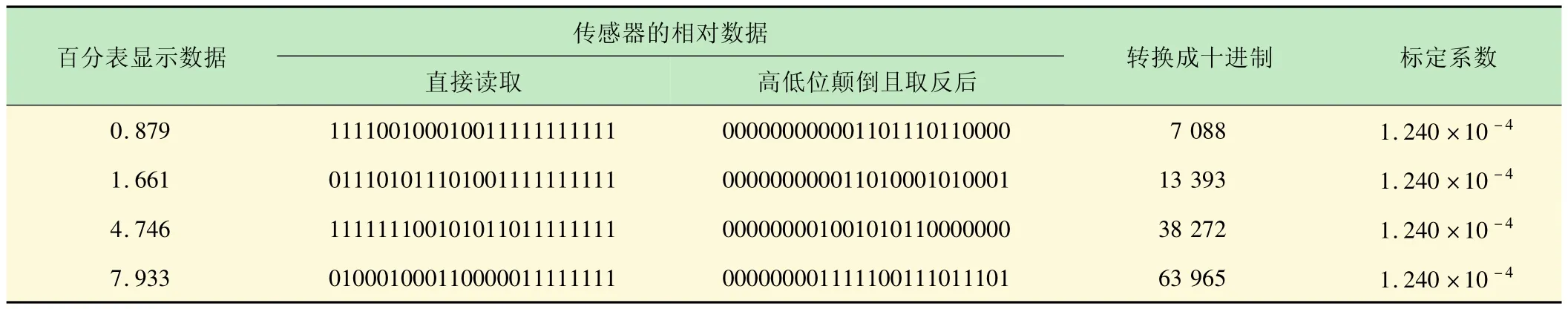

由表1、2可以看出,正数标定的系数为非常数;而负数的标定系数为常数。进一步观察可以发现,传感器输出的相对数据为正数时,其二进制最高位都是“1”,负数的最高位都是“0”,如果给正数二进制取反,那么就会得到表3中的数据。

取反后可发现,正数标定的系数为常数。标定系数是用数显表显示的值除以传感器正数的相对数据取反后的值(负数直接读取的相对数据)。在后续的软件编程时将数显表的实际值扩大1 000倍变成整数,即将标定系数扩大1 000倍定为0.124,这样便于数据处理显示时数据的拆分。在数据采集编程时,首先判断完读取的数据的正负号(最高位为1是正号,最高位为0是负号)后,再选择是否需要取反,再经过单片机对采集数据处理,最后就可直接显示采集数据的正负及大小。

表1 直接读取的传感器的相对数据(正数)

表2 直接读取的传感器的相对数据(负数)

表3 对正数的相对数据取反后的数据

3 传统测量系统硬件方案的论证

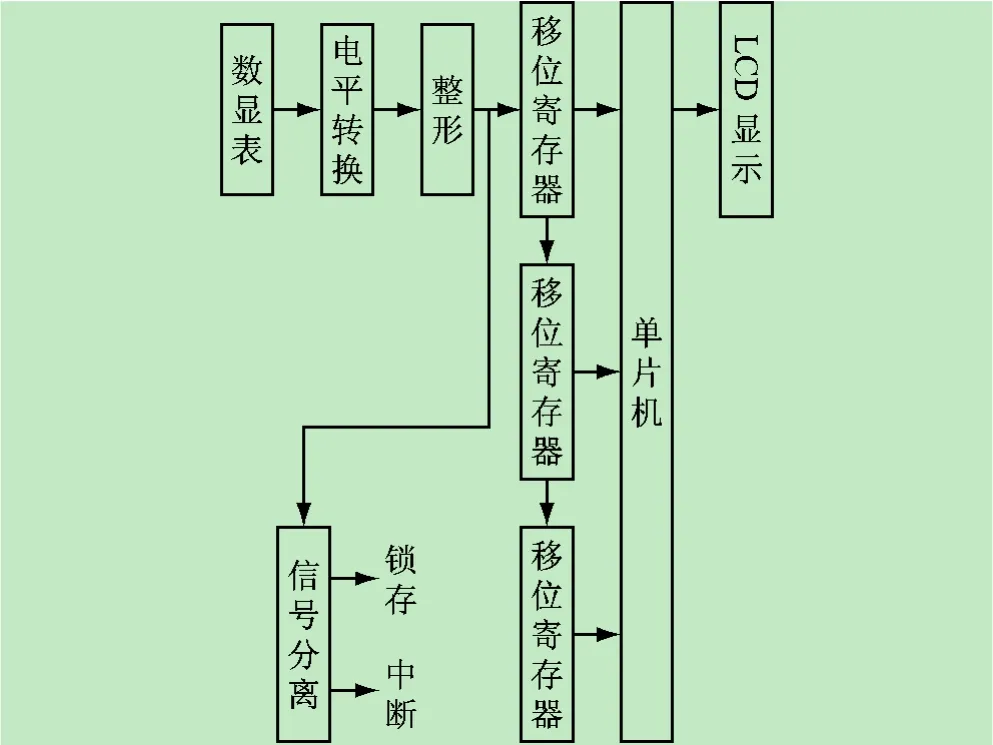

图2为现有文献报道的测量系统方案。它由3片8位移位寄存器接收24位数据信号,通过片选控制分3次读入结果,为了准确无误地读取信号,必须使单片机在进入第2组数据时就产生中断读取数据。为了告诉单片机锁存完毕进行正确的读取还须分离出锁存信号。系统通过中断的方式对容栅式传感器数据信号进行分组,它由单稳态触发器产生的外部中断进行控制,当产生中断后就读取单片机I/O口的数据;当串行数据经移位寄存器转化为并行数据后经锁存器锁存,这时所有的24 bit可以全部通过单片机的某一I/O口,然而单片机只有8 bit口,系统则用片选法来控制数据的读入,单片机的另一I/O口分别与3片锁存器相连,在读取数据时选通相应的锁存芯片[7-9]。这种方案无疑是可行的,然而大部分工作靠硬件完成,没有充分利用软件的功能,测量系统硬件组成相对复杂,硬件成本较高。

图2 传统方案框图

4 改进后测量系统硬件方案的论证及择优

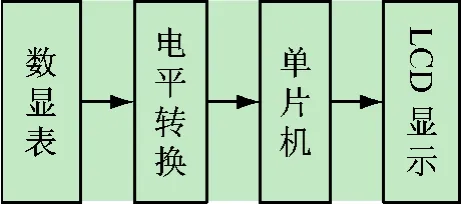

4.1 方案一

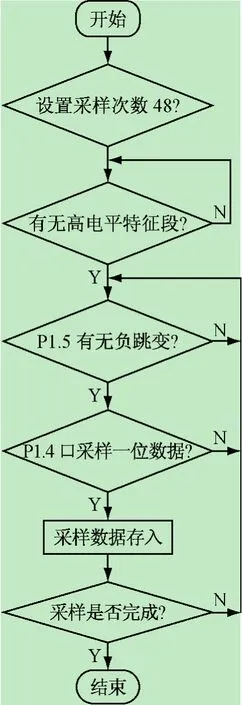

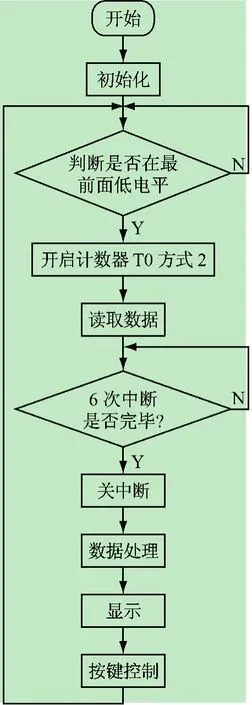

方案一框图如图3所示,将从传感器出来的信号(CLK和Data)进行电平转换后,分别送入单片机的2个I/O(假如CLK 接 P1.5,Data接 P1.4)。数据采集程序要解决的主要问题是确定数据采集的起始条件。根据图1可知,容栅芯片在CLK信号窄脉冲的下降沿对Date信号进行采样,CLK信号每次负跳变一次,即可采样一位Date信号数字脉冲,共48次就可先后将两组24位绝对数据数据和相对数据全部采样完毕。计算时只采用后24位数据。在编程时要充分考虑指令执行的时间不能超过时钟脉冲的周期间隔,故该部分程序拟采用汇编语言编程,以便保证数据采集的正确性。其他电平转换电路部分及显示部分软硬件设计和采集数据处理子程序设计与下述方案二相同,在此暂不做叙述。采样程序流程图如图4所示。

图3 方案一框图

该方案的优点是硬件电路少,比较直观地体现信号的采集路径及过程,经济性能高,但缺点是软件控制数据传送速度较慢,占用的检测时间长,不如硬件电路的实时性好,且采集数据处理较麻烦。

4.2 方案二

方案二框图如图5所示,用1片移位寄存器来进行数据的传输,省掉了传统方案中两片移位寄存器和信号分离电路,并结合软件功能使硬件电路更为简单,降低硬件成本的同时,仍能确保系统运行的可靠性。

采用一个8位移位寄存器成功与否在于软件的正确编制,这里要解决好:① 怎样确定要读的数据组;②怎样控制每次移入8位就读取一次,若能控制好,显然3次读取就能采集24 bit完整信息。解决第一个问题的办法是将CLK信号同时送移位寄存器和单片机的计数通道,检测到一段持续的低电平就启动计数器,计满24个脉冲后就准备读取P1口的后24位数值。解决好第一个问题,第二个问题就好解决了,将计数器置成连续装载值为8的工作方式,每计数8个CLK脉冲就读取一次数据,在这里只要保证在下一个脉冲到来之前的13μs内取走数据就能保证读数正确。

图4 数据采样程序流程图

图5 方案二框图

5 测量系统硬件原理

5.1 信号转换部分

将数显百分表输出的CLK(1.5 V)和Date(1.5 V)信号接入 LM393双电压比较器[10]。当 CLK或Date信号是高电平时(1.5 V),它大于比较器的参考电压(1 V),比较器就输出一个5 V高电平信号(因为比较器的电源电压是5 V);当CLK或Date是低电平时(0 V),小于比较器的参考电压(1 V),则比较器就输出一个0 V低电平信号。

5.2 串/并转换部分及数据采集实施办法

传感器的Data信号是一个串行信号,在此先把这个信号输入到一个串入并出带锁存的移位寄存器(74HC595)里。由于一个完整的数据是24 bit的,我们用一个8 bit的串入并出移位寄存器向单片机并行口P1进行传输一次读进来8 bit,并进行锁存则不影响后面数据的移位,这样单片机读3次就将24 bit读完,既避免了硬件电路的繁琐和纯采用软件编程实时性差的缺点。

5.3 显示部分

单片机应用系统最常用的显示器是发光二极管显示器(LED)和液晶显示器(LCD),可显示数字、字符及系统的状态。由于LED显示信息量少,形式比较单一,人机交互性差,而LCD液晶显示内含有控制驱动器,使得它和单片机的接口电路实现比较简单,还具有功耗低、体积小、质量轻,超薄和可编程驱动等其他显示方式无法比拟的优点,故本系统选用1602液晶显示屏。

6 系统软件设计

6.1 主程序

主程序流程图如图6所示。结合图1阐述数据采集的具体的实施过程为:首先完成系统的初始化[11-15],其次将经电平转换后的CLK信号接到单片机的P3.5来检测CLK电平的变化,当连续检测到低电平时就用P3.4口进行外部脉冲计数中断。在此用定时器/计数器0,并将其设定为自动装载的方式2进行计数,每计数到8中断一次。由于前24为绝对数据是不需要的,可以让单片机接收但不用读出,当前24 bit数据传输完(前3次中断完),后面每次中断接收到的数据再读出,三次中断就可以将全部24位相对数据读出了。最后采集数据经过单片机处理后将测量结果显示在LCD液晶显示屏上。

6.2 中断子程序

中断子程序流程图如图7所示。当定时器/计数器计满8个时钟脉冲时就中断,这时就将进入移位寄存器的8位数据锁存,锁存器工作时需要提供一个上升沿锁存时钟才能进行锁存,所以就用软件给P3.0一个上升沿控制移位寄存器锁存并行输出到P1口,然后读取P1口并将读完之后的数据另存,以防止后一组数据覆盖,当3组数据存储完毕后就关闭中断。

6.3 数据处理子程序

数据处理子程序流程图如图8所示。在读取完之后就进行数据处理,先判断采集到数据的正负,最高位若为1(正数)则先取反再进行合并;若为0(负数)就直接合并,最后将合并后的数据进行标定然后拆分出各位。

6.4 显示子程序

图6 主程序流程图

图7 中断程序流程图

图8 数据处理子程序流程图

常用的数据显示程序编程较为经典,利用单片机C语言可移植性好的特点,可对其稍加更改直接移植到应用程序当中。

7 硬件设计时注意问题

CLK信号经过比较器后同时送移位寄存器和单片机的计数通道,目的在于移位寄存器能在CLK时钟控制下进行正确的移位,并在每次中断后给P3.0口一个上升沿的脉冲作为74HC595的锁存时钟,从而将串行信号转换成并行信号进入单片机;为了让单片机能直接运算,将74HC595的输出端的高位(Q7~Q0)接到单片机P1口的低位上(P1.0~ P1.7),避免高低位颠倒,简化数据处理软件流程。

8 结语

借助数字示波器分析数显百分表输出信号与其显示数据之间的关系,有助于对容栅式传感器原理的理解和软件编程;合理选择相关硬件搭建电路可有效地保证系统运行稳定性的同时降低成本。文中介绍的数据采集检测系统是我校机械学院研究生综合实验教学内容的一部分,通过该实验的开设大大提高了学生综合应用能力和创新精神的培养。目前该测量系统也初步应用于省教育厅科研项目下位机数据采集系统试验当中。

[1] 王煜东.传感器应用技术[M].西安:电子科技大学出版社,2006:100-102.

[2] 徐科军.容栅传感器的研究与应用[M].北京:清华大学出版社,1995:6-10.

[3] 王习文,齐 欣,宋玉泉.容栅传感器及其发展前景[J].吉林大学学报(工学版),2003,33(2):89-94.

[4] 杨雪芳,蔡 萍,王卫钢,等.全数字式容栅位移传感器[J].仪表技术与传感器,2005(7):5-6.

[5] Dwight Larson.用于辅助电路分析的示波器数学功能[J].电子设计技术,2012,19(7):40-40,42,44.

[6] 胥京宇.泰克推出专为教育行业而设计的示波器[J].世界电子元器件,2012(5):69-69.

[7] 李佳列,丁国清,颜国正,等.多路电子数显百分表测量系统的研制[J].仪表技术,2002(1):23-24,26.

[8] 王安敏,王辛立,崔 伟.基于AT89C52单片机的容栅传感器测距系统[J].仪表技术与传感器,2008(9):86-90.

[9] 王辉林,李莎莎.基于LabVIEW的数显百分表测量系统[J].计量技术,2008(6):37-39.

[10] 张国雄.测控电路[M].3版.北京:机械工业出版社,2008:40-78.

[11] 孙永泉,王振清.基于容栅传感器和单片机的变形检测系统[J].微计算机信息,2007,23(12-2):103-104.

[12] 陆 雯,王道波.容栅传感器及其在目标运动转台中的应用[J].计算机仿真,2005,22(8):250-252.

[13] 邬玉亭,李 勇.电容式数显内径测微仪[J].工具技术,1995,29(6):46-48.

[14] 胡 超,王 耀.鉴相式位移传感器的计算机检测[J].宁波大学学报,1996,9(1):27-28.

[15] 凌锐鸿 王 佶.容栅角度测量装置的精度分析[J].工具技术,1996,30(4):24-27.