基于FPGA的脉冲压缩雷达目标模拟器设计❋

2013-06-27刘敬兴叶春令王华

刘敬兴❋❋,叶春令,王华

(国营8450厂,福建三明365001)

基于FPGA的脉冲压缩雷达目标模拟器设计❋

刘敬兴❋❋,叶春令,王华

(国营8450厂,福建三明365001)

目标模拟器在雷达的研制生产过程中具有重要的意义,不仅能加快项目开发进度,还能降低研制和实验费用。介绍的模拟器主要是针对脉冲压缩雷达而设计,该模拟器通过对雷达回波中频信号模拟,利用FPGA技术实现,具有设计简单、使用方便、成本低等特点。首先根据系统要求建立了二相码脉冲压缩雷达目标回波信号的数学模型,利用辛克函数模拟雷达天线扫描状态;然后给出了基于FPGA的设计解决方案以及主要模块的实现方法;最后给出了设计可行的结论,同时指出了今后将改进的地方。

脉冲压缩雷达;雷达回波;中频信号;目标模拟器

1 引言

雷达目标模拟器不仅能完成雷达系统调试与测试,还能缩短项目开发周期以及减少项目的现场实验费用,是雷达相关项目开发过程中的重要手段之一。对雷达目标回波模拟是信号处理技术和雷达技术相结合的产物,它一般包含目标信息模拟与信号环境模拟,按照所模拟的信号,目标模拟器可划分为射频信号模拟器、中频信号模拟器、视频信号模拟器等。目前,大部分模拟器采用直接数字波形合成(Direct Digit Wave Synthesize,DDWS)方法设计[1-2],其采用波形存储直读方式能产生任意波形,但是波形数据修改麻烦,不能任意调节噪声、目标等信号的参数。本文设计的是中频信号模拟器,该模拟器采用DDWS与模拟技术相结合,利用FPGA并行处理能力,能够产生任意的目标回波、噪声信号以及模拟雷达天线扫描方式,还可以单独随意调节目标回波、噪声信号和雷达天线扫描方式等参数,具有使用简单灵活、成本低、能够较好地模拟现场等特点。

2 脉冲压缩雷达回波模型建立

本节推导了雷达定点监视和雷达天线扫描两种工作状态下目标回波的数学模型,为目标模拟器的设计提供理论依据。

2.1 理想回波

对于窄带雷达的“点”目标,不考虑噪声、天线扫描等影响时,其零中频理想回波信号可表示为[3]

式中,α(t)表示相位调制后回波信号的幅度函数,θ(t)表示回波信号的相位函数,exp(·)表示信号的复数函数。该回波只含有调制的中频信号以及目标的多谱勒频移,其发射的高频成分已经被滤除。

(1)θ(t)函数

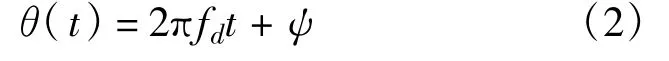

相位函数主要是受目标多谱勒频率以及初始相位决定,其表达式为

式中,fd为动目标的多普勒频移(当为固定目标时,fd取值为0),ψ为初相。

(2)α(t)函数

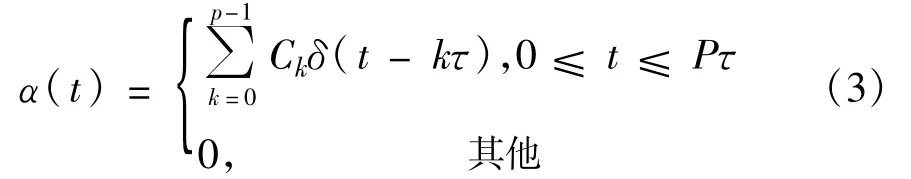

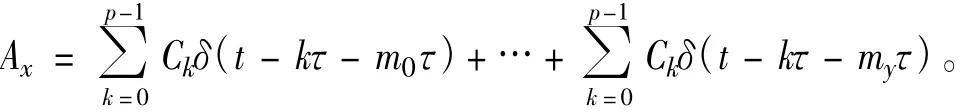

本文主要讨论相位编码雷达的回波信号,若不考虑雷达天线扫描因素影响,目标回波幅度主要受编码相位调制。当雷达固定发射P位二相编码时,接收的理想回波信号可表示为[4]

式中,δ(t)为单位冲激函数,τ为子脉冲宽度,P为码元个数,kτ为编码持续周期,Ck为特定的二进制编码序列{Ck=1,-1}。

2.2 噪声信号

本文设计的噪声信号采用[0,1]上均匀分布的随机高斯白噪声n(t),其幅度大小An,则噪声函数表示为

2.3 雷达定点监视时目标回波

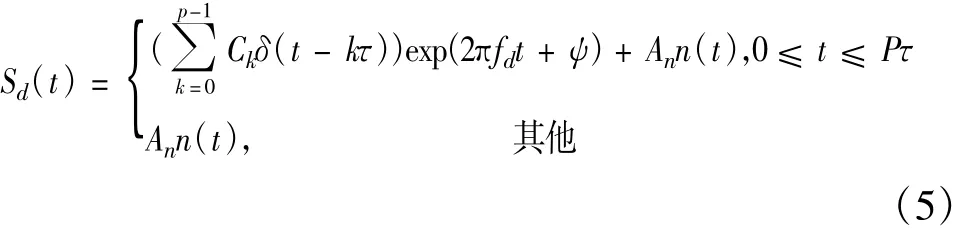

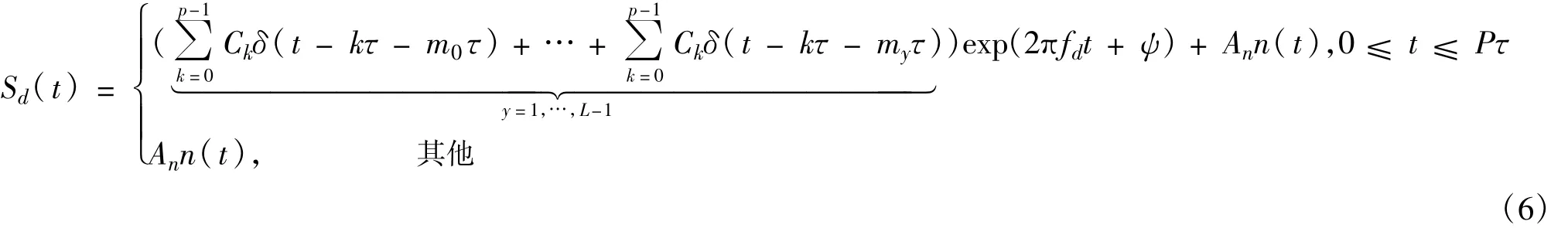

当雷达工作在定点监视状态时,理想目标回波叠加了噪声信号,雷达定点监视时天线不扫描,则不考虑天线波束的影响,根据噪声的随机性结合式(1)~(4)可得单个目标,信号回波的函数表达式为

式(5)中描述的是只存在单个目标的情况,而实际环境一般都存在多个目标,假设在多个距离门(如L个)存在目标,此时,根据式(5)可推导出其函数表达式为

如式(6),L个目标同时存在时的目标回波信号Sd(t),myτ表示第y个目标相对0时刻的延迟时间,y的取值范围为[1,L-1]的整数。

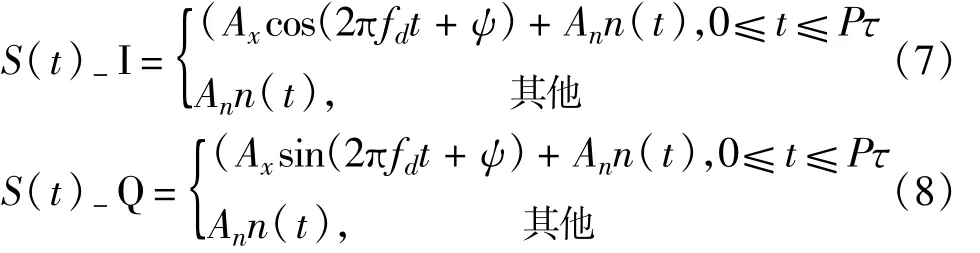

对式(6)通过I、Q正交解调后,得I、Q分量信号,其中I分量和Q分量函数表达式分别为

2.4 雷达天线扫描时目标回波

(1)天线波束方向信号

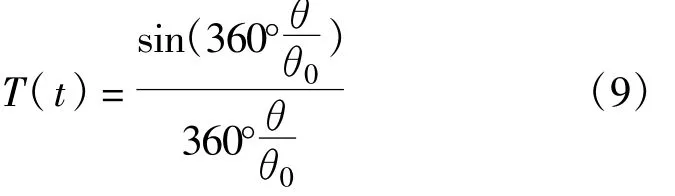

雷达天线按一定角速度扫描时,其波束方向可通过天线方向性图描述,其包络函数可用辛克函数近似表示[5]:

其中:

其中,θ0为零功率波束宽度,θ表示天线的方向角度。

(2)雷达天线扫描时目标回波

雷达天线扫描运动时,回波信号受波束方向信号调制,根据式(7)~(9),其函数表达式可表示为

3 系统设计实现

3.1 系统原理框图

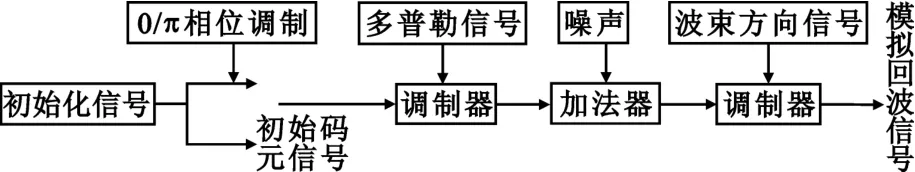

根据理论推导(10),采用如图1所示的原理框图实现该目标器系统,首先按照脉冲重复周期,根据给定的二相编码码元(Ck)调制初始化信号产生宽带初始码元信号,然后利用目标多谱勒信号进行调制,对调制信号叠加随机噪声,最后利用波束方向信号调制后输出作为模拟的目标回波信号。初始化信号为单个目标的最大幅度;多普勒信号是I、Q正交的正弦波;噪声是利用24位m序列伪随机码产生的伪随机噪声;波束方向信号根据设计的天线方向函数生成并通过DDWS方法实现。

图1 系统框图Fig.1 System block diagram

3.2 硬件电路设计

该目标模拟器采用FPGA作为核心处理与控制芯片,充分发挥FPGA芯片的并行处理能力。该目标模拟器采用型号为EP2C35的FPGA芯片实现,把多个功能模块整合在EP2C35芯片内,减少了外围电路的复杂程度,降低了设计难度,同时也提高了系统灵活性。FPGA内部主要包含噪声模块、I、Q正交模块、初始码元模块、波束指向模块、译码模块和控制模块,具体见图2。

图2 硬件电路框图Fig.2 Hardware circuit diagram

该系统所需要的外部信号极少,只需要雷达数字信号处理机给出一个触发信号以及同步时钟。其工作原理如下:

FPGA在同步时钟控制下工作,当收到触发信号后,控制模块根据预先设计的指令同时控制噪声模块、I、Q正交模块、初始码元模块、波束指向模块并行工作,生成相应的数据,并按照预定的周期和时序控制数据的输出,同时实时接收译码模块数据改变系统工作状态。

初始码元模块根据二相码码元Ck产生目标回波的数字编码信息,通过D/A(AD9765)转换成模拟信号得到初始码元信号;I、Q正交模块产生I、Q正交数据,通过D/A(AD7547)转换成模拟信号得到I、Q两路多普勒信号;波束指向模块根据式(9)生成数据,通过D/A(DA0803)转换成模拟信号得到波束方向信号;噪声模块产生的伪随机噪声通过调理、滤波后获得所需带宽内的噪声信号。译码模块主要是对键盘指令译码并向控制模块传送指令实现系统工作状态的更改。

调制器1和调制器2利用初始码元信号作为载波和I、Q多普勒信号进行调制并滤波得到I、Q两路中频信号,该信号与噪声信号相加后分别通过调制器3、调制器4和波束方向信号调制,最后通过滤波器完成低通滤波获得两路回波I、Q信号。

3.3 关键电路模块实现

3.3.1 信号调制器

从图2中可以知道,回波的幅度被天线方向图以及编码调制,相位被目标的多谱勒频率调制,因此在该系统中调制器的设计尤为关键。具体硬件电路采用MC1596芯片完成,设计的信号调制器的主要指标要求见表1。

表1 信号调制器主要技术指标Table 1 The main technical indicators of the sig nal modulator

3.3.2 多普勒I、Q信号的产生

I、Q信号由FPGA控制AD9765产生。AD7547是双路12 b并口数模转换器,控制逻辑和时序简单,首先利用计算机生成256点sinθ和cosθ数据,采用2 048进行量化取整,然后把量化后的sinθ和cosθ数据存储在FPGA的ROM中,并且按照AD7547的控制时序把ROM中数据输出至AD7547完成模数转换,信号低通滤波后得到I、Q正交正弦信号。由于数据输出至AD7547的间隔周期决定了产生正弦信号的周期(或频率),所以需要根据系统对正弦波频率的要求计算EP2C35输出数据的内部控制时钟频率。

3.3.3 码元信号产生

码元信号由FPGA控制AD9765产生。AD9765是12 b并口高速数模转换器,控制简单易于实现。先把二相码序列存储在ROM中,根据要求的模拟目标数以及目标位置计算初始码元信号,然后利用FPGA按照AD9765的控制时序把码元信号数据输出,最后对AD9765输出的模拟信号滤波后获得所需要的初始码元信号u(t)。产生初始码元信号的步骤如下。

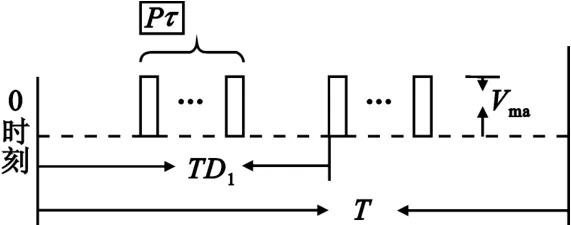

步骤2:根据系统要求的最多目标个数计算出码元幅度数值(Vma)。

图3为初始码元信号波形示意图,P表示码元个数,T为脉冲重复周期,其值表示码元信号的幅度,存在多(i)个目标的回波信号时,所有目标回波有可能存在重叠部分,为了确保信号累加时不溢出,必须表示取整)。

图3 初始码元信号波形示意图Fig.3 Initial symbol signal waveform diagram

步骤3:根据系统要求的最多目标个数以及各个目标所处的距离,设计各个目标码元信号相对0时刻的延迟时间。

图4为初始码元模块框图,初始码元模块中的TD控制器接收到外部指令后,首先进行逻辑运算,然后根据运算结果控制相应目标的延迟时间以及控制相应选通开关打开(默认为关断状态),被选通的目标信号进入累加器完成求和运算,产生如图3所示的初始码元信号,最后由控制模块按照AD9765特定的时序输出信号。外部指令由控制模块发出其主要内容包含需要产生几个目标以及各个目标的相对距离(延迟时间),图4中目标1至目标i模块完全一致,都是存在一个延迟时间(TD)为0的二相编码信号,为方便目标模拟仿真,一般情况下延迟时间取码元宽度τ的整数倍。

3.3.4 波束方向信号

根据式(9)计算天线方向函数波形数据,存储在FPGA的ROM中,按照固定的周期和时序输出至DA0803,经过滤波、放大等处理后获得波束方向信号。

3.3.5 噪声信号

本系统要求的噪声信号利用随机伪噪声技术产生。随机伪噪声信号的产生根据x24+x7+x2+1多项式(24位本原多项式),通过FPGA硬件实现,然后对产生的伪噪声编码信号进行低通滤波则获得所需的噪声信号。

4 实验结果分析

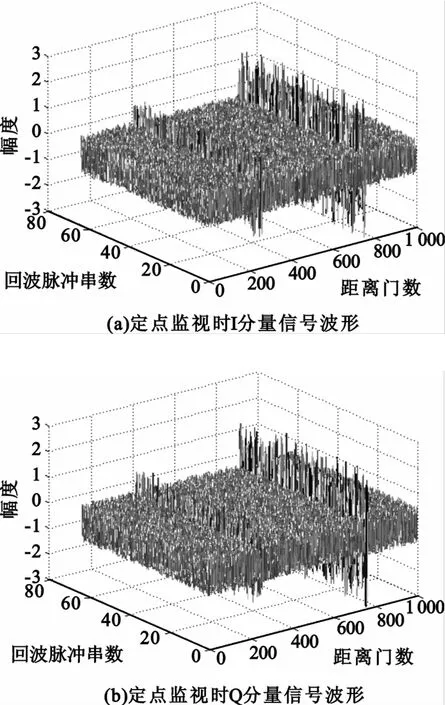

实验条件设置如下:脉冲重复周期200μs,子脉冲宽度0.2μs;二相编码Ck采用13位巴克码(1,1,1,1,1,-1,-1,1,1,-1,1,-1,1);一个固定目标的位置在50μs(第250个距离门)处,信号增益为1;一个动目标的位置在150μs(第750个距离门)处,信号增益为2;多普勒频率为1 500 Hz;回波脉冲串数为64,雷达定点监视时I、Q分量信号波形如图5所示。

图5 定点监视时目标回波图Fig.5 Sentinel surveillance target echo

当天线的零功率波速宽度θ0为30°,雷达天线扫描状态时I、Q路信号波形如图6所示。

图6 天线扫描时目标回波图Fig.6 Antenna scan target echo

从图6中容易看出在雷达天线扫描过程中,当天线对准目标时,产生目标回波信号,在其他方位仅存在噪声信号,这与实际情况相符。

5 结论

该系统为雷达中频信号模拟提供了一个很好的解决方案,设计的目标模拟器已经在某型号脉冲压缩雷达研制过程中使用,为雷达系统的信号处理机验证动目标检测、多目标干扰、目标方位点迹凝聚等算法提供了支持。该目标模拟器也还存在一些缺点:模拟目标的最多个数需要在设计时确定,在运行过程中不能更改,需要重新编写FPGA内部的程序实现,这将在今后进一步改进,能够不限制目标个数(资源满足的情况下)利用算法自动完成初始码元信号生成。

[1]向道朴,黎向阳,孟宪海.一种通用雷达回波模拟器的设计与实现[J].现代雷达,2007,29(10):84-86. XIANG Dao-pu,LI Xiang-yang,MENG Xian-hai.Design and Implementation of a General Digital Radar Echo Simulator[J].Modern Radar,2007,29(10):84-86.(in Chinese)

[2]熊兴中,汪学刚.基于USB2.0协议的雷达回波模拟器设计[J].现代雷达,2006,28(11):48-50. XIONG Xing-zhong,WANG Xue-gang.Design of Radar System Simulation Based on USB2.0 Protocol[J].Modern Radar,2006,28(11):48-50.(in Chinese)

[3]林茂庸.雷达信号理论[M].北京:国防工业出版社,1981:94-95. LIN Mao-yong.Radar Signal Theory[M].Beijing:National Defense Industry Press,1981:94-95.(in Chinese)

[4]刘敬兴.地面探测脉冲压缩雷达的动目标检测[J].电子技术应用,2010,36(1):132-135. LIU Jing-xing.Moving target detection of ground-based pulse compression radar[J].Application of Electronic Technique,2010,36(1):132-135.(in Chinese)

[5]丁鹭飞,耿富录.雷达原理[M].3版.西安:西安电子科技大学出版社,2002:201. DING Lu-fei,GENG Fu-lu.Radar Principles[M].3rd ed. Xi′an:Xidian University Press,2002:201.(in Chinese)

LIU Jing-xing was born in Sanming,Fujian Province,in 1982.He is now a senior engineer.His research concerns ground surveillance radar,signal processing and embedded systems analysis,design.

Email:liujingxing523@163.com

叶春令(1962—),男,福建三明人,工程师,主要研究方向为地面雷达系统分析与光电结合系统总体设计;

YE Chun-ling was born in Sanming,Fujian Province,in 1962. He is now an engineer.His research concerns ground radar system analysis and photoelectric integration system design.

王华(1981—),女,陕西西安人,2004年获学士学位,现为工程师,主要研究方向为地面雷达伺服控制及电路设计。

W ANG Hua was born in Xi′an,Shaanxi Province,in 1981.She received the B.S.degree in 2004.She is now an engineer.Her research concerns ground radar servo control systems and circuit design.

Design of a Pulse-Compress Radar Target Simulator Based on FPGA

LIU Jing-xing,YE Chun-ling,WANG Hua

(State-owned No.8450 Factory,Sanming 365001,China)

A target simulator has great significance in development and production process of radar,for it can not only speed up the progress of the project development,but also reduce the cost of research and experiment.The simulator descriked in this paper is mainly designed for pulse-compress radars.Through radar echo IF signal simulation,the simulator is achieved by FPGA technology,which is featured by simple design,conveniency,low cost,etc.In this paper,firstly,according to system requirements,a mathematical model of the two-phase code PC radar target echo signal is established,and radar antenna scan-status is simulated by using SINC function;then,the design solution based on FPGA and the implementation method of the main module are given;finally,the conclusion that the design is feasible is given,at the same time,the improvements in the future are pointed out.

pulse-compress radar;radar echo;IF signal;target simulator

date:2013-04-08;Revised date:2013-07-10

❋❋通讯作者:liujingxing523@163.comCorresponding author:liujingxing523@163.com

TN955

A

1001-893X(2013)09-1238-05

刘敬兴(1982—),男,福建三明人,2004年获学士学位,现为高级工程师,主要研究方向为地面侦察雷达总体、信号处理和嵌入式系统分析、设计;

10.3969/j.issn.1001-893x.2013.09.023

2013-04-08;

2013-07-10