E-band通信系统中高速并行FIR成形滤波器设计❋

2013-06-27钟文斌周志刚王丽云李超

钟文斌❋❋,周志刚,王丽云,李超

(中国科学院上海微系统与信息技术研究所宽带无线技术实验室,上海200050)

E-band通信系统中高速并行FIR成形滤波器设计❋

钟文斌❋❋,周志刚,王丽云,李超

(中国科学院上海微系统与信息技术研究所宽带无线技术实验室,上海200050)

为实现E-band(E频段)通信系统中的高速成形滤波,在已有快速FIR滤波算法(FFA)基础上,通过快速短卷积迭代以及张量展开算法,设计了一种高速并行FIR成形滤波器,并进行硬件复杂度分析与时延分析。浮点和定点数仿真验证结果表明,所设计高速并行滤波器在硬件实现上可减少21%的乘法运算操作和13.4%的时延单元,6比特以上小数量化可达到系统成形滤波需求。

E-band通信系统;并行FIR结构;成形滤波;短卷积迭代;定点仿真

1 引言

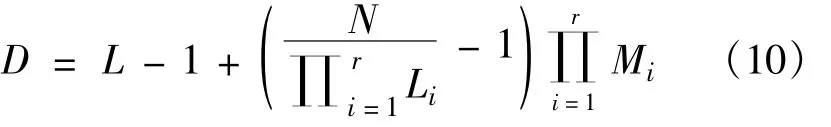

E-band通信系统工作在80 GHz频段,传输速率可达Gb/s以上,是未来通信系统无线回传的主要解决方案之一[1-2]。高速无线传输系统对发送信号的频谱提出了较高的要求。对于采用数字中频技术的多通道E-band系统,由于信号带宽较宽,而数字中频频率相对较低,故需要高效的成形滤波对信号频谱进行修正。

考虑传输速率为10 Gb/s的E-band通信系统,采用16QAM调制以及双通道数字中频架构时,需2.5 Gsample/s的信号处理速率。而目前主流的FPGA中DSP核的最高处理速度约为550 Msample/s,故串行滤波结构无法满足应用需求。采用高速并行成形滤波器结构可在较低的硬件复杂度情况下提高滤波器吞吐量。

文献[3]中提出了以短卷积算法为基础的并行滤波结构,而文献[4]则采用多相分解的方法引出了目前最常用的快速FIR滤波算法(FFA)。这两个算法的缺点在于所需的延时单元随并行程度而大大增加。文献[5]中基于快速线性卷积算法实现了快速块滤波算法,然而由于预加矩阵非常复杂,导致所需的加法器和乘法器数量大大增加,不利于硬件实现。同样的问题也存在于通过Cook-Toom算法和Winograd算法[6]导出的快速卷积算法,在问题规模较大时无法适应硬件实现的限制。文献[6-9]基于张量分解的方法和流水线技术,给出了并行滤波器带来的一系列性能分析,但缺乏对实际系统的滤波器性能分析。文献[10-11]虽然对滤波器硬件实现做出较大简化,然而对滤波器阶数和系数的对称性要求较高。本文将针对E-band通信系统,设计可通过迭代实现的高速并行成形滤波器,并从实现复杂度、滤波器特性、量化误差分析等方面验证滤波器性能及其实用性。本文第2节描述了E-band通信系统中的成形滤波器,在此基础上在第3节设计了基于快速短卷积迭代算法的高速并行滤波器,在第4节详细分析了其复杂度,并进行仿真验证。

2 E-band通信系统中成形滤波器

2.1 根升余弦滚降滤波器

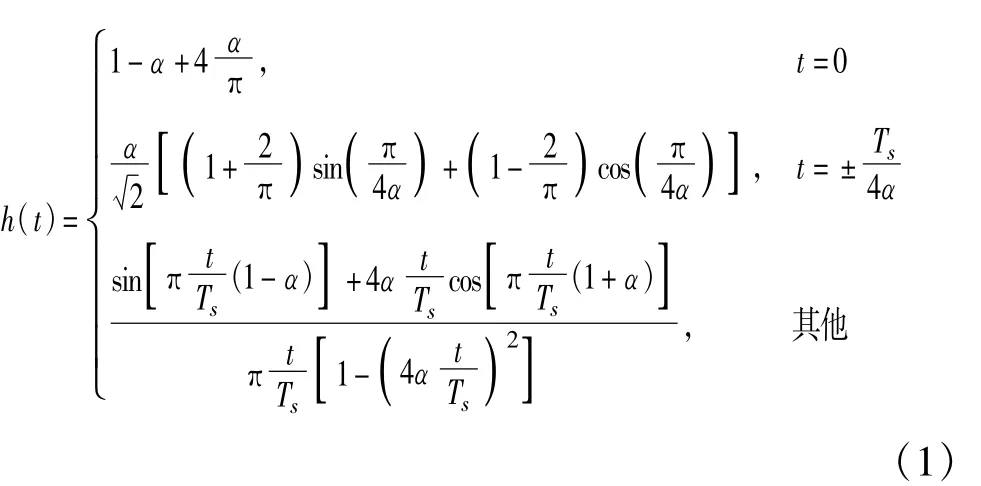

E-band通信系统中应用了根升余弦滚降滤波器(Root Raised-Cosine filter,RRC),用于收发两端成形滤波。RRC的冲激响应可表示为

该滤波器性能取决于两个参数:滚降系数α和符号周期Ts,其中滚降系数为[0,1]的实数,符号周期为符号速率的倒数(Ts=1/Rs)。RRC滤波器在±Ts处仅当α=0时为0,但就整个收发端传输系统传输函数而言,在±Ts处为0,符合奈奎斯特无ISI(Inter-Symbol Interference)传输准则。

本文所研究的E-band通信系统采用65阶RRC滤波器,实际速率为3.75 Gsample/s,滚降系数为α=0.4,重点考虑其高速并行实现结构的设计。

2.2 短卷积迭代算法

FIR滤波器是通过卷积实现的。根据多相分解的原理,长卷积可以被分解为若干短卷积。如果利用快速卷积算法对这些短卷积进行实现,再进行迭代,即得到长卷积的快速实现算法[6]。本文采用的是文献[7]中基于张量积的卷积展开方法。

N阶FIR滤波器可以用多项式表示为

其中,H(z)为滤波器系数多项式,X(z)、Y(z)分别为输入和输出多项式。

将多项式进行分解,可表示为式(3)所示矩阵形式,记为Y=HX。串行的FIR滤波器可以由L路并行结构实现。

其中,xi、yi为输入输出序列,hi为FIR滤波器系数。子滤波器的阶数随并行数增加而降低。

这种并行结构能够增加吞吐量并减小系统总延时,然而其硬件复杂度会随着并行程度呈线性增长,在E-band高速通信系统中不适用。

短卷积可用快速卷积算法实现。快速卷积算法可统一表示为Sn=QnHnPnXn,由此形成的滤波器可表示为Yn=QnHnPnXn。其中,P称为预加矩阵(Pre-addition Matrix),Q称为后加矩阵(Post-addition Matrix),它们主要决定了算法中需要计算的加法和延时模块数量。H是子滤波器矩阵,表示为Hn=diag[Pn×[h0,h1,…,hn-1]T],是对角阵,它主要决定了算法需要的乘法操作数。不同的快速卷积算法主要对上述矩阵进行不同的优化,以降低系统硬件实现复杂度。

2.3 降低复杂度的快速短卷积迭代算法

在以上快速卷积算法的基础上,用张量展开[7]的方法对两个短卷积进行迭代,可得M×M(其中M=mn)卷积的表达式:

其中,⊗为张量积(Tensor Product)符号。该结果可推广到任意长度的L×L(L=L1L2…Lr)卷积:

利用这种卷积算法实现FIR滤波器,各子滤波器的迭代实现过程可以共享加法和延时操作,从而获得硬件实现上复杂度较低的结构。

虽然传统的FFA也能用张量积形式展开[4],然而由于没有规范化输入矩阵A的存在,导致其P、Q矩阵中包含大量延时模块,当并行数较多时,系统吞吐量会随之降低。另外,其系数往往不易进行二进制量化,故不利于硬件实现。而式(5)所述的迭代卷积算法,其P、Q矩阵中元素可以优化为只含0和±1的矩阵,大大降低了实现复杂度。

3 基于快速短卷积算法高速并行滤波

任意并行FIR滤波器可以通过转置变换转化为其等效转置形式[2]。通常情况下两种滤波器结构的硬件复杂度相当,但会具有不同的有限字长效应,这就影响了滤波器的精度。在实际应用中,往往需要考虑FIR滤波器的转置形式。文献[4]中已证明转置形式的滤波器结构具有较好的有限字长效应。

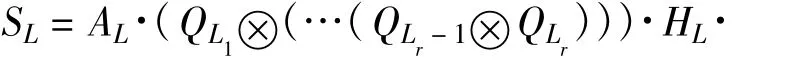

对上节中的Y=HX进行转置变换,可得到滤波器的一种等效并行实现形式:YF=HTXF。根据式(5)的快速卷积算法,可由线性卷积导出并行滤波算法:Y=ALQLHPLX。再进行转置变换,可得等效形式的并行滤波算法:

其中:

对于本文设计的E-band系统中的65阶RRC滤波器,可采用8路并行结构实现。考虑到对输入信号进行过采样,实际滤波器采用32路并行实现,即L=32。结构实现框图如图1所示,共需采用243个三阶子滤波器进行并行滤波。

图1 复杂度降低的迭代快速卷积滤波器Fig.1 Complexity reduced iterated parallel FIR filter

这种情况下对L=32进行分解和迭代,有3种可行方案,由于迭代顺序的差别,不同方案将导致不同的系统复杂度。具体的硬件实现复杂度性能分析在下节中详细阐述。根据分析结果,本文所述的滤波器的最优分解方案为L=4×2×4,即将滤波系统分解为3个子滤波过程进行迭代实现。

4 硬件复杂度分析与性能仿真验证

在可编程硬件实现中,乘法操作被称为强操作,而加法和延时操作则被称为弱操作,前者比后者需要更多的硬件资源和处理时间。对于高速的E-band通信系统的成形滤波器,应尽量减少强操作数,并将弱操作数控制在可接受范围内。

4.1 硬件复杂度分析

4.1.1 乘法运算

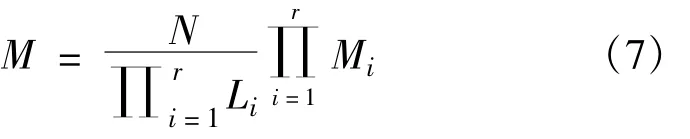

上述并行滤波器所需要计算的乘法数量由式(6)中子滤波器对角阵HL决定,所需要的乘法操作数M可由下式计算:

其中,r为分解成的子滤波过程数,Mi为子滤波过程i所需的乘法数,N为原始滤波器的阶数,Li为分解后子滤波过程的并行路数。

取N=65、L=32、L1=4、L2=2、L3=4,则本文中的高速并行滤波器所需乘法数为390。而对于普通FFA算法,则滤波器被分解为5个2路并行子滤波模块,所需的乘法数为493.6。在实际中,由于子滤波器的阶数为整数,实际需要乘法数分别为576和729,故本文算法比普通FFA减少21%的乘法操作数。

4.1.2 加法运算

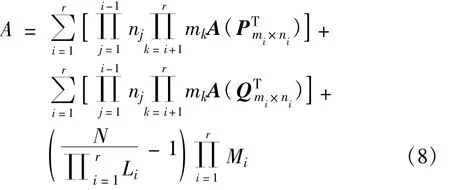

本文算法需要的加法数量取决于式(6)中的P、Q、A矩阵。矩阵A在实现上不需要加法运算,故只需考虑P、Q。算法所需要的加法数由下式给出[4]:

等式右边第一、二项分别为P矩阵和Q矩阵所需的加法数,第三项为子滤波过程所需的加法数。式中,m、n为矩阵的行列数,符号A(PTmi×ni)表示要实现PTmi×ni矩阵所需的最少加法数,A(QTmi×ni)同理。

由于矩阵P、Q行列数不相同,故采用不同的迭代顺序将使式(8)的取值发生变化。对于L=L1×L2×L3的分解方案,根据文献[5]中快速卷积算法对P、Q矩阵取值。当:

(1)L1=4、L2=4、L3=2时,所需加法操作A=1432;

(2)L1=4、L2=2、L3=4时,所需加法操作A=1340;

(3)L1=2、L2=4、L3=4时,所需加法操作A=2132。

因此,方案2所需的加法器数量最少。值得注意的是,分解迭代的顺序并不影响乘法器和延时单元的数量,而对加法数影响较大。

而当采用普通的基于FFA算法的高速并行滤波时,所需加法数为

计算的所需加法数为1 330,与上述算法基本相当。两种算法在所需加法器方面无明显差别。

4.1.3 延时单元

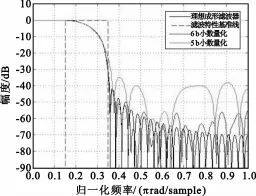

本文所采用高速并行滤波器中P、Q矩阵不含延时单元,3种分解方式在该性能上一致,所需的延时单元数量的表达式为

本文算法需要的延时单元数为415,而基于FFA的滤波算法则需要517个延时单元。在实际FPGA实现中,为了减小系统延时,往往需采用流水线技术[13]。在本文所述的算法中,可以在图1的Q矩阵后插入额外的延时单元,实现流水线设计。该算法与FFA都需要额外的243个延时单元来实现,故前者节省了13.4%延时单元。

4.1.4 时延分析

滤波器时延由滤波器实现时的关键路径[12]决定,且关键路径中乘法器的数量起决定性因素。设TM为乘法器时延,TA为加法器时延,则直接实现的FIR滤波器关键路径时延为TM+64TA。而本文滤波器在加入流水线后,关键路径为TM+16TA,与FFA一致。由于乘法器时延为主导因素,故两者的关键路径时延相差不大。但本文滤波器采用32路并行结构,实际总时延约为(TM+16TA)/32,吞吐量比前者大大增加。

硬件复杂度汇总如表1所示。对于65阶FIR成形滤波器的32路并行实现结构,采用本文所述的迭代快速滤波算法,由于对延时模块的位置做出调整,使得算法在几乎不增加加法操作的前提下,减少21%的乘法操作和13.4%的延时单元。

表1 高速并行滤波算法与FFA算法性能比较Table 1 Performances of high speed parallel alg orithm and FFA

4.2 高速并行滤波器滤波性能仿真

以下通过计算机仿真验证所设计的滤波器特性,调制方式为16QAM,其他仿真参数如表2所示。

表2 仿真参数Table 2 Simulation parameters

4.2.1 收发信号星座图

经过16QAM调制,发送信号的星座图如图2所示。

图2 发送信号(16QAM)星座图Fig.2 Transmitted constellation(16-QAM)

在信噪比为15 dB时,在经过理想串行成形滤波器后,星座图如图3所示,其误差向量幅度(EVM)为-18 dB(12.58%)。

在经过本文设计的滤波器成形后,接收信号星座图如图4所示。结果信号EVM仍为-18 dB(12.58%)。两种实现方式的滤波性能一致,但并行结构有更高的吞吐量且可节省硬件资源。

图4 并行滤波应用后接收信号星座图Fig.4 Received constellation with parallel shaping filter

4.2.2 定点与浮点仿真性能对比

采用正则有符号数对系统各参数进行量化[13]。

若采用6 b小数位量化,并用高速并行滤波结构实现,则可得图5的接收信号星座图。定点仿真星座图比浮点情况下离散度较高,说明定点运算引入了额外的系统噪声。定量计算可知其EVM值为-17 dB(14.12%),与浮点情况相比,有约1 dB的EVM损失。

图5 定点并行滤波成形后信号星座图Fig.5 Received constellation with fixed-point simulation

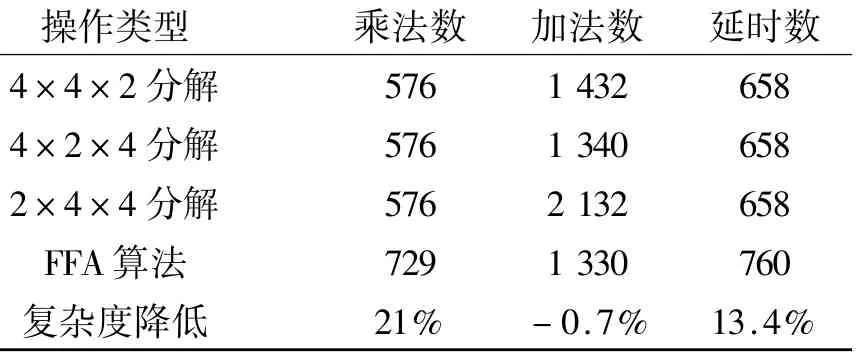

比特量化位数决定了硬件复杂度,同时也决定了接收信号EVM指标,这两方面性能是一对矛盾。将不同量化位数对应的接收信号EVM汇总如图6所示,当信道信噪比为15 dB时,小数位数大于6 b时,EVM损失小于1 dB,误符号率几乎不受影响。当信道信噪比为20 dB时,只需采用5 b以上量化,即可达到系统误符号率要求。实际系统中无线信道传输特性较复杂,因此在保证性能的情况下,在硬件实现时,小数位应采用6 b以上量化。

图6 不同小数量化位数接收信号对应的EVMFig.6 EVMs of received constellation in different quantization length

定点实现的并行滤波器幅频响应如图7所示。滤波器的截止频率为0.35,阻带衰减为32 dB,与理想串行滤波器基本保持一致。当采用低于5 b小数位数量化时,截止频率偏移至0.38,阻带衰减仅为23 dB,带外噪声大大增加。

图7 定点实现的滤波器幅频特性Fig.7 Magnitude of fixed-point shaping filters

5 结论

本文基于快速短卷积迭代算法,设计了一种适用于特定E-band通信系统的高速并行成形滤波器结构,并进行了性能分析与验证。该结构在滤波特性上与串行结构一致,与传统的FFA并行结构相比,硬件实现时能够节省21%的乘法操作和13.4%的延时单元,并减小了系统关键路径的时延,增加了系统的吞吐量。定点仿真和浮点仿真的结果基本保持一致,6 b小数位量化带来的EVM损失小于1 dB。所设计的滤波器结构对E-band等高速通信系统具有较强的适用性。进一步工作可针对特定高速系统参数对该滤波结构进行硬件实现。

[1]Claudio C,Massimo C.Next-Generation Access Network:A Wireless Network Using E-Band Radio Frequency(71-86GHz)to Provide Wideband Connectivity[J].Bell Labs Technical Journal,2011,16(1):187-206.

[2]Huang X,Guojay Y,Zhang A,et al.A Multi-Gigabit Microwave Backhaul[J].IEEE Communications Magazine,2012,50(3):122-129.

[3]Acha J I.Computational structures for fast implementation of L-path and L-block digital filters[J].IEEE Transactions on Circuits System,1989,36(6):805-812.

[4]Parhi K K.VLSI Digital Signal Processing Systems:Design and Implementation[M].New York:Wiley,1999.

[5]Lin I S,Mitra S K.Overlapped block digital filtering[J].IEEE Transactions on Circuits System II,1996,43(8):586-589.

[6]Cheng C,Parhi K K.Hardware Efficient Fast Parallel FIR Filter Structures Based on Iterated Short Convolution[J]. IEEE Transactions on Circuits System,2004,51(8):1492-1500.

[7]Cheng C,Parhi K K.Low-Cost Parallel FIR Filter Structures with 2-Stage Parallelism[J].IEEE Transactions on Circuits System,2007,54(2):280-290.

[8]Yu-Chi T,Ken C.Area-Efficient VLSI Implementation for Parallel Linear-Phase FIR Digital Filters of Odd Length Based on Fast FIR Algorithm[J].Transactions on Circuits System,2012,59(6):371-375.

[9]Richard C.Parallel FIR Filters Based on Modulo Arithmetic[C]//Proceedings of 2006 IET Irish Signals and Systems Conference.Dublin:IEEE,2006:167-172.

[10]Yu-Chi T,Ken C.Hardware-efficient VLSI Implementation for 3-parallel Linear-phase FIR Digital Filter of Odd Length[C]//Proceedings of 2012 International Symposium on Circuits and Systems.Seoul:IEEE,2012:998-1001.

[11]Yu-Chi T,Ken C.Area-Efficient VLSI Implementation for Parallel Linear-Phase FIR Digital Filters of Odd Length Based on Fast FIR Algorithm[J].IEEE Transactions on Circuits System,2012,59(6):371-375.

[12]Roger W,John M,Ying Y.FPGA-based Implementation of Signal Processing Systems[M].UK:Wiley,2008.

[13]张维良,张彧,杨再初,等.高速并行FIR滤波器的FPGA实现[J].系统工程与电子技术,2009,31(8):1819-1822. ZHANG Wei-liang,ZHANG Yi,YANG Zai-chu,et al.FPGA implementation of high speed parallel FIR filters[J]. System Engineering&Electronic,2009,31(8):1819-1822.(in Chinese)

ZHONG Wen-bin was born in Longyan,Fujian Province,in 1988.He received the B.S.degree from Shanghai Jiaotong University in 2011.He is now a graduate student.His research concerns broadband wireless technology and key technology for E-band communication systems.

Email:wenbin.zhong@mail.sim.ac.cn

周志刚(1974—),男,湖南长沙人,2005年于东南大学获博士学位,现为中科院微系统所副研究员、硕士生导师,主要从事未来无线通信系统物理层传输和媒体接入关键技术研究;

ZHOU Zhi-gang was born in Changsha,Hunan Province,in 1974.He received the Ph.D.degree from Southeast University in 2005.He is now an associate professor and also the instructor of graduate students.His research concerns PHY transmission and MAC technology for future wireless communication.

王丽云(1984—),女,山东人,2012年于复旦大学获博士学位,现为中科院微系统所助理研究员,主要从事宽带无线通信基带算法研究和工程实现;

WANG Li-yun was born in Shangdong Province,in 1984.She received the Ph.D.degree from Fudan University in 2012.She is now a research assistant.Her research concerns algorithm research and realization of broadband wireless communication.

李超(1989—),男,浙江衢州人,中科院微系统所硕士研究生,主要研究方向为E-band通信系统编解码技术。

LI Chao was born in Quzhou,Zhejiang Province,in 1989.He is now a graduate student.His research concerns coding/decoding technology for E-band systems.

Fast Parallel FIR Shaping Filter Design for E-band Systems

ZHONG Wen-bin,ZHOU Zhi-gang,WANG Li-yun,LI Chao

(Broad band Wireless Technology Lab,Shanghai Institute of Microsystem and Information Technology,Chinese Academy of Sciences,Shanghai 200050,China)

The E-band communication system implies high speed pulse shaping filter.On the basis of fast FIR(Finite Impulse Response)algorithm(FFA)and fast iterated short convolution algorithm,a parallel FIR shaping filter is designed.The hardware-complexity and time-delay performances are analyzed,and the filtering properties are verified according to both floating point and fixed-point simulation.The parallel FIR filter can decrease 21% of the multiplications and 13.4%of the delays,and fulfills the E-band system demands with 6-bit quantization. Key words:E-band communication system;parallel FIR filter;pulse shaping filter;iterated short convolution;fixed-point simulation

�想成形滤波后星座图 Fig.3

constellation with ideal shaping filter

The National Science and Technology Major Project(2010ZX03003-004,2011ZX03004-003);Chinese Academy of Sciences Strategic Pilot Projects(XDA06010304);Chinese Academy of Sciences Key Deployment Project(KGGZD-EW-103-5(4))

TN713;TN911.72

A

1001-893X(2013)09-1223-06

钟文斌(1988—),男,福建龙岩人,2011年于上海交通大学获工学学士学位,现为中科院微系统所硕士研究生,主要研究方向为宽带无线通信技术、E-band通信系统关键技术;

10.3969/j.issn.1001-893x.2013.09.020

2013-04-28;

2013-06-09Received date:2013-04-28;Revised date:2013-06-09

国家科技重大专项(2010ZX03003-004,2011ZX03004-003);中科院战略性先导专项(XDA06010304);中科院重点部署项目(KGZD-EW-103-5(4))

❋❋通讯作者:wenbin.zhong@mail.sim.ac.cnCorresponding author:wenbin.zhong@mail.sim.ac.cn