8Transistors SRAM稳定性分析与验证

2013-06-13刘章发

丁 艳,刘章发

(北京交通大学电子信息工程学院,北京100044)

1 引言

SRAM静态随机存储器是目前如平板电脑、智能手机等拥有广泛用户群的便携产品的重要组成部分。随着便携产品的迅猛发展,人们对电池的续航能力要求也越来越高。为了提高电池的续航能力,低电压低功耗的设计需求越来越迫切。随着供电电压的降低,SRAM的稳定性变的更差[1]。尤其是在纳米工艺下,芯片面积日益缩减[2],严重降低了静态噪声容限SNM和写容限WM,从而进一步制约着SRAM 存储单元的稳定性[3-4]。

以前的研究主要集中在性能上稳定和较完善的6T结构SRAM存储单元,如图1所示。随着高密高稳定性存储单元的需求日益迫切,8T结构 SRAM存储单元受到了广泛关注,如图2所示,该种结构比传统的6T单元具有低压下更高的稳定性[5-6],尤其是对SNM和WM的改善。SNM和WM是表征SRAM存储单元稳定性的关键参数,也是SRAM设计的重要性能指标。虽然8T存储单元相比6T存储单元具备更好的稳定性,但是面积偏大这一劣势限制了其广泛应用。如何保证高稳定性的同时又能控制8T结构存储单元的芯片面积一直是研究的热点。

图1 6TSRAM 存储单元结构示意图

图2 8T SRAM存储单元结构示意图

通过详细分析8T结构存储单元的SNM和WM,寻求弥补8T存储单元相比6T面积过大的办法。

2 理论分析

影响SRAM存储结构单元性能的指标主要有读写稳定性、读电流以及面积成本等。

8T结构存储单元如图2所示,有两条字线和三条位线,其读写端口分开,读和写操作分别通过字线和位线进行数据的读取和写入,可以对读和写性能分别进行优化。其读和写操作的工作过程分别为:

写操作:与6T的写操作一样。当写字线(WWL)使能时,数据分别通过两个选通管M5、M6将位线(WBL和WBLX)上的数据写进存储单元。此时,读字线(RWL)处于无效状态,即读写分开。

读操作:当读字线(RWL)使能时,写字线(WWL)处于无效状态,存储单元的数据通过M7和M8管读出数据到读位线上(RBL)。

2.1 读写稳定性分析

SRAM的读写稳定性主要通过静态噪声容限SNM和写容限WM来分析。

SRAM存储单元的静态噪声容限SNM,是指存储单元受噪声的影响能够发生翻转的最小直流电压,反映了电路对噪声的耐受程度,

以6T存储单元为例,比较经典的SNM分析方法[7],如图 3 所示。

图3 SNM分析模型

6T存储单元除了选通管外的结构可以认为是两个反相器组成的一个锁存器。Vn是指静态噪声源。锁存器的SNM就是指在使得锁存器发生状态翻转之前的最大Vn。

假设图4中A点存逻辑1,B点存逻辑0,当进行读操作时,M1和M6工作在饱和区,M2和M3工作在线性区,M4管和M5管工作在亚阈值区,近似截止。

图4 SNM具体分析

根据基尔霍夫电流定律

以及基尔霍夫电压定律

整理可得:

上式(3)未曾考虑NMOS和PMOS阈值电压的不同,以及默认所有输入电压均为VDD。在实际操作中NMOS和PMOS的阈值电压是不同的,必须分开考虑。静态噪声容限SNM受到供电电压VDD、器件尺寸的比值因子CR以及MOS管的阈值电压影响。供电电压VDD的变化对SNM的影响受制于CR值的影响,跟据CR值的不同,变化也不同;如果CR值比较大,则VDD与SNM是正比例关系。SNM是受制于CR比值因子的影响,不会因为某一管子宽长比的改进而改善稳定性,选取较大的CR值是改善SNM的有效途径。同时SNM与阈值电压的变化也是成正比例关系,温度与阈值电压成反比例关系,因此在低温条件下SNM会更好一些。

写容限是指能够写入存储单元的最大电压值,其影响因素也同样受三方面的影响,即VDD、阈值电压以及器件宽长比因子PR(公式5所示)的影响[8]。

在通常设计中,如果工艺和仿真环境一定的情况下,SNM主要通过参数CR来调节,CR越大,SNM值会越大。WM主要通过参数PR来调节,PR越小,WM值越大。

另一方面,器件尺寸由于受到SNM和WM两方面的影响,同时考虑稳定性和面积两方面的改善,W/L比值即PD:PG:PU三者之间比值会最终达到一个平衡值[7]。如果在该种情况下,仍要提高稳定性或者改善面积,就需要考虑其他的影响因素。其中最为重要的是考虑噪声的来源,如位线电压对稳定性的影响。

2.2 位线电压—预充电电压对稳定性的影响

位线电压,即位线的预充电电压。通常情况下,该电压会被预充电到供电电压VDD,尤其是对6T存储单元结构;如果该电压下降,则BL上的读电流会相应的下降,对SRAM的速度会造成影响。为了避免降低读电流,位线电压需要预充到高电平。对于8T存储单元结构,读写操作分开,调节写位线上的电压对读电流造成的影响微乎其微,这在后边的仿真可以验证。因此,可以通过这一因素来进一步提升稳定性。

首先,通过对SNM进行分析可知,如果降低位线上的电压,则会使得B点的电压处于弱电位状态,反相器发生翻转变得困难,从而提高了噪声的耐受能力。

翻转电压如下:

位线预充电电压降低,图2中8T存储单元内部存储点的电位会处于弱电位,使得写能力受到一定影响,根据PMOS管的上拉特性和NMOS管下拉特性,A和B点电位最终会处于一个平衡状态,不会造成太大的影响。

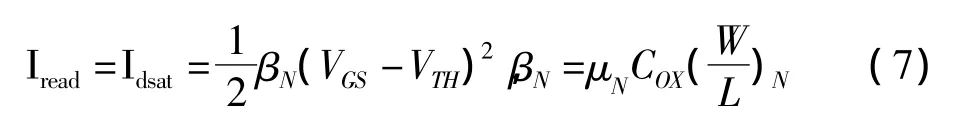

大多数的研究都仅仅是提及预充电至高电平,即供电电压VDD。这主要是因为大多数的研究设计采用6T存储单元结构。根据工作在饱和区(VDS5>VDD-VTN)的MOS管的源漏电流公式Idsat=可知,降低位线电压,会减小读电流。因此,为了保证读电流不会被降低,从而降低芯片的读取速度,都采取对位线预充到供电电压VDD。但是如果考虑到8T存储单元结构读写端口分开的特点,降低位线的预充电压值不会降低读电流,因此采取调节预充电电压的方案是可行的。

2.3 预充电单元基本结构

6T存储单元结构的SRAM的预充电单元结构是利用三个PMOS管栅极相连构成的,如图5所示。

图5 6T存储单元结构预充电单元电路图

该预充电结构的P1管和P2管分别对两条位线BL预充电,而P0管则是一个均衡管。目的是保证两条位线BL预充电压的一致,防止SA(灵敏放大器模块)读取BL电压差时发生误差,导致错误的操作,造成读失败。

8T存储结构的SRAM的预充电结构因为有两条写位线和一条读位线,且写位线预充电电压值不需要精确的保持一致,所以分别只需要一个PMOS管即可。如果考虑到前边分析的预充电电压大约降了一个阈值电压值的大小,可以考虑使用NMOS管代替PMOS管来实现预充电的功能。

2.4 读电流

典型的6T结构存储单元,读电流是指流过位线BL上的饱和电流Id,即

该种结构的读电流受位线电压、供电电压、晶体管宽长比以及阈值电压等因素的影响。读电流主要制约SRAM的读取速度,所以,如果要保证芯片的读取速度就不可以降低存储单元的读电流。

8T结构的存储单元相比6T结构存储单元,读电流是改善性能的关键因素。由于读写端口分开,写端口的写位线电压的变化不会对读电流造成影响,从而保证了利用写位线电压的变化改善SNM的方法,不会影响芯片的高速性能。

2.5 面积因素

从面积方面来看,就预充电单元而言,8T存储单元相对6T存储单元并未造成面积上的过多浪费。整体而言,为了保证稳定性性能指标与6T一致,甚至更好,不可避免的造成了部分面积的损失。但是,相比6T单元的面积而言,面积并未造成很大的浪费。因此,面积的劣势在此得到了很好的控制。

建立一个简易模型(如公式5所示),理论上简略计算一个晶体管的面积:

其中,W0是指单个管子的有效栅宽,ΔW是指管子的栅与有源区的最小约束,W1指估算的单个晶体管占用空间的总有效宽;同理可得L1为晶体管占用空间的总有效长。Sarea是指单个晶体管的估算面积。

通过该种计算面积的简略模型分析,可以大体上估计芯片面积的变化。

根据该种模型的计算可知,虽然8T存储结构多了两个NMOS管,但是由于整体晶体管的宽长减小,再通过折衷提升的部分SNM值,缩减晶体管的尺寸,可以进一步减小晶体管的尺寸,因此面积上相比6T不会造成很大的浪费。

3 仿真结果验证分析

采用SMIC 40nm工艺技术搭建电路环境,使用Cadence公司的spectre仿真器对电路分析进行仿真验证分析。

对8T存储单元结构电路,调节MOS管的尺寸,W/L 大致的比值为:PD∶PG∶PU=1.1∶1.9∶2.6,而读端口的两个MOS管的尺寸一致,其中栅长L尺寸选取logic model(器件参数库)下的最小尺寸,栅宽W选取为最小尺寸的两倍。通过调节预充电电压,提高稳定性性能指标,改善稳定性,进而可以通过折衷这一部分性能来进行尺寸的缩减,达到改善面积的目的。

仿真测试也是通过对SNM、WM和读电流Iread三方面的性能指标来验证。

3.1 SNM

SNM的测试电路是根据图4的电路结构来进行的。通过变化噪声源电压值,使得存储单元的状态发生翻转,此时测得的最大噪声源电压值即是SNM。通过瞬态仿真和直流仿真可以得到以下数据。

首先需要通过测试得到适合的预充电电压值,即预充电到多少时,SNM最大且比较稳定。

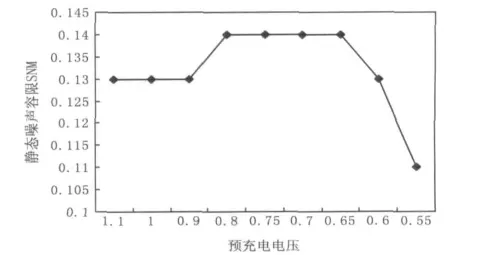

如图6所示,是预充电电压和SNM之间的关系,横坐标表示预充电电压,纵坐标表示SNM。测试环境PVT(工艺、电压和温度)是:工艺corner为FNSP,供电电压 VDD=1.1V,温度为 125°,即选取了相对SNM而言较差的工艺。预充电电压的范围是从1.1V到0.55V。通过瞬态仿真测出SNM值进行比较得出该图。

图6 静态噪声容限与预充电电压间的关系

分析图6的仿真结果可知,当位线上的电压预充电降到0.7V时,静态噪声容限有明显提升。相比预充电电压 =VDD=1.1V的 SNM值,提升了10%左右。

MOS管的阈值电压大约在0.4V左右,VDDVth在0.7V左右。

图7是外界因素如温度对SNM的影响。由该图可以看出,随着温度由零下40°逐渐升高至125°,噪声容限逐渐变小。从图7可以更加验证预充电电压的变化范围对SNM的影响。因此,若预充电电压调节到0.7V时,即下降大约为一个阈值电压时,SNM会比较稳定。

图7 温度对静态噪声容限的影响趋势图

3.2 WM

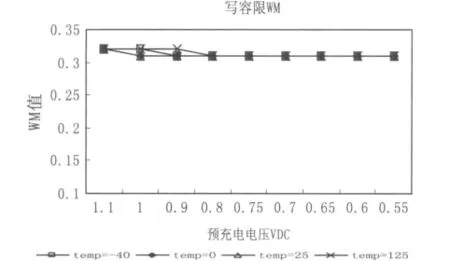

写容限的仿真方法,同样是使用spectre工具来测量。首先扫描位线BL上电压的线性变化,直到存储单元的原状态发生翻转的最大电压,即为写容限WM。具体的测试结果如图8所示。

图8表示的是预充电电压对WM的影响。横坐标表示预充电电压,纵坐标表示WM。从该图可以看出,随着预充电电压的降低,WM变化很小。而且随温度的变化影响也不大。因此调节写位线的预充电电压基本不会影响WM,是可取的。

图8 预充电电压对WM的影响趋势图

综上论述可知,降低写位线的预充电电压提升了静态噪声容限,而且不会对写性能造成太大的损失。

3.3 读电流

读电流,即存储单元位线上流过的电流。测试时,可以通过测试NMOS管(M8)的源漏电流来得到。由于读写端口分开,调节写位线的预充电电压对读电流不会造成影响。通过仿真测试可知,结果几乎未发生变化。改善写位线电压确实没有减小8T存储单元的读电流,从而保证了芯片的高速性能。

3.4 面积

通过版图以及仿真测试可知,如果保证读电流和SNMWM的值与参考的6T结构存储单元的性能指标接近的话,面积损失不大。如果将读电流提升75%,则面积损失约15%。因此,即使是在保证高性能的同时,也可以很好的控制芯片的面积,避免成本过多浪费。

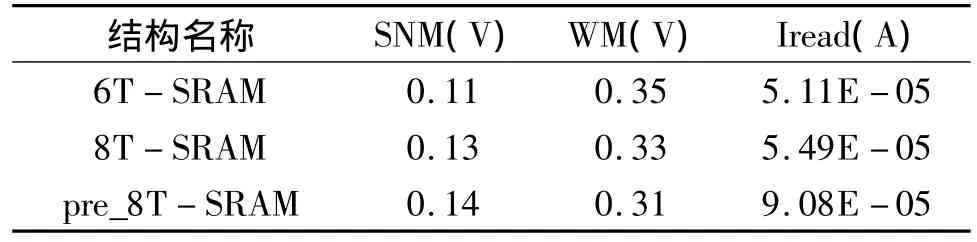

综上所述可得,分别在最差的仿真条件下得到SNM的最小值(FFcorner,125°)和 WM 的最小值(SSCorner,-40°)(见表1)。在降低预充电电压约一个阈值电压的设计时,为了满足高速的要求,以牺牲部分面积来提升读电流。如果牺牲10%左右的面积,读电流可以提升2倍左右(即pre_8T-SRAM的读电流)。8T结构存储单元性能指标和6T结构存储性能指标的相关数据,如表1所示。

表1 稳定性性能指标

表1中,6T-SRAM是6T结构的SRAM,作为参考结构。8T-SRAM是提升稳定性同时控制面积的8T结构 SRAM。pre_8T-SRAM是指在8TSRAM的基础上其预充电电压降低一个阈值电压Vth时的SRAM。

通过数据可知,SNM的值比较差,是影响稳定性的关键因素,而WM的值偏大,因此考虑牺牲部分WM来提升稳定性是可取的。同样,如果考虑牺牲部分面积则可以换来更快的速度。

4 结束语

8T存储单元结构的SRAM,性能更加优化。不仅可以通过调节器件的尺寸取得高稳定性,还可以在此基础上调节写位线电压即预充电电压,进一步提升稳定性。以SMIC 40nm工艺为例可以提高10%左右,甚至更高。如果考虑以改进的稳定性折衷为减小器件尺寸,则可以在一定程度上改善原有设计面积过大的问题。因此调节预充电电压带来的优势值得被考虑,并可被应用到具体的设计之中。

[1]Pilo H,Arsovski I,Batson K,Braceras G,et al.A 64Mb SRAM in 32nm High-k Metal-Gate SOI Technology with 0.7V Operation Enabled by Stability,Write- Ability and Read - Ability Enhancements[J].IEEE Conference Publications,2011(2):254 -256.

[2]T Suzuki,S Moriwaki,A Kawasumi,et al.0.5 - V,150 -MHz,Bulk-CMOS SRAM with Suspended Bit-Line Read Scheme[J].IEEE Conference Publications,Sep.2010:354-357.

[3]Krishnan A.T,Reddy V,Aldrich D,et al.SRAM Cell Static Noise Margin and VMIN Sensitivity to Transistor Degradation[J].IEEE Conference Publications,2006:1-4.

[4]Ming-Long Fan,Yu - Sheng Wu.Investigation of Cell Stability and Write Ability of FinFET Subthreshold SRAM Using Analytical SNM Model[J].IEEE Transactions On Electron Devices,2010,57(6):1375 -1381.

[5]RKapre,K Shakeri.SRAM Variability and Supply Voltage Scaling Challenges[J].IEEE Conference Publications,2007:23-28.

[6]Hiroyuki Yamauchi.Embedded SRAM Circuit Design Technologies for a 45nm and beyond[J].IEEE Conference Publications,2007:1028 -1033.

[7]E Seevinck,F J List,J Lohstroh.Static - noise margin analysis of MOS SRAM cells[J].IEEE J.Solid State Circuits,Oct.1987,SSC -22(5):748 -754.

[8]Jiajing Wang,Satyanand Nalam.Analyzing Static and Dynamic Write Margin for Nanometer SRAMs[J].IEEE Conference Publications,2008 ACM/IEEE International Symposium:129-133.