基于CPLD的视频、音频和数据综合传输系统

2013-01-31胡秀洁孙艳玉张宝艺宋家友

胡秀洁,孙艳玉,张宝艺,宋家友

(郑州大学 信息工程学院,河南 郑州450001)

模拟式传输终端有信号同传时交调干扰严重、容易受环境干扰影响、传输质量低、长期工作稳定性差等缺点,因此,市场上模拟传输终端已逐渐被数字传输终端所代替。本文设计了一种运用低压差分信号(Low-Voltage Differential Signaling,LVDS)技术[1]的数字信号光纤传输系统,可以在一根光纤中同时传输4路数字视频、1路音频和1路数据信号。硬件基于E2PROM或Flash存储器编程的CPLD,编程次数可达上万次,相比FPGA具有系统断电时编程信息不丢失和保密性好的特点。

所设计终端可用于平安城市、高速公路、银行以及电力系统等的远程监控、远程会议、远程教学、远程医疗等领域,还可以根据需要将不同路数的视频、音频和数据进行任意组合以满足各种不同需求。

1 系统设计

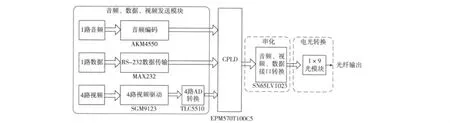

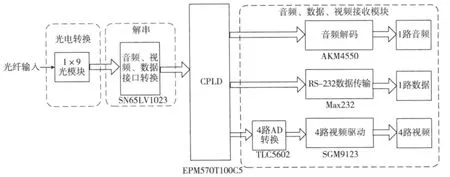

本设计由发送板和接收板2个部分组成。发送板实现的功能是:将4路无压缩视频信号和1路音频信号进行高分辨率数字化,再与1路数据信号一起形成高速多路正向数字流通过CPLD器件,运用Verilog HDL语言编程,实现正向数据的一次复接,并运用LVDS技术将复接后的数据转换为高速差分信号后通过光电一体模块进行发送。接收板运用LVDS技术将接收到的混合信号进行低速分接,并通过CPLD器件二次分接,恢复视频、音频和数据信号,再进行数模、电平转换后,发送到相应的端口。发送板和接收板结构设计框图及所用芯片分别如图1和图2所示。

图1 发送板结构框图

CPLD是整个系统的核心,选择Altera公司MAXⅡ器 件系列的EPM570T100C5芯片,该器件系列是一种非易失性、即用性可编程逻辑系列,是所有CPLD系列产品中成 本最低、功耗最小和密度最高的器件。

图2 接收板结构框图

2 硬件设计

综合传输系统的硬件设计主要包括CPLD核心器件、视频音频数据信号采集、处理和电平转换模块、LVDS串化/解串化模块以及信号的电光、光电转换模块。

2.1 视频模块

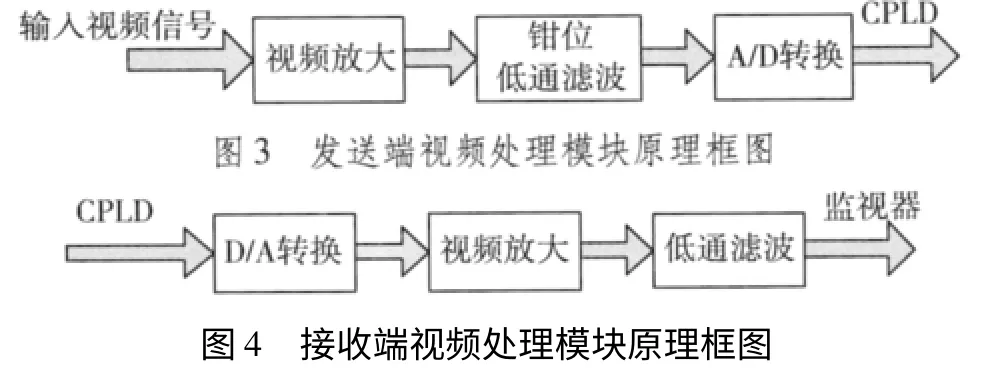

发送端视频模块由摄像头采集模拟视频信号,然后通过SGM9123芯片完成放大、滤波、钳位[2]等预处理,并进行模数转换,然后送入CPLD中完成数字信号的一次复接。光传输接收端视频模块实现的功能是将由CPLD输出的数字信号送入TLC5602和SGM9123芯片进行数模转换、视频放大和低通滤波,最后转换成模拟信号送到监控设备上。

发送端和接收端的视频处理模块[3]原理框图分别如图3和图4所示。

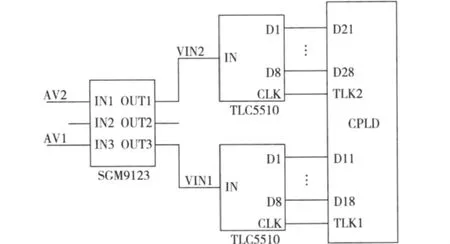

视频信号为模拟低频信号,为得到CPLD所需的数字信号,必须经过放大、滤波和模数转换。模拟信号中包含交流和直流分量,经过放大器时,由于其中耦合电容的影响,信号会失去直流部分。视频信号失去直流部分,图像的同步电平将不能固定在同一电平上,同步头将随图像的变化而变化。所以为了使其不受图像变化的影响,必须恢复直流分量,使同步头钳制在同一电平上。SGM9123是一个具有钳位功能,内置带宽为8 MHz的低通滤波器和6 dB增益放大电路的三通道视频缓冲器,因此发送端和接收端的视频驱动电路都采用此芯片。模数和数模转换芯片则采用TLC5510和TLC5602,它们是8 bit、低功耗的转换器。图5为2路视频发送原理图。

图5 2路视频发送原理图

2.2 音频和数据模块

数据信号利用RS-232通信接口传输到数据模块发送端,数据模块发送端和接收端通过MAX232[4]芯片进行转换,将计算机串口信号电平和CPLD电平相互转换,以达到计算机和CPLD可以通信的电平标准。图6为1路数据发送原理图。

发送端音频模块是将采集到的音频信号传输至音频编码器,编码后的数字信号接入CPLD;接收端则是对称相反的过程。发送端和接收端的音频处理芯片都采用AKM4550,它是一款低电压,左、右声道各16 bit的A/D和D/A便携式数字音频系统转换器。

2.3 LVDS串化/解串设计

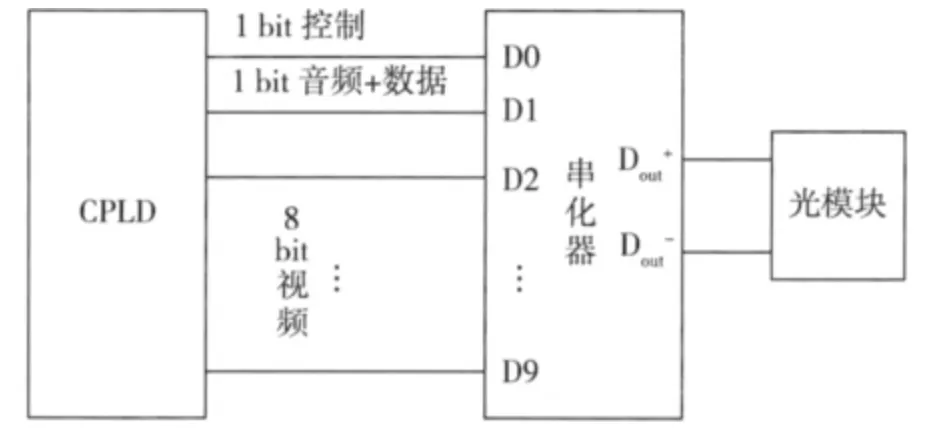

LVDS串化/解串芯片分别采用SN65LV1023和SN65LV1224,它们是10 bit串行器/解串器芯片组,并且SN65LV1023和SN65LV1224成对使用。经CPLD芯片处理后的视频信号和音频及数据信号送入SN65LV1023开始串化过程,10 bit输入信号中低8 bit用于传输采样转化后的视频信号,1 bit用于传音频和数据混合信号,1 bit为控制位信号。输出的DOUT+和DOUT-送入光纤传输模块,解串过程则相反。图7为串化过程原理框图。

图7 串化过程原理框图

2.4 光电模块

发送端,信号经串化器二次复接后,所形成的高速数字差分信号通过光电转化器转换成光信号并通过光纤进行传输。接收端则把光纤传来的信号再转化为电信号,然后送入解串器作进一步处理。

本设计中采用的是1.25 Gbit/s与84 Mbit/s速率不对称单模单纤光收发一体模块,它可以通过单根光纤实现双向工作,单电源+3.3 V/+5 V供电,发射器件可选用工作波长为1 310 nm或1 550 nm的FP、DFB激光器。

3 软件设计

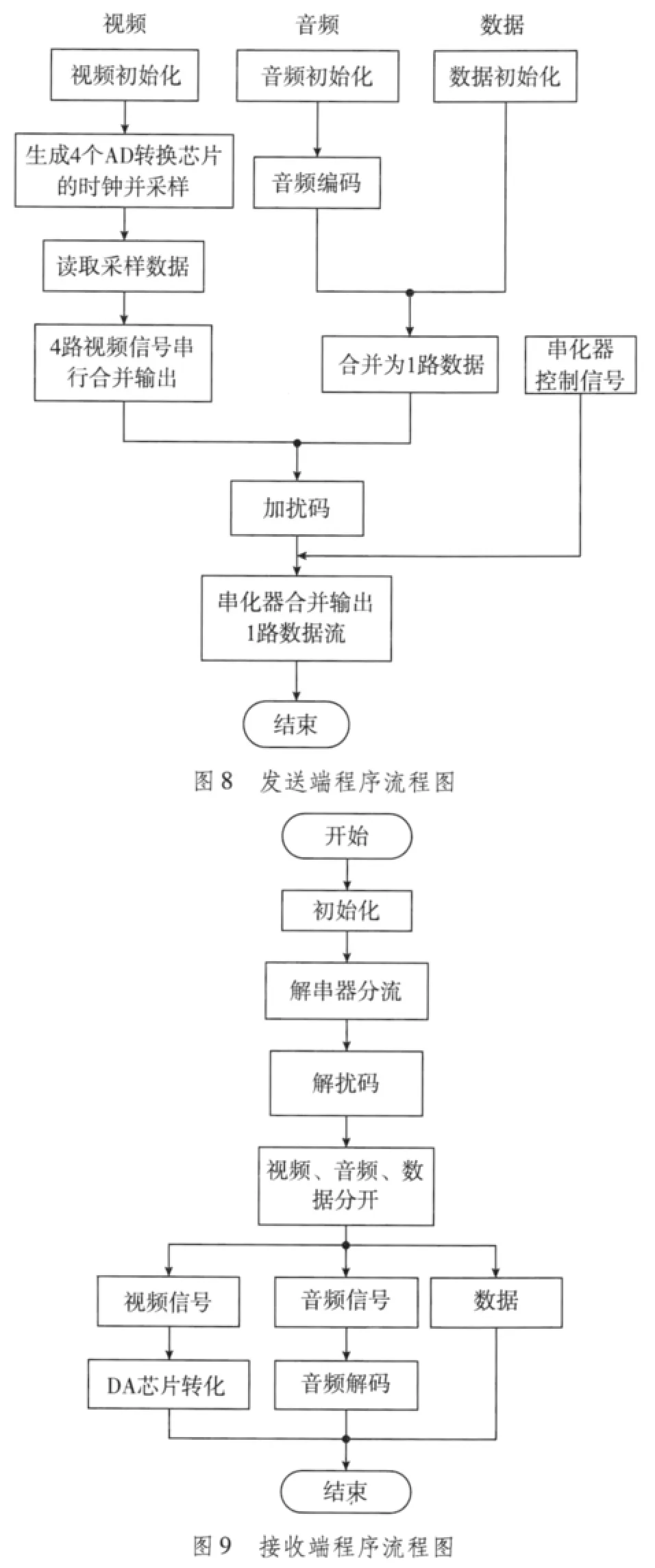

软件设计利用Verilog HDL语言进行编程[5],使CPLD实现所需功能。主要包括:各信号模块初始化、提供时钟信号、处理采样数据、完成串行数据与并行数据的转换以及扰码/解扰码[6]等。图8和图9是发送端和接收端程序流程图。

3.1 发送端并/串数据转换

发送端的视频信号转换频率为15 MHz,而CPLD采样频率60 MHz。通过对60 MHz进行四分频,得到4路15 MHz信号,因而可完成4路视频信号串行输入,并将4路视频数据合并为1路数据流,共8 bit,与8 bit扰码对应位异或后接至串化器的8个输入端口。同样,1路音频信号经过编码后和1路数据合并,与1 bit扰码异或后接至串化器的另一个输入端口。串化器最后一个控制口依次输入00110011…,此信号用来识别视频各路数据输入,便于在接收端分离4路视频信号。音频数据时钟为32 kHz,数据波特率为9 600 baud。发送端时序图如图10所示,其中,fold_out表示加扰码前视频和音频数据混合信号输出的数据流,p_serial_dtout表示加扰码后输出的数据流。

3.2 接收端串/并数据转换

P_data_in是解串器一次分接后输入CPLD的低速数字信号,其时钟安排与发送端相同。根据时钟信号的不同,可分出视频、音频和数据信号,并将其对应送入相应处理模块。图11为接收端时序图,图12为将时钟周期缩小后音频数据时序图。

图10 发送端时序图(截图)

3.3 扰码/解扰码设计

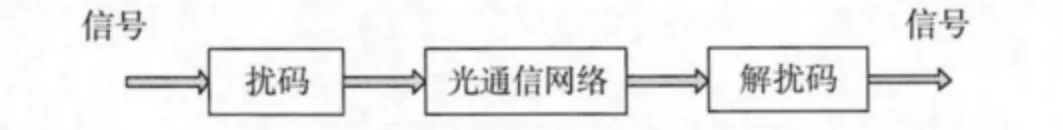

扰码的作用是对输入信号进行随机化处理,以减少数据的连“0”和连“1”数目,确保接收端的位同步提取。同时还可以扩展基带信号频谱,起到加密效果。因此,需要对传输数据在发送端进行加扰,在接收端进行解扰。扰码结构框图如图13所示。

图13 扰码结构框图

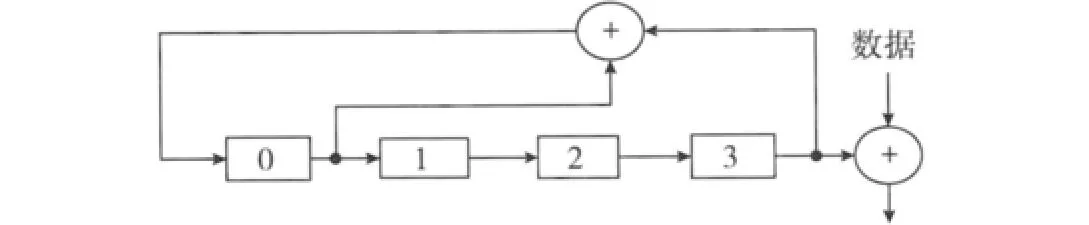

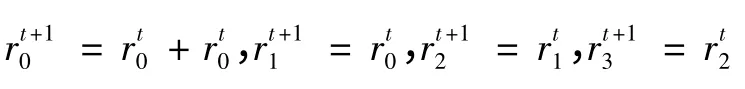

扰码信号通过循环移位寄存器产生,而扰码器的结构则由扰码生成多项式决定。本设计中使用的扰码生成多项式为x4+x1+1。图14所示是由该生成多项式确定的扰码器结构框图。

图14 扰码器结构框图

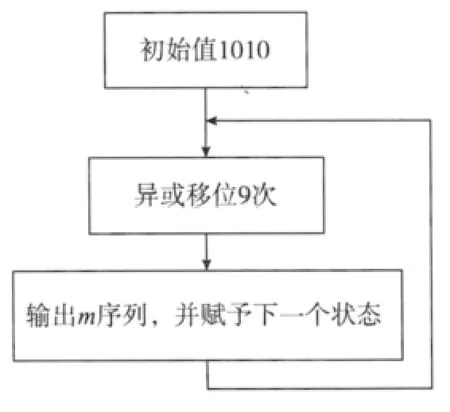

设计中假设初始值为1010,由上式可知,下一值为1101,一直到第9个值为1000。取各组值的末位为第1个9 bit扰码信号,然后初始值会变成下一个时刻的值,经过不间断的循环,产生一系列9 bit数据扰码。图15为扰码程序流程图。

图15 扰码程序流程图

4 结束语

本文所设计的综合传输系统,以CPLD为核心,传输性能稳定,便于调试和升级。SGM9123等多功能芯片的选择、对称原则的设计布线,简化了硬件电路的设计,降低了成本。同时运用LVDS技术,完成了图像、声音和计算机发出的操作指令的传输。经过实验测试,图像传输稳定,声音传输清晰,计算机操作指令传输无乱码和丢字现象,指令正确。

[1]蒋东初,李玉山.LVDS在高速数字系统中的应用研究[J].现代电子技术,2009,32(7):147-150.

[2]姜鹏,何毅.应用CPLD的数字光端机的设计与实现[J].自动化仪表,2011,32(1):80-82.

[3]王德胜,康令洲.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-35.

[4]任安虎,张燕.一种实用光端机的设计与实现[J].电子设计工程,2010,18(9):55-58.

[5]潘松,黄继业,潘明.EDA技术实用教程—Verilog HDL版[M].4版.北京:科学出版社,2010.

[6]张立鹏,朱清新,青华平.100G以太网自同步并行扰码算法实现[J].通信技术,2010,43(5):135-137.