基于DSP和DDS技术相位及频率严格可调的多路同步信号发生器*

2012-12-28吴校生周晓玲陈文元张卫平

邓 腾,吴校生,周晓玲,陈文元,张卫平,崔 峰,刘 武

(微米/纳米加工技术重点实验室,上海交通大学微纳科学技术研究院,上海200240)

在各类信号发生器中,我们通常需要产生高稳定性的频率信号输出,一般是通过频率合成的方式来完成的,频率合成是指从一个高稳定的参考频率,经过各种技术处理形成一系列稳定的频率输出[5]。传统的直接频率合成器体积大、硬件成本高;锁相环路法频率分辨率低、频率跳变速度慢[2]。直接数字频率合成(DDS)是现在发展起来的一种新的频率合成技术。DDS的优点是:相对带宽很宽,频率转换时间极短,频率分辨率很高,全数字化结构便于继承,输出相位连续,频率、相位和幅度均可实现程控[8,10],因此能够和计算机紧密地结合在一起,充分发挥软件的作用。本文以TI公司的TMS320F2812型DSP为核心处理器,对DDS芯片AD9833进行程控从而实现合成频率的输出。利用DSP多引脚输出的特点,实现对多块DDS芯片的程控,通过软件编译,实现相位严格可调的多路信号产生[6,9]。传统的多路固定相位差的信号发生主要是通过RC移相电路实现的,这样产生的信号容易幅值发生衰减,而且相位差不够精确,而且相位差的调整改变相对复杂。本文中采用的程序控制产生移相信号能够得到相位差稳定且严格可调的无衰减信号[2,4]。

1 系统基本原理

1.1 DDS工作原理

可编程DDS的核心是相位累加器,它由一个加法器和一个N bit相位寄存器组成,N一般为24~32,AD9833为28 bit的相位累加器。每来一个外部参考时钟,相位寄存器便以步长M递加。相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。正弦查询表包含一个正弦波周期的数字幅值信息,每一个地址对应0°到360°范围的一个相位点[1]。

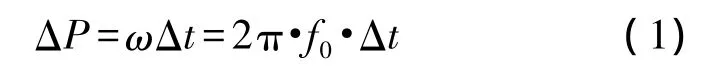

AD9833中使用的DDS技术是从连续信号的相位出发,将一个正弦信号取样、量化、编码,形成正弦查询表。合成是改变相位增益,由于相位增益不同,一个周期内采样点数就不同,产生的正弦信号频率也不同,达到频率合成的效果。正弦波信号是非线性的,而其相位是线性的,因此每隔Δt(时间周期)有对应的相位变化。Δt,即:

所以合成的频率信号为:

其中Δt=1/fm。由式(2)可以看出改变ΔP可以得到不同的f0值。

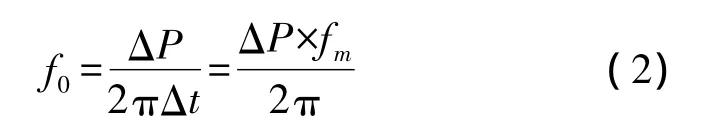

DDS芯片AD9833原理框图如图1。

图1 DDS原理框图

图1所示的是DDS芯片工作的原理框图,进行的是DA数模转换,通过相位累加器反映到正弦查询表上,正弦查询表包含一个正弦波周期的数字幅值信息,每一个地址对应正弦波0°~360°范围内的一个相位点,查询表把输入地址的相位信息映射成正弦波幅值信号,然后驱动DAC转换成模拟信号输出,实现控制频率、相位都可调的正弦波。

其中相位累加器为28 bit的,取其高14 bit作为读取正弦波寄存器地址,对应波形相位变化为:

因此,合成频率与频率控制字K直接相关:

设定参考频率,K取值范围为1<K<228。

1.2 DDS多路相位控制原理

目前,单片芯片能够多通道输出信号的芯片很少,而且价格昂贵,因此,可以用多片单通道DDS产生多路信号,难点是如何控制多路信号的同步与相位差。传统控制多路信号移相的方法是通过RC移相电路来实现,这样的移相方法产生的多路信号容易发生幅值不稳定以及信号衰减的问题。一般采用的低通RC移相电路,传递函数为:

我们所需要的是两路相位差90°的信号,而RC移相电路在90°相位移动时幅值的衰减几乎达到了无限。幅值在理论上可以通过放大电路放大,但实际上过小的幅值其抗干扰能力将会大幅变小,使波形剧烈失真;即使幅值可以经过后级补偿,但是此电路永远达不到90°的相移,只能无限接近,使得电路的性能指标下降。传统的解决办法是采用多级RC移相电路来实现,但是这样会使得电路趋于复杂而产生更多的失真与干扰等问题。[2,4]

本文中实现多路信号的相位移动的办法是直接使用DSP控制多块DDS的控制字来实现。产生多路固定的相位差信号同样需要注意同步问题。主要影响因素有:

(1)所有DDS时钟源之间相位差要小于最小限度,因此在PCB布局时使时钟源达到各路DDS的走线等长,以保证参考时钟到达DDS系统具有相同的时钟沿。

(2)在DDS系统上电之后传送数据之前应产生复位信号,它能使DAC输出处于一个相同的状态,成为一个共同的参考点,从而使DDS同步。

在两路DDS能够同步输出的基础上,通过控制DDS芯片接受相同的时钟沿信号,即相同的MCLK信号与FSYNC使能信号脉冲,并改变DDS芯片的相位控制字,就可以轻松实现多路DDS信号的相位严格控制。[5-6]

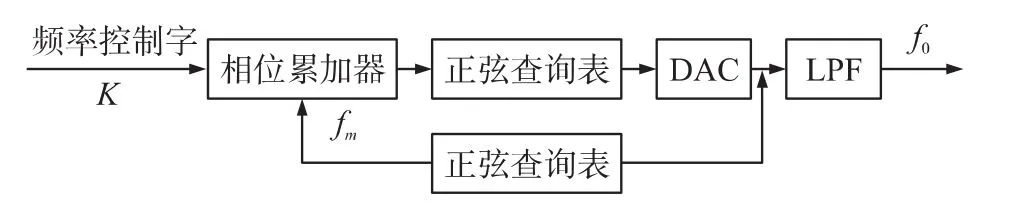

2 多路固定相位差DDS信号发生器的硬件设计

多路相位严格可调DDS信号发生器包括控制核心和DDS信号产生模块。本设计采用TMS320F2812作为控制核心,通过TMS320F2812的GPIO口来传递控制字和工作时序。以两路相位差90°的DDS信号为例,DDS信号产生模块由两片AD9833实现。本系统的硬件电路和外围接口如下图2所示。

图2所示为利用DSP输出控制字控制两片AD9833芯片产生相位差严格90°的信号发生器电路,两路信号发生之后分别经过一个一阶高通滤波器,完成基本的滤波,调节偏置。两片AD9833芯片共用一个晶振信号,信号频率为 25 MHz。[3,6]

两片AD9833共用参考时钟频率SCLK,对应F2812的 GPIOA0口;频率更新信号 FSYNC,对应GPIOA2口;外部参考时钟频率MCLK,连接到晶振信号输出。而F2812的GPIOA1口和GPIOA3口分别控制两片AD9833的控制字加载,实现串行加载,可以分别实现不同频率和不同相位的控制。通过程序控制GPIO口模拟SCLK与FSYNC的时序信号,并发送对应控制字信号结合时序信号对AD9833进行控制,实现VOUT端口波形良好的正弦波信号输出[7]。

图2 多路相位严格可调DDS信号发生器硬件电路设计

3 多路固定相位差DDS信号发生器的软件设计

AD9833有16 bit控制字,其中两位是用于选择工作方式,AD9833有一个28 bit的相位累加器,2个28 bit的频率寄存器FREQ0和FREQ1用于设定K值,2个12 bit的相位寄存器用于设定相位值。16 bit控制字前两位用于选择工作模式,00为写入控制字,01为写入14 bit频率字频率寄存器FREQ0,10为写入14 bit频率寄存器FREQ1,11为写入相位控制字12 bit到相位寄存器PHASE0和PHASE1。

DDS输出正弦波频率计算公式为:

式(6)中:fout为输出正弦波频率,ΔPHASE为频率控制字,CLKIN为系统时钟源频率,N为相位累加器位数。因此DDS的频率分辨率为:

AD9833的相位累加器位数N=28采用25 MHz的系统时钟源频率,输出信号频率为2 MHz,根据式(6)计算得到的AD9833的频率控制字为:MSB高14 bit 0x4083,LSB 低 14 bit 0x45fc。AD9833拥有12 bit的相位寄存器,相位调整精度为0.087 9°,相位精度很高。[7]

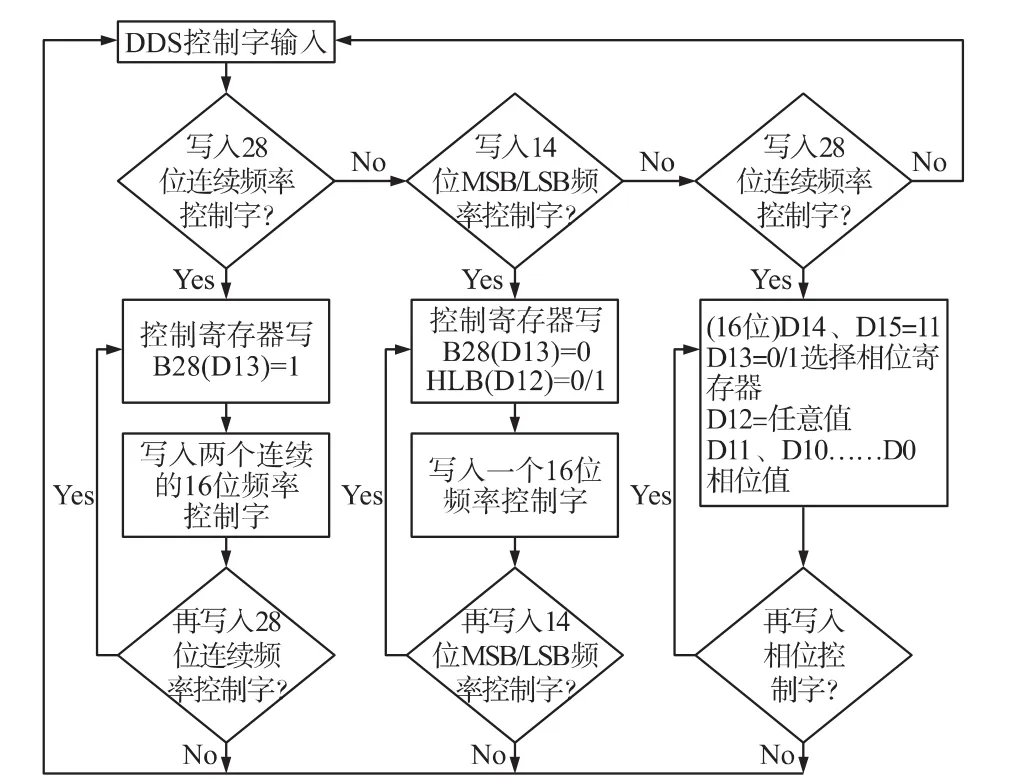

下图为设计核心AD9833的控制字输入部分的程序流程框图,整个系统的软件部分由C语言和汇编语言混合编写,在完成初始化、显示等功能后,根据AD9833的控制字方式,通过TMS320F2812按照AD9833的时序控制字写入到AD9833的内部寄存器中,完成频率信号合成。

图3所示为AD9833芯片的控制字写入流程图,由于控制字数据写入是串行接口,DDS芯片读取高低电平信号组合成控制字,确定工作模式,选择写入频率控制字的模式,是连续写入28 bit控制字或者分别写入14 bit频率控制字,抑或选择写入12 bit的相位控制字。而AD9833的数据写入是同步信号,所以在控制字发送到SDATA口的同时,SCLK表现为下降沿,而FSYNC接口必须为低电平信号,这样才能实现控制字的完整写入,从而实现针对AD9833 芯片的软件控制。[12]

图3 AD9833控制字写入流程图

GPIO口控制输入AD9833的控制字,由于共用SCLK和FSYNC,能够实现两片AD9833的频率控制字和相位控制字同时输入,并同时产生频率信号,通过给给AD9833输入相同的频率控制字和相位差90°的相位控制字,实现两路相位严格可调的频率信号的产生。[6,11]

4 实验结果

本文采用的DDS芯片AD9833和DSP控制器TMS320F2812成功实现多路相位严格可调的信号发生器,可以输出多路相位差严格可调、频率相同或可调的正弦波信号。多路信号也可独立使用,且信号稳定,频率分辨率高。由于芯片接口为串行接口,占用DSP的GPIO口比较少,因此可以进行大量芯片的同步信号或固定相位差信号的产生。

由于90°和180°相位差对比比较强烈,因此实验结果采用90°相位差和180°相位差进行对比,AD9833产生的频率范围比较小,因此主要采用200 kHz的频率信号说明信号发生器产生的频率信号的稳定性和准确性。

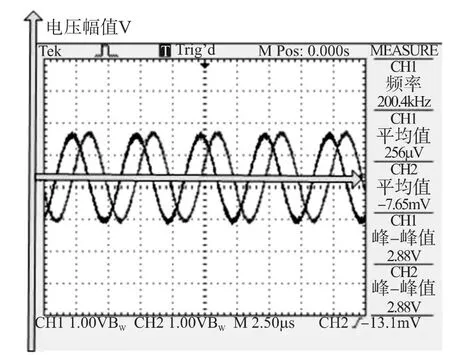

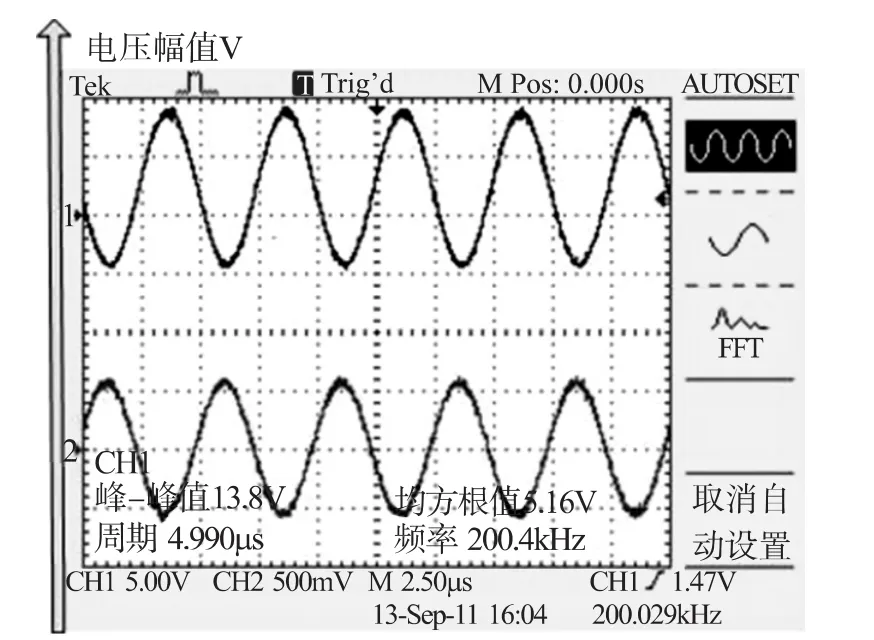

用示波器显示DDS系统生成的多路相位严格可调信号,如图4所示,两路频率均为200 kHz,相位差为90°的信号。图5所示两路频率200 kHz,相位差为180°的信号。

图4 频率200 kHz,相位差90°

图5 频率200 kHz,相位差180°

图4所示为200 kHz频率的两路相位差90°的信号,通过控制字的调整可以得到180°相位差的两路信号,如图5所示。90°相位差频率字为0xC000和 0xC400;180°相位差频率字为 0xC000和0xC8000。由上面两张图片可以看出由信号发生器产生的正弦波信号频率稳定,频率准确性很高,而相位差也很准确。

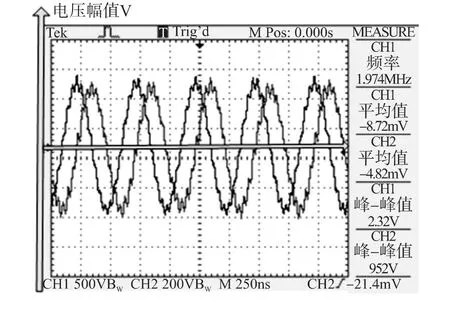

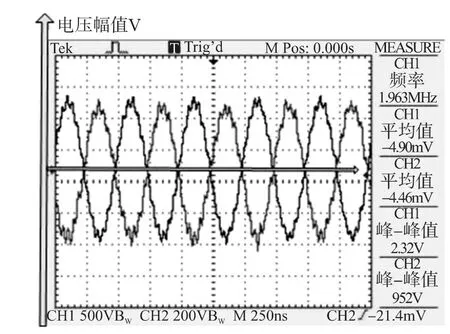

图6、图7采用的是2 MHz的频率信号进行对比,采用的相位差也是90°和180°进行对比说明。对比展示信号发生器产生的多路信号相位严格可调以及相位差稳定、精确的特性。

图6 频率200 kHz,相位差90°

图7 频率2 MHz,相位差180°

图6所示为频率2 MHz的相位差90°的两路信号,图7所示为频率2 MHz相位差180°的两路信号。由图6和图7可以看出本文所诉的信号发生器产生的两路信号相位稳定性和精确性。而且改变信号的频率和相位差只需要改变程序中输入控制字的数据即可,相比硬件电路而言更为简单方便,适应性强。因此本电路实现的信号发生器不仅能够实现相位差严格可调,还能实现频率的调整。可以满足各类信号源的需求。

5 结语

本文介绍了一种基于 DDS芯片 AD9833和TMS320F2812为控制器的电磁悬浮微马达多路固定相位差DDS信号发生器的设计方法。利用多片DDS芯片AD9833来产生多路信号,并控制使其得到固定相位差,且相位差可调。多路信号可以协调使用产生特定的相位差或者实现同步,也可单独使用,且均可做到相位、频率可调。采用串行加载方式,可实现大规模多路信号发生器。

该信号发生器可输出多路频率和相位可调的正弦波和方波,实验表明波形频率稳定性好,低频准确度高,相位分辨率高,相位差精准。可以广泛应用于科研工作及实际应用中。

[1]Analog Devices,Inc.AD9833 Data Sheet[S].2003.

[2]谢青红,张筱荔.TMS320F2812 DSP原理及其在运动控制系统中的应用[M].北京:电子工业出版社,2009.

[3]覃贞妮,刘武,陈文元.静电悬浮微陀螺多路同步DDS信号发生器设计[J].科学计算与信息处理,2010,(18):110-114.

[4]XiaoshengWu,TengDeng,Wenyuan Chen.Electromagnetic Levitation Micromotor with Stator Embedded(ELMSE):Levitation and LateralStabilityCharacteristicsAnalysis[J].Microsyst Technol,2011,17:59-69.

[5]邵诗逸,黄晓刚,刘武.磁悬浮转子微陀螺旋转驱动电路设计[J].传感器与微系统,2006,25(2):83-85.

[6]吴校生.磁悬浮转子微陀螺的设计制造及其特性研究[D].上海:上海交通大学,2004.19-34.

[7]邵诗逸,黄晓刚,刘武.磁悬浮转子微陀螺旋转驱动方式研究[J].微电子学,2006,36(1):111-117.

[8]王丹,李平,文玉梅.采用DDS频率合成的虚拟信号发生器研究[J].传感技术学报,2007,20(3):586-591.

[9]陈本永,陈艇,张丽琼,等.磁悬浮式微动工作台驱动方案的设计与实现[J].传感技术学报,2007,20(1):213-216.

[10]周文委,王涌.一种DDS信号发生方法与频谱研究[J].电子器件,2009,32(3):620-622.

[11]蒋建军,徐群.TMS320F2812与模数转换器AD7656的接口设计[J].科技信息,2007,(6):17-18.

[12]尹明,解锋,叶晓慧.基于DSP芯片控制AD9833实现雷达调频系统[J].仪器仪表用户,2007,14(3):35-36.