一种HIMAC 硬件协处理器的设计与FPGA 实现*

2012-12-22潘伟涛邱智亮

潘伟涛,邱智亮

(西安电子科技大学综合业务网理论及关键技术国家重点实验室,西安710071)

为了推进“三网融合”以及有线电视网双向化改造,利用同轴电缆连接光纤主干网和用户的传输系统成为符合我国当前网络设施现状的重要解决方案,如HINOC(High Performance Network Over Coax)[1-3]、MoCA(Multimedia over Coax Alliance)[4]、HomePlug AV[5]等系统。其中,HINOC 网络是利用有线电视网已有的同轴电缆线路分配网络,组建而成的最后100 m 范围内的宽带接入网。该技术完全利用现有的有线电视网同轴电缆网络布线,仅增加HINOC Bridge(HB)和HINOC Modem(HM)等相关设备,实现高速和高质量的多业务接入,可提供给用户IPTV、SDTV/HDTV 和高速上网等宽带应用。更为重要的是HINOC 系统是基于我国国情、自主研发的具有自主知识产权的系统,这一产品的应用将带动芯片制造、设备制造、直至业务提供商的产业链的发展,也为我国正在建设的下一代广播电视网(Next-Generation Broadcast,NGB)及“三网融合”奠定坚实的基础。

HINOC 网络协议栈为分层结构,自下而上依次为PHY 层(以下简称HIPHY[6])、MAC 层(以下简称HIMAC)和高层。MAC 层又可分为公共部分子层和汇聚子层,实现HINOC 网络中的媒质接入控制和业务适配功能;PHY 层规定了传输信号的帧结构、信道编码以及调制技术。为了提高数据搬移效率,MAC 层的主要功能需要由硬件完成。本文介绍了一种基于具有自主知识产权的HINOC MAC 层协议的硬件加速协处理的设计。

1 HIMAC 体系架构及功能概述

1.1 体系架构

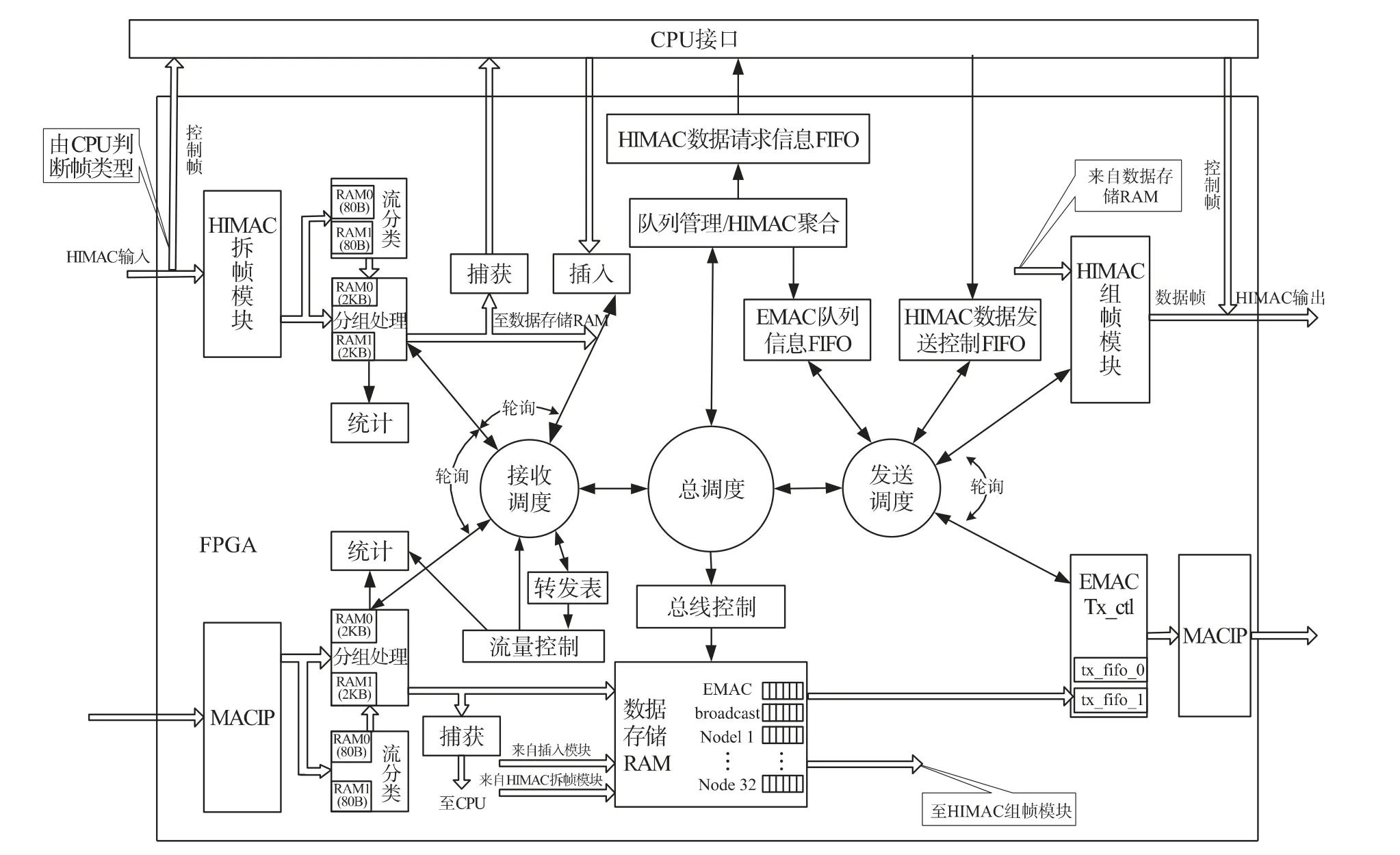

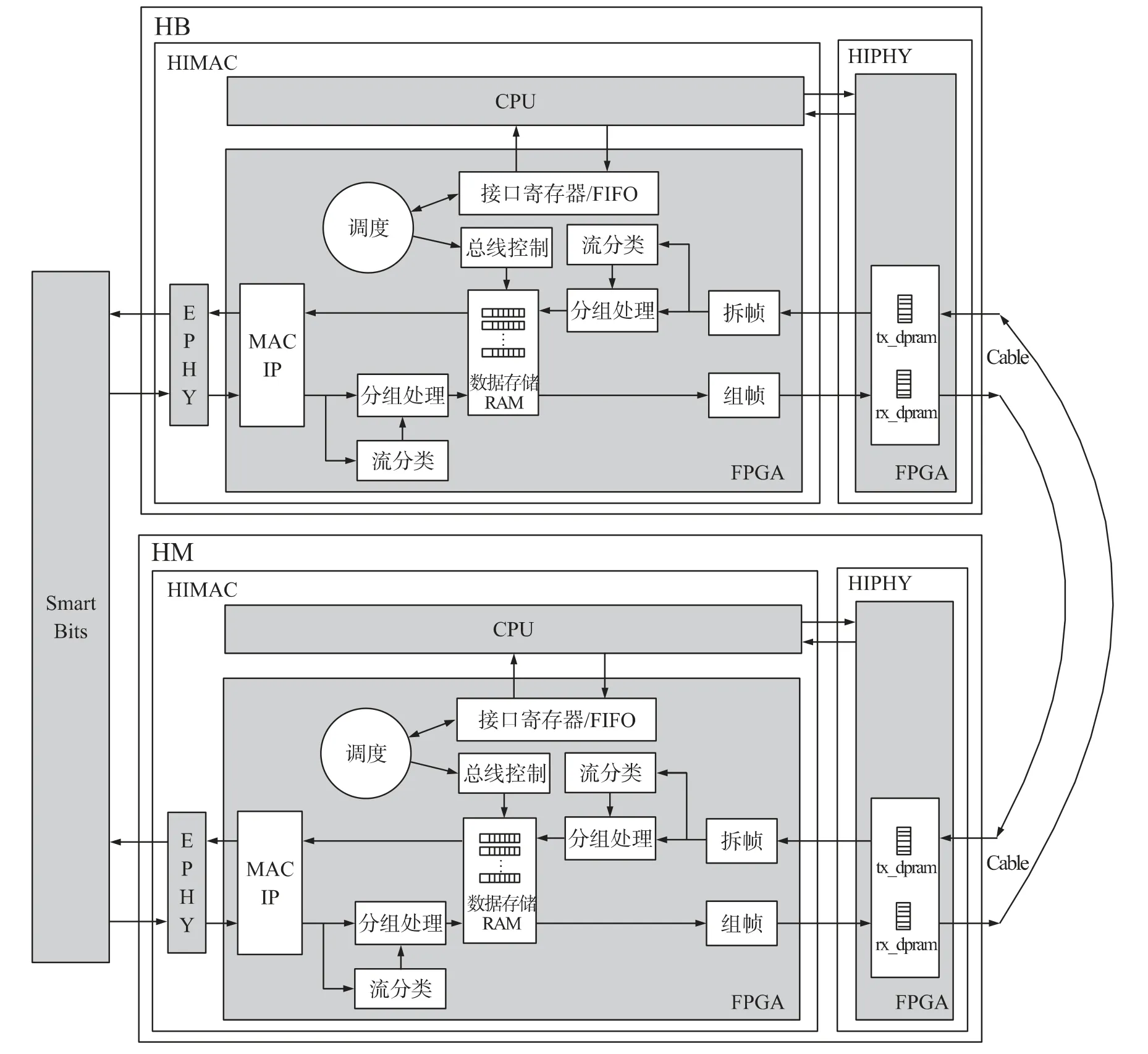

HIMAC 主要用于在CPU 软件控制下,完成EPHY(以太网PHY)和HIPHY(HINOC PHY)之间的数据传输和信息交互。主要分为拆帧、组帧、调度、EMAC 接口控制、流分类、插入捕获及数据缓存等模块。其详细内核结构如图1 所示。

图1 HIMAC 系统整体框图

1.2 功能概述

HIMAC FPGA 对外接口有3 种:一种是EMAC接口,完成以太网帧的接收和发送,实现与高层进行数据业务的交互;另一种是HIMAC 接口,完成HIMAC 帧的组帧和拆帧,实现HINOC 网络内部的数据传输;第3 种是CPU 接口,实现CPU 与HIMAC之间数据帧及控制帧的传输。

EPHY 和HIMAC 之间的数据处理流程比较简单,它们之间交互的信息只有EMAC 数据帧,直接和HIMAC 进行数据传输。其数据处理流程是:当EPHY 有以太网数据时,EPHY 通过与EMAC 接口的信息交互把EMAC 数据搬移到EMAC 帧的接收缓存中实现EMAC 数据帧的接收;当HIMAC 中的EMAC 帧发送缓存中有以太网数据要发送时,通过EMAC 接口与外部EPHY 的信息交互实现EMAC 数据帧的发送。

HIPHY 交给HIMAC 处理的帧有两种类型,即数据帧和控制帧。当HIPHY 的发送缓存中有HIMAC 帧要发送时,HIPHY 首先会产生中断触发中断服务程序,CPU 执行中断处理程序,读取HIMAC 帧的帧头信息并对该帧进行判断,如果是控制帧则交给CPU 处理,如果是数据帧,则从HIPHY的发送缓存直接搬移到HIMAC 的接收缓存中。同理,交给HIPHY 的帧也有两种类型,当交给HIPHY的帧是控制帧,则由CPU 直接写到HIPHY 的接收缓存中,如果是数据帧则从HIMAC 的发送缓存搬移到HIPHY 的接收缓存中。

2 关键模块功能介绍

由于HIMAC 硬件协处理器承载着以太网帧与HINOC 帧之间数据的交换、转发及传输功能,因此,不同业务的实现、不同类型帧之间的转换及调度、转发功能是整个HIMAC 的核心。

2.1 流分类及分组处理模块

流分类模块负责按照规则表的要求对流进行规则匹配。流分类模块可在数据帧内识别出IP 帧头的位置以及IP 上层协议(如IGMP,ICMPv6,TCP,UDP)头的位置;基于这些帧头的位置,规则表规定了需要进行匹配操作的关注窗口、匹配的操作值、匹配后要进行的动作等信息,流分类模块用关注窗口从数据帧中取出值与各条规则对比,得到需要对该数据帧进行的操作;以指令码的形式送出。流分类的指令的内容包括:指定优先级、重定向(包含拷贝重定向)到CPU、丢弃包、插入、修改、删除字段(最长32 bit)。

流分类对以太网数据包过滤和分类后,得到分类结果,即指令码,分组处理模块负责执行这些指令码,由此实现诸如访问控制、QOS 处理、IGMP Snooping 等相应的功能。分组处理模块需要完成的功能包括:控制EMAC 分组的正确接收、执行流分类模块给出的指令、提取帧的源目的地址,帧长,VLAN 号等信息、把分组处理的结果告知统计模块及实现帧数据在内部总线上的正确搬移等功能。

2.2 组帧拆帧模块

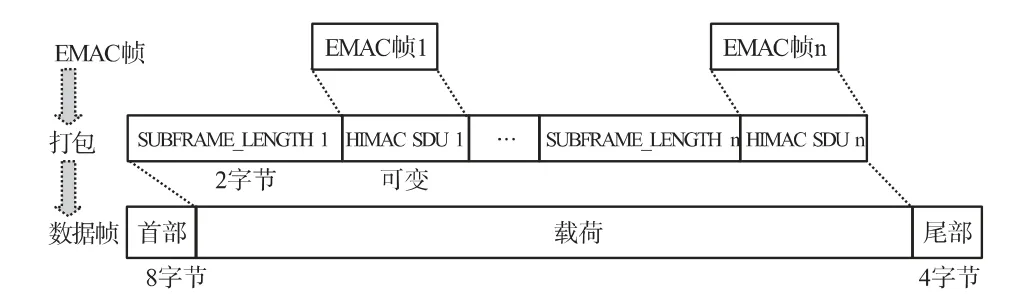

组帧模块通过与调度模块和内部总线模块的信息交互把要发送的上层数据业务根据打包规则封装成适合在HINOC 网络中传输的HIMAC 帧格式,然后通知SLAVE 接口将该数据帧发送出去。而HIMAC 拆帧模块则是将封装在HIMAC 帧中的EMAC 帧拆分出来。图2 是组帧过程示意图,拆帧过程与之相反。

图2 HIMAC 组帧示意图

2.3 调度模块和转发表模块

调度模块是HIMAC 协处理器内部的核心模块之一,在整个HIMAC 中起着重要的作用。它连接着转发表模块、队列管理模块、内部总线控制模块、分组处理模块、HIMAC 数据发送控制FIFO 以及捕获和插入模块等,在这些模块之间进行信息的控制、传递,最终有序、正确地完成EMAC 帧的接收和发送、HIMAC 帧的组帧和拆帧等工作。调度模块可分为6 个部分:接收调度模块、发送调度模块、总调度模块以及用来缓存数据的接收调度FIFO、发送调度FIFO 和调度结果FIFO。

转发表模块分为单播转发表模块和组播转发表两种。单播地址转发表的主要功能为:根据接收调度模块传来的单播EMAC 帧的源MAC 地址、目的MAC地址、源端口号、VLAN 号(源端口VLAN_ID)以及VLAN 有效指示信息进行学习和查表操作,查表成功则将查表得到的目的端口号以及接收到的VLAN 信息输出给接收调度模块,否则,指示查表失败。同时,为了使地址表的表项能够持续更新,设置5 min 的老化时间,若一个表项的老化时间到达,则被认为是陈旧表项,从地址表中删除。而组播转发表则是由CPU通过软件的方式来完成组播转发表的维护和更新。其中HIMAC 硬件协处理器完成两个功能:一是从CPU 接口寄存器实时读取软件组播表信息,建立和更新硬件组播转发表;二是根据调度器输入的组播目的地址查找组播转发表实现组播数据流的转发。

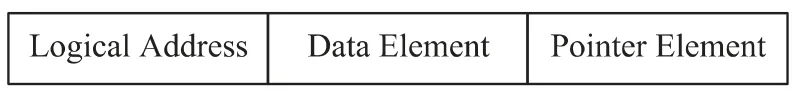

2.4 队列管理模块

由HINOC 网络组网方式可知,HB 节点一端连接千兆以太网,另一端通过一根同轴电缆连接HINOC 接入网。由于采用了TDM/TDMA 方式每个HINOC 接入网最多可包含32 个HM 节点,各个节点之间都可以相互通信,类似于一个32×32 的交换矩阵。系统采用了共享存储式的交换结构,交换数据以队列的方式存储在共享存储器中。在频繁的数据出队和入队过程中,需要一个专门的队列管理模块来管理,更新和维护存储器中的数据队列。整个队列管理的实现是以对每个链表节点的操作为基础实现的。每个链表节点由数据部分和地址指针部分构成,如图3 所示。

图3 链表节点结构

2.5 插入捕获模块

在设计中,HINOC 网络能够支持IGMP、MLD、DHCP 等协议,而这些协议报文必须交给CPU 进行处理,因此在HIMAC 中设计了捕获模块,用于将需要交给CPU 处理的报文捕获给CPU。为了实现的简易性,设计为从总线上捕获数据。捕获的数据帧分为两类:重定向到CPU 的数据帧及复制到CPU的数据帧。

当CPU 产生(或者是转发)的数据帧需要由HIMAC 或EMAC 端口发送时,就需要将这些数据帧插入到HIMAC 内部,然后让这些数据帧和普通的数据帧一起进行调度、入队,出队等操作,为此,设置了插入模块作为CPU 的数据帧插入到HIMAC 内部的通道。可以将插入模块作为接收调度模块进行轮询操作时的第三个外部接口,帧从CPU 出来,经调度模块调度,就可以直接入队。

3 功能仿真及FPGA 验证

3.1 功能仿真

整个HIMAC 硬件协处理器采用Verilog HDL 语言实现。为验证其逻辑功能的正确性,编写了CPU、HIPHY 及以太网帧产生模块等BFM。规定其详细功能列表,建立验证平台,制定相应的测试用例。仿真验证采用可回归的自动报结果的检验手段。在ModelSim 6.3 环境下通过逻辑仿真。结果表明,能够实现预定的各种功能。

3.2 FPGA 验证

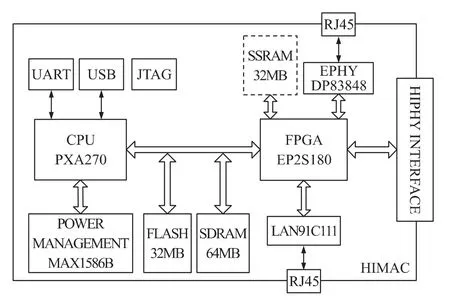

3.2.1 验证平台

FPGA 的验证平台主要包括Altera 公司StratixⅡ系列的芯片EP2S180,PXA270 处理器及一些接口和存储模块等。验证平台硬件框图如图4 所示。

图4 硬件验证平台

3.2.2 验证方案

HINOC 系统中,影响系统性能的因素主要有Pd周期及Pd 帧前/后保护期、帧间隔、调试方式(64/128/256QAM)[7-8]、MAP 规划的不同等。设计中Pd周期、Pd 帧前/后保护期和帧间隔的基本单位为1/64 μs,这里是以HIPHY 的时钟频率(64MHz)为基准。针对HINOC 系统的测试,本文设计了如图5 所示的测试方案。

方便起见,图5 只给出了HIMAC FPGA 内部的部分功能模块。该测试方法可通过CPU 配置HINOC系统寄存器实现,CPU 将HIMAC FPGA 和HIPHY FPGA 的模式寄存器置0,选取正常工作模式。HINOC 系统中,下行方向(HB→HM):HB 将收到的EMAC 帧进行组帧后送往HIPHY 的发送缓存,然后在MAP 周期内下行时隙时将组好的数据帧经HIPHY 发送至HM,HM 将数据拆帧后,由EMAC 口发回SmartBits 测试仪;上行方向(HM→HB):HM 将收到的EMAC 帧完成组帧后向HB 请求信道预约,然后在HB 为其分配发送时隙内将数据发送至HB,HB对数据拆帧后,由EMAC 口发回SmartBits 测试仪。

图5 系统验证方案

3.3 实验结果

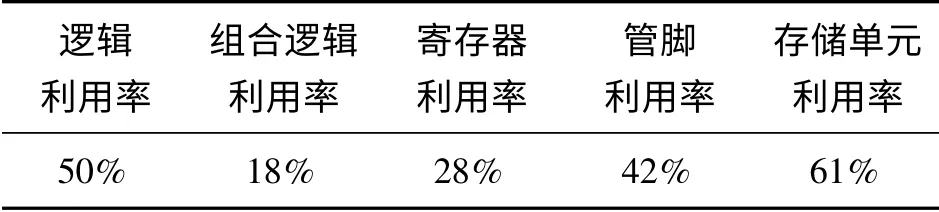

使用Altera 公司的Quartus Ⅱ9. 1 工具对HIMAC 协处理器代码进行综合,目标器件为EP2S180F1020I4,综合后的资源占用情况如表1所示。

表1 FPGA 资源统计

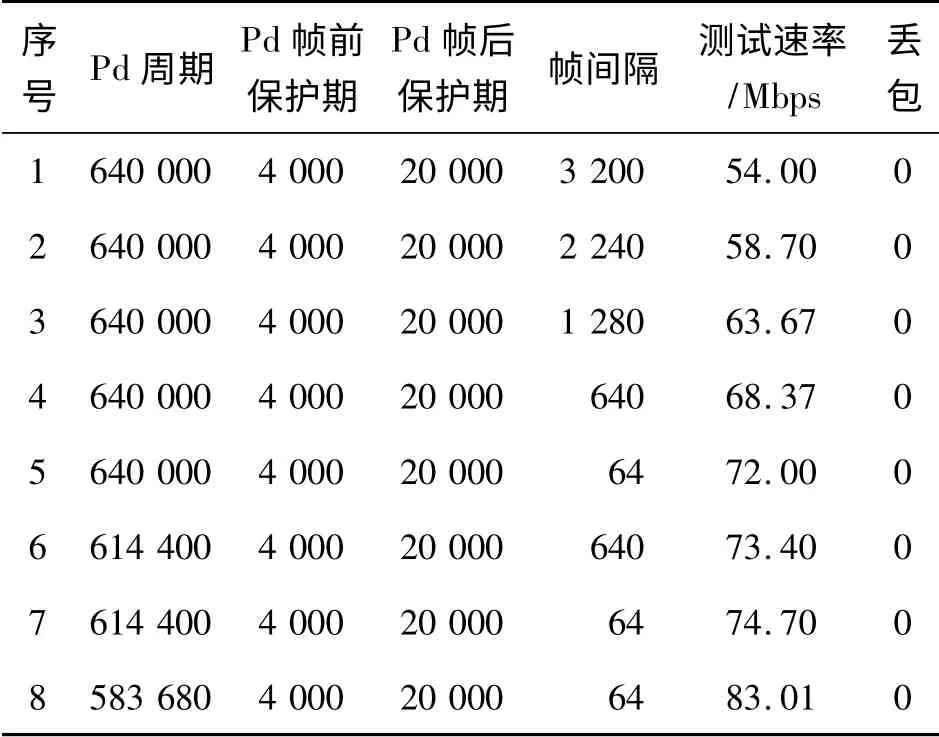

为测试系统的性能,对图5 所示系统进行下行传输测试和双向传输测试。

(1)HINOC 系统下行传输测试

下行传输时,MAP 规划中仅仅存在下行时隙和MAP 帧,而不存在预约时隙和上行时隙。表2 给出了Pd 前后保护期分别为4 000 和20 000(接近理论最小保护时间)、256QAM 调制方式下的HINOC 系统下行传输的测试结果。

表2 系统下行测试

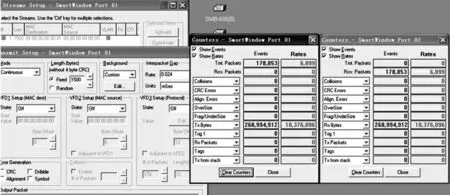

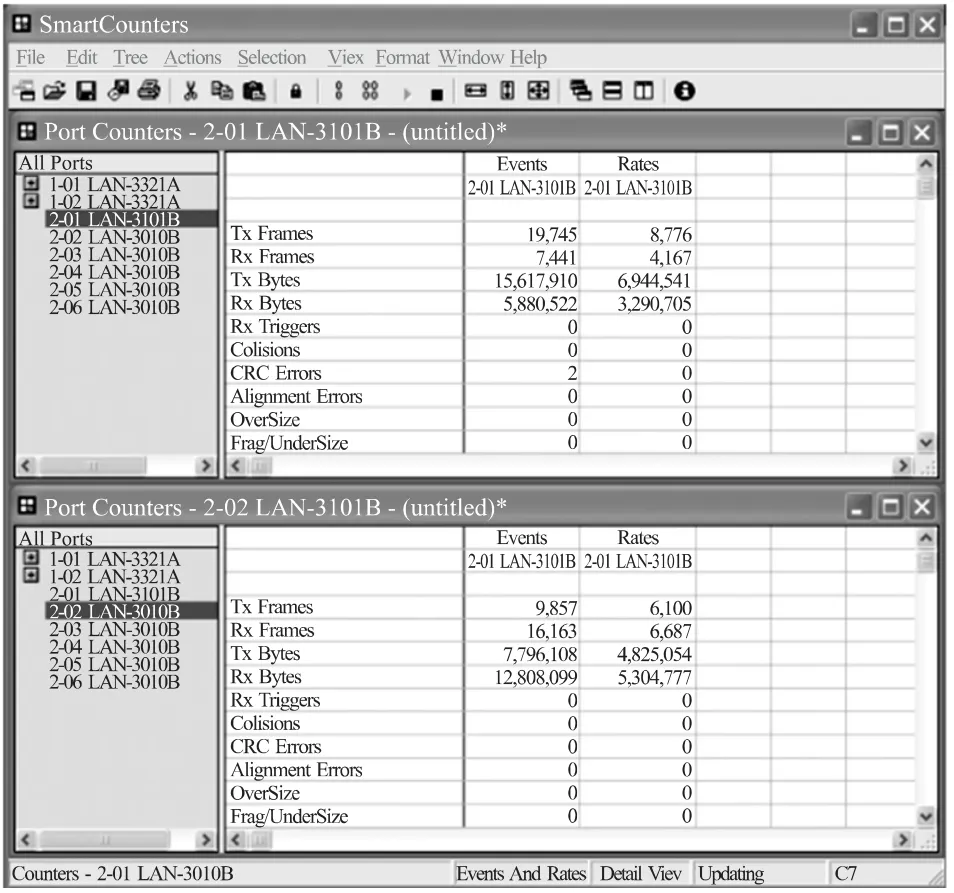

表2 所测为无丢包情况时的HINOC 系统下行极限传输速率。图6 给出了利用SmartBits 200 测试仪测得的表2 中序号8 情况时的测试结果。

图6 系统下行测试结果

可见,在EMAC 帧间隔为0.002 4 ms,帧长度为固定1 500 byte 情况下,所统计的发送和接收的数据一致,且无出错,网络的单向数据传输速率可达83 Mbit/s,考虑到在每个MAP 周期内,CPU 需要处理控制帧、信令帧、生成MAP 规划等,此速率实际上已接近该情况下的极限速率。

(2)HINOC 系统双向传输测试

双向传输时,MAP 规划内包含上/下行时隙、预约时隙和MAP 帧。图7 给出了Pd 周期为786 432,Pd 前/后保护期分别为6 400 和20 000,上下行切换间隔20 000,帧间隔为2 000 时,利用SmartBits 600测试仪得到的测试结果。

图7 系统双向传输测试结果

由图7 可知,测得的HINOC 系统下行传输速率为42 Mbps,上行传输速率为26 Mbps,测试结果达到设计要求。

4 结论

提出了一种具有自主知识产权的HINOC 系统MAC 层硬件协处理器的设计方案。实验结果表明,该设计满足HINOC 系统对各种数据帧处理速率的要求,同时,一些原本由软件完成的功能通过硬件来实现,降低了CPU 的负荷,同时也提高了数据帧处理的效率。

[1] 国家广播电影电视总局广播科学研究院,北京大学,西安电子科技大学.高性能同轴电缆接入网(HINOC)物理层传输模式及媒质接入控制协议(面向NGB 电缆接入技术的建议方案).2010 年.

[2] 赵翠,张诚,李红滨,等.HINOC 系统硬件架构和实现方法[J].广播与电视技术,2011,(10):39-42.

[3] 欧阳峰,崔竞飞HINOC 技术概述和进展[J].电视技术,2011,(12):11-13.

[4] MoCA MAC/PHY Specification V1.0[S]. Multimedia Over Coax Alliance,2006.

[5] HomePlug AV Specification V1.0[S].HomePlug Power Alliance,2005.

[6] Cui Xiaoxin,Long Jinkai,Sun Bin,et al. A High Performance Baseband Transceiver IC for HINOC Communication System[C]//ICSICT2010,442-444,2010.

[7] Pfau T,Sebastian Hoffmann,Reinhold Noe.Hardware-Efficient Coherent Digital Receiver Concept with Feedforward Carrier Recovery for M-QAM Constellations[J]. Journal of Lightwave Technology,2009,27:989-999.

[8] Adnan Zafar,Zaineb Farooq S. Implementation and Analysis of QPSK &16QAM Modulator & Demodulator[C]//ICAST2008,64-68,2008.