基于SystemVerilog 的SRAM 控制器IP 核验证*

2012-12-22周德新金志威赵学娟

周德新 ,金志威,王 鹏,赵学娟

(1.中国民航大学航空自动化学院,天津300300;2.中国民航大学天津市民用航空器适航与维修重点实验室,天津300300)

随着芯片设计规模及复杂度的不断增加,验证工作在整个设计生命周期内占据着相当大的比重。传统的验证方法针对待验证设计编写直接测试激励,采用定向的测试方式,查找设计中的漏洞。此种方法凭借其直观且易于实现等优点被广泛采用。然而对于复杂的、多功能的设计,采用传统验证方法很难编写各种测试去覆盖所有的特性并找出漏洞。因此能否对设计进行全面而有效的验证,是验证人员所面临的主要问题[1]。

SystemVerilog 作为新一代的设计验证语言,结合了现代的设计和验证环境并将硬件描述语言(HDL)与高级验证语言(HVL)结合在一起,为高度复杂的芯片设计提供了强大的设计和验证保证[2]。SystemVerilog 支持约束随机的产生、覆盖率统计分析以及断言验证。其最突出的优点在于面向对象的编程结构,有助于采用事务级的验证和提高验证的重用性[3]。由于具有诸多优点,SystemVerilog 是被设计和验证工程师广泛使用的语言之一。

本文采用基于SystemVerilog 的验证方法对SRAM 控制器IP 核进行功能验证。通过分析覆盖率数据并对比传统的验证方法,基于SystemVerilog 的验证方法能够更加快速且全面的完成对设计的验证。

1 SRAM 控制器IP 核

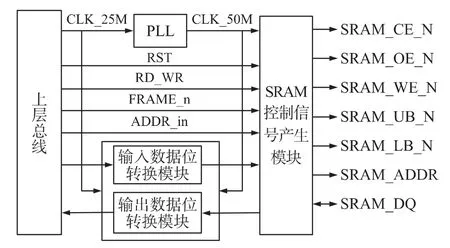

本文的验证载体为一段VHDL 编写的SRAM控制器IP 核。其中SRAM 选用的是ISSI 公司的IS61WV102416BLL 高速异步16bit 静态RAM 存储器。SRAM 控制器IP 核的系统框图如图1 所示。

图1 SRAM 控制器系统框图

由图可知,系统共分为4 个模块,分别为PLL锁相环模块、输入数据位转换模块、输出数据位转换模块和SRAM 控制信号产生模块。其中PLL 模块主要用于生成双倍于上层总线的时钟,以便于对SRAM 地址和数据采样。由于SRAM 的数据端口是16 bit,与上层数据位数不匹配,因此在进行读写操作时,需要通过输入和输出数据位转换模块对读写数据进行位数转换。SRAM 控制信号产生模块通过接收复位信号(RST)、读写控制信号(WR_RD)、周期构成信号(FRAME_N)和地址信号(ADDR_in),生成SRAM 的控制、地址和数据信号。

下面根据SRAM 控制器IP 核的设计需求,使用伪代码的形式列出各功能项。此种描述方法与文字描述相比能够更加简单明了地表达出各项内容,有助于设计人员与验证人员的交互。其中低有效信号以!SIGNAL#出现时有效,以SIGNAL#出现时无效。<-符号左边为结果,右边为条件。

1.All State==one-hot coding

2.(!SRAM_CE_N#* !SRAM_WE_N#)<-[!SRAM_CE_N#* !SRAM_WE_N#* (cmd=write)]

3.(!SRAM_CE_N#* !SRAM_OE_N* !SRAM_WE_N#)<-[!SRAM_CE_N#* SRAM_WE_N#* (cmd=read)]

4.SRAM_ADDR* SRAM_DQ delay 1 clock(cmd=write)

5.DATA_out delay 2 clock(cmd=read)

2 基于SystemVerilog 的验证方法

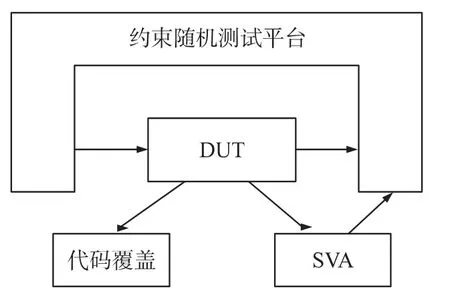

基于SystemVerilog 的验证环境如图2 所示[4]。此验证环境通过约束随机测试平台对待测设计加载随机输入激励,使用验证工具分析,获取代码覆盖率数据。同时使用SVA 对待测设计进行监控,通过仿真获得功能覆盖率数据。

图2 基于SystemVerilog 的验证环境

2.1 约束随机测试平台

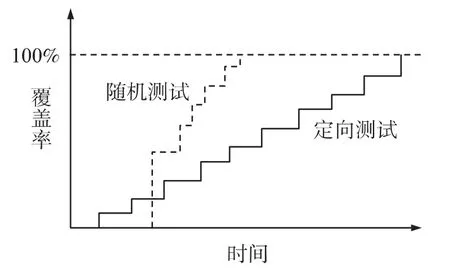

由于设计复杂度的不断提高,待测设计的功能也越来越多,这样在使用直接测试方法编写测试激励时很难覆盖到所有的功能。而随机测试可以比传统的直接测试更有效,通过指定约束条件,在特定区域内随机产生输入激励,大大增加了测试的覆盖范围。图3 显示了两种测试方法随时间的进度比较,由图可知,虽然随机测试在验证前期耗费时间较长,而随着验证工作的深入,可大幅度减少验证时间[5]。

图3 约束随机测试与定向测试随时间的进度比较

使用SystemVerilog 编写测试平台时可先定义一个带有随机变量和约束的类,然后对该类进行调用。在类中可把变量的类型声明为rand 或randc 类型并可对其添加约束条件[6]。下列是一段产生随机数据和地址的测试代码,其中地址变量的值大于8 且小于16。

class add_data

rand logic signed[7:0]addr;

randc logic signed[31:0]data;

constraint d {addr>8;

addr<16;}

endclass

2.2 SVA 断言

在当今流行的验证技术中,基于断言的验证ABV(Assertion Based Verification)凭借着其在更短的时间内找到设计中存在的功能缺陷的优点,迅速成为了验证流程中的关键与必要的手段[7]。在验证环境中增加断言来加强验证环境的能力。

作为SystemVerilog 的重要组成部分,SVA(SystemVerilog Assertion)是一种描述性语言,可以完美地描述和控制时序相关的问题,而且语言本身简洁易读容易维护,使得设计人员和验证人员可以快速地对复杂设计的验证行为进行定义,是使用最广泛的验证方法之一。SVA 提供了若干个内嵌函数来测试特定的设计情况,并且提供了一些构造来自动收集功能覆盖数据。通过分析功能覆盖数据,可以分析出待测设计在功能上还有哪些缺陷[8]。

以SRAM 控制器IP 核的第2 条功能项为例,使用SVA 对此功能点进行监控,如下所示。

sequence sram_write;

($fell(FRAME_N)&&(!WR_RD));

endsequence

property p_write;

@(posedge CLK_66M)sram_write|=>(!SRAM_CE_N &&!SRAM_WE_N);

endproperty

a_write:assert property(p_write);

c_write:cover property(p_write);

2.3 覆盖率

覆盖率可分为代码覆盖率和功能覆盖率两种。代码覆盖用来检查设计中的哪些代码在验证期间被执行过。常见的代码覆盖有语句覆盖、分支覆盖和表达式覆盖等。100%的代码覆盖率只能说明验证过程中执行了所有的源代码,却不能说明验证的正确性和完整性[9]。计算代码覆盖率的公式为

式中,H(Hit)是击中覆盖点;A(Active)是有效覆盖点。

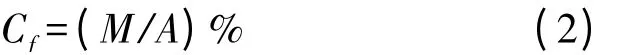

功能覆盖是对代码覆盖的补充。功能覆盖用来衡量验证对象是否实现了设计者所期望的功能。功能覆盖中的覆盖点由验证者指定,需要更高的抽象级,即需要编写覆盖率模型。SystemVerilog 语言的结构化,易于构建功能覆盖率模型,并且可以被SystemVerilog 仿真工具有效地执行。在SystemVerilog语言中,功能验证主要包括两种手段:Cover Property和Covergroup。Cover Property 适用于在设计中采样基于时钟信号的数据。一般用在Block 中的低层次功能覆盖和在接口中的较高层次覆盖。Covergroup可以用在Module、Program、Interface 和Class 中[10]。计算功能覆盖率的公式为

式中,M(Match)是属性成功的次数;A(Attempts)是属性被尝试检验的次数。

3 验证结果

通过对SRAM 控制器IP 核搭建基于System-Verilog 的验证环境,并在QuestaSim 10.0 验证工具上实现,获取代码覆盖率和功能覆盖率数据

表1 列出了使用传统验证方法和基于System-Verilog 的验证方法获取的代码覆盖率数据。从表中各类数据可以看出,基于SystemVerilog 的验证方法能够明显的提高各覆盖率,提升验证质量。

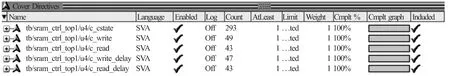

图4 所示为工具仿真50 μs 后的Cover Directives窗口显示的覆盖率数据。图中,Count 列表示断言在仿真时间内被激活的次数,Cmplt%和Cmplt graph 列分别表示断言指令的覆盖率和覆盖率的图形化显示。由图可知,各功能均被实现,且覆盖率达到100%。此种通过SVA 断言技术的方法在功能验证上比传统分析波形的方法更加直观且节省时间。

表1 覆盖率数据比较

图4 功能覆盖率

4 结论

本文介绍了基于SystemVerilog 语言的验证方法,并使用此方法对SRAM 控制器IP 核进行验证。通过对比分析代码覆盖率数据,可以看出了基于SystemVerilog 的验证方法比传统的验证方法验证质量更高,并结合SVA 断言对设计进行监控,可直观快速的发现设计中的缺陷,提高验证效率。

[1] Janick Bergeron,Eduard Cerny,Alan Hunter,et al. Verification Methodology Manual for SystemVerilog[M].Springer,2005.

[2] Stuart Sutherland,Simon Davidmann,Peter Flake. SystemVerilog for Design[M].Springer,2006.

[3] Mike Mintz,Robert Ekendahl. Hardware Verification with System-Verilog[M].Springer,2007.

[4] Srikanth Vijayaraghavan,Meyyappan Ramanathan,A Practical Guide for SystemVerilog Assertions[M].Springer,2005.

[5] Chris Spear.System Verilog for Verification[M].Springer,2006.

[6] Sasan Iman.Step-by-Step Functional Verification with SystemVerilog and OVM[M].Springer,2008.

[7] Eduard Cerny,Surrendra Dudani,John Havlicek,et al. The Power of Assertions in SystemVerilog[M].Springer,2010.

[8] SystemVerilog 3.1a Language Reference Manual. Accellera’s Extensions to Verilog[M].Accellera,Napa,California,2004.

[9] Janick Bergeron. Writing Testbenches Using SystemVerilog[M].Synopsys,Inc,2006.

[10] Andrew Piziali.Functional Verificational Coverage Measurement and Analysis[M].Netherlands:Kluwer Acadamic Publishers,2004.