基于FPGA 的高速数据采集系统的设计与实现*

2012-12-22常高嘉冯全源

常高嘉,冯全源

(西南交通大学微电子研究所,成都610031)

电子信息技术近些年来持续迅猛发展,通信信号的带宽已变得越来越宽,调制方式也从传统的模拟调制发展到数字调制、矢量调制,编码方式也在不断地趋于复杂化。为了满足对较宽频域范围内高频、瞬态信号细节的精确、实时检测分析,必须要有一种数据采集系统,这种系统必须具有高采样率、高分辨率,以便于对高速、复杂的信号进行快速的采样、存储、传输和分析。应用可编程门阵列FPGA 可使数据采集系统具有高度的灵活性,基于FPGA 的高速数据采集是现代测试系统中非常重要的一种数据记录与处理设备[3]。

本文设计了一种由AD、FPGA 和DSP 组成的数据采集系统,系统的采样精度为12 bit,采样率为100 MSPS。该系统主要用于对盲信号的分离及信号参数的识别。

1 系统结构

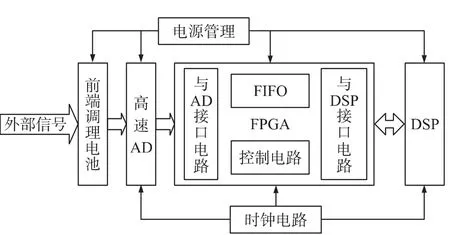

数据采集系统的原理框图如图1 所示。该系统使用的ADC 芯片为ADI 公司的AD9233,采样精度为12 bit,采样率为100 MSPS;FPGA 选用的是Altera 公司的CycloneⅢ系列EP3C16Q240C8;DSP为TI 公司的TMS320C6416,其最高主频为1 GHz。该数据采集系统主要由前端信号调理电路、模数转换电路、FPGA 电路和DSP 电路组成。

图1 数据采集系统结构图

模拟信号首先经过前端调理电路使其幅度转换成适合AD9233 处理的范围,并将单端信号转换成差分信号后输出给AD9233,AD9233 在采样时钟的控制下完成模数转换,然后FPGA 将ADC 量化后的信号寄存在FIFO 中,最后DSP 通过接口电路从FPGA 的FIFO 中读取数据并做后续的一些处理。整个系统中,DSP 起主控作用,它控制着FPGA 是否对AD 的输出数据进行寄存及是否从FPGA 的FIFO 中读取数据。

本高速数据采集系统的关键是前端调理电路的设计与实现。前端调理电路完成对输入信号幅度的调整,阻抗匹配,并把单端信号变成抗噪性更好的差分信号。前端调理电路的抗干扰能力、增益控制特性、频率特性、时延特性等是设计中需要重点考虑的因素,本设计中使用变压器模式和放大器模式来完成前端调理电路的设计。

2 设计实现

2.1 前端调理电路

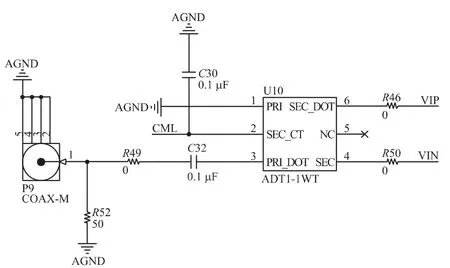

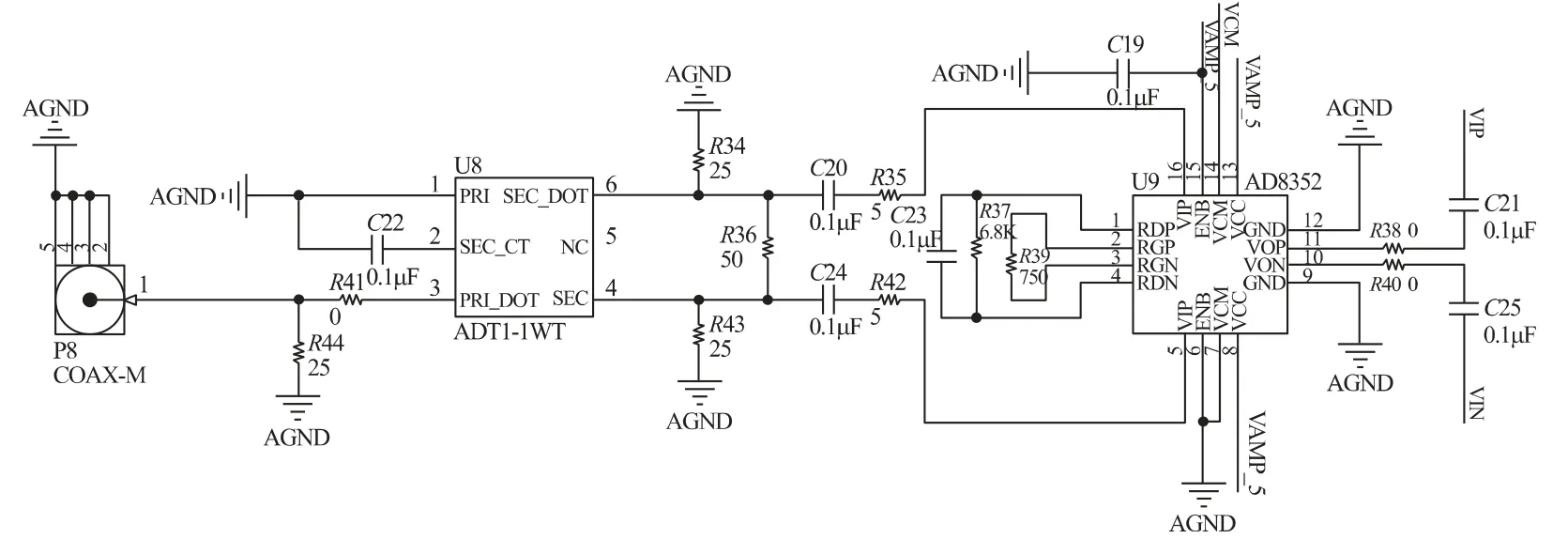

前端调理电路的作用是将模拟信号的幅度调整为适合ADC 芯片处理的范围,同时将单端信号转变成AD 需要的差分信号。本设计中采用了两种方法设计前端调理电路,一种是使用变压器,一种是差分放大器的方法。两种方式的电路如图2 和图3 所示。

图2 采用变压器分式的前端调理电路

图3 采用差分放大器方式的前端调理电路

两种方法各有优缺点,需要根据模拟信号的特点和设计目标来确定选择哪种处理方式。由于变压器是无源交流耦合器件,所以产生的噪声很小,只能将交流信号输出到ADC 芯片,同时它的通带平坦性和驱动能力差,无动态隔离能力,提高增益会降低AD 的模拟带宽。而放大器是有源器件,会产生较大的噪声,但是它的通带平坦性和驱动能力好,可以提高动态隔离,增益提高后对AD 的模拟带宽影响很小。通过分析变压器和放大器的特点,前端调理电路优先器件的选择可以总结为表1 所示。

表1 ADC 前端调理电路中变压器和放大器的性能对比

2.2 时钟电路

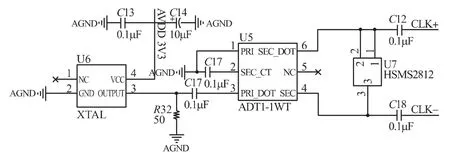

ADC 芯片的采样是在时钟的控制下完成的,所以时钟信号的质量对AD 的影响非常大,特别是高速、高分辨率ADC 或是中频欠采样时对时钟输入信号的质量尤为敏感。所设计的电路如图4 所示。

图4 系统的时钟电路

本设计用一个100 MHz 的有源晶振产生时钟源,然后用一个变压器将单端时钟信号转成差分信号后交流耦合到AD 的CLK+和CLK-引脚端,并在变压器的次级,靠近CLK+和CLK-引脚处跨接一组背对背肖特基二极管。这两个二极管可以将输入到AD 的时钟信号限制为约差分0.8 V 峰峰值。这样,既可以保留信号的快速上升和下降时间,还可以防止时钟的大电压摆幅馈通至AD9233 的其他部分,这一点对时钟的低抖动性能来说非常重要。

2.3 FPGA 程序设计

ADC 芯片输出数据的速度是100 Mbyte/s,而DSP 接口速度低于100 Mbyte/s,所以需要通过FPGA对数据进行缓存。FPGA 通过使用FIFO 的方法来完成数据的缓存。FPGA 的程序设计由Verilog 语言实现,主要由4 部分组成,与AD 的接口程序、与DSP 的接口程序、循环FIFO、控制器。控制器的作用是对DSP 发送的控制命令进行译码,然后控制循环FIFO的读和写状态;FPGA 与AD 的接口程序根据AD 的数据时钟输出信号将AD 输出的数据正确存入FPGA的FIFO 中;FPGA 与DSP 的接口程序根据DSP 的控制信号将地址总线和数据总线上的值传送给控制器,由控制器来对DSP 的命令进行译码。

设计完成后整体的系统实物如图5 所示。

图5 系统的整体实物图

3 PCB 设计及硬件电路的调试

3.1 PCB 设计

高速数据采集系统中,PCB 的设计也是非常关键的一方面。PCB 的设计的好坏决定走线上信号的质量。本设计中采用了以下方法来提供信号的质量。

①差分信号要走严格的等长差分线。差分线可以提高信号的抗噪性,减小外界对信号的干扰。

②电路中的数字地和模拟地分割开,最后在一点通过0 Ω 电阻连接起来,这样做能够减小数字地中的高频杂波对模拟电路的影响。

③对晶振部分的电路做包地处理。时钟信号是ADC 转换中的又一关键特性。为保证时钟的频谱纯度,设计中将晶振部分的电路做了包地处理,这样可以很好地降低外界对晶振的干扰。

④AD 的10 bit 数字输出到接口部分的各条走线要等长。等长线可以保证AD 输出的各个bit 位的数字信号到达接口处的延时相同。

3.2 硬件电路的调试

本电路的调试分3 个阶段完成,电源电路的调试、前端调理电路的调试和数字电路的调试。

(1)电源电路的的调试 首先焊接各个电源芯片,并测试电源芯片输出电压的纹波。

(2)前端调理电路的调试 本设计中的前端调理电路有变压器和放大器两种模式,需测试两种模式适合处理的输入信号。经调试发现,变压器模式适合处理信号幅度较大噪声大的输入信号,而放大器适合处理信号幅值小的输入信号。

(3)数字电路的调试 该部分完成对AD 控制电路的调试,如AD 差分输入的最大峰峰值、是否使用AD 内的占空比稳定器、各bit 位的数字输出到接口处的延时情况等。

4 系统测试

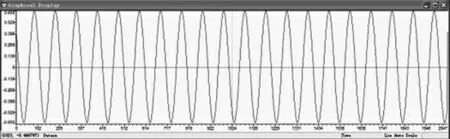

系统测试选用的信号源是Tektronix 公司的AFG3252,选用的是频率是1 MHz,峰峰值为5 V 的正弦波。通过在DSP 中编程读取FPGA 的FIFO 中的数据,得到的波形如图6 所示。可以看出DSP 得到的数据稳定且基本上没有杂波,为后续的数据处理奠定了良好的基础。

图6 DSP 中读取到的系统处理完成的波形

5 结论

本文完成了由AD、FPGA 和DSP 组成的高速数据采集系统设计。本文对硬件电路中的前端调理电路和时钟电路做了详细的介绍。前端调理电路采样了变压器和放大器的两种设计方法,根据输入信号特性选用不同的设计电路;时钟电路采用差分信号以减小外界的干扰,同时还在时钟输入端加了背对背肖特基二极管以增加稳定性。用Verilog 语言完成了FPGA 部分的控制电路、FIFO、FPGA 与AD 和DSP 的接口程序设计,完成了对数据的缓存,最后在DSP 中可以稳定地读取到ADC 量化后的波形。

[1] Zhang Baofeng,Wang Ya,Zhu Junchao.Design of High Speed Data Acquisition System Based on FPGA and DSP[C]//Artificial Intelligence and Education(ICAIE),International Conference,2010:132-135.

[2] Xiao Jinqiu,Wang Xinglong,Feng Yi.High-Speed Real-Time Data Acquisition System Based on FPGA[C]//Electronic Measurement& Instruments,9th International Conference,2009:378-391.

[3] 何鹏.基于FPGA 的高速数据采集系统[J].机械与电子,2010(11):96-97.

[4] 肖金球,刘传洋,仲嘉霖. 基于FPGA 的高速实时数据采集系统[J].电路与系统学报,2005,10(6):128-131.

[5] 李和平,王岩飞.高速数据采集模块的设计和实现[J].电子器件,2008,31(4):1245-1248.

[6] 何寅生,高俊,娄景艺.基于SOPC 的PCI 数据采集卡的设计与实现[J].电讯技术,2009,49(7):77-80.

[7] 贾龙,林岩.基于DSP 和FPGA 的高速数据采集系统的设计及实现[J].电子测量技术,2007,30(5):95-97.

[8] 王建秋.基于FPGA 的高速数据采集系统的电路设计[J]. 潍坊学院学报,2011,11(4):16-19.

[9] 江明.基于FPGA 的高速数据采集系统的研制[D].哈尔滨:哈尔滨理工大学,2011.

[10] 葛远香,金燕,胡开明. 基于FPGA 高速数据采集系统控制电路的设计[J].浙江工业大学学报,2009,37(1):96-99.

[11] 李少东.数据采集系统的通道电路设计[J]. 电子质量,2012(3):15-16.

[12] 周晓玲,沈恺煜,吴校生,等.基于DSP 高速外扩FLASH 的高精度数据采集系统[J].电子器件,2012,35(1):111-114.