基于分布式算法的有限长单位冲激滤波器

2012-12-01王和明路文龙张启亮

王和明,路文龙,张启亮

(空军工程大学导弹学院,陕西 三原 713800)

0 引言

目前实现 FIR(Finite Impulse Response,有限长单位冲激响应)滤波器的器件主要有三种:专用芯片、DSP(Digital Signal Processor)和 FPGA (Field Programmable Gate Array)。专用芯片实现的滤波器存在功能单一的缺点;使用DSP实现滤波器由于程序顺序执行,难以实现高速、高阶的滤波器[1];FPGA能够并行执行逻辑运算,并且可通过增加逻辑单元的方式使运算速度不受阶数增加的影响,在设计高速、高阶的滤波器时受到越来越多技术开发人员的关注。

通过FPGA实现FIR滤波器时,使用DSP运算结构只是在利用FPGA的乘法器资源来换取滤波器速度的提升,这对实现高阶滤波器非常不利。DA算法 (Distributed Arithmetic,分布式算法)采用不同于通用DSP的乘累加结构,使得滤波器运算速度不随着阶数的增加而降低,同时降低了进行滤波运算所需的资源[2]。本文在对DA算法分析研究的基础上,设计了基于分布式算法的有限长单位冲激响应滤波器。

1 分布式算法原理及滤波器结构

1.1 传统分布式算法

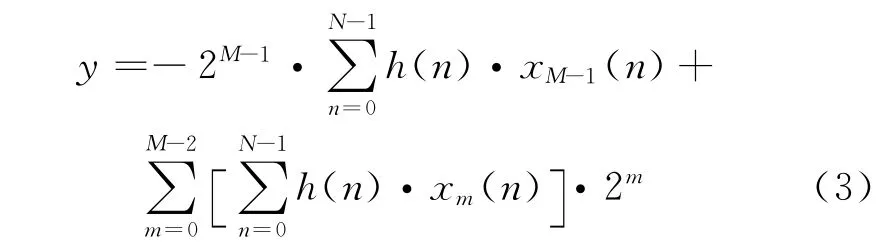

DA算法作为一项重要的FPGA技术,广泛地用于计算相关、DFT以及滤波器等乘累加(Sum of Products,SOP)问题中[3]。如式(1)所示,N -1表示对数据的总延迟时钟数。

式(1)中,h(n)为 N 阶滤波器的第n 个系数,x(n)为第n个抽头对应的数据。设x(n)是位宽为M比特的二 进 制 数,以 二 进 制 补 码 形 式 表 示:xM-1(n)xM-2(n)…x1(n)x0(n),其 中 xM-1(n)为 符 号 位,x0(n)为最低位,则x(n)可表示为:

将式(2)表示的x(n)代入式(1)并整理,得

图1 DA算法实现原理Fig.1 Principle of distributed arithmetic

1.2 改进分布式算法

采用DA算法进行滤波器设计主要消耗FPGA的存储器资源,且随着滤波器阶数的增加存储器的容量成指数增长[4],显然FPGA将越来越难以实现。如果将高阶滤波器拆分为多个阶数较少滤波器的级联,可有效减少FPGA的查找表的资源占用。对于通过L个K阶滤波器级联实现的N阶滤波器,设滤波器的位宽为M,则减少的查找表资源为(2N-L·2K)×M。

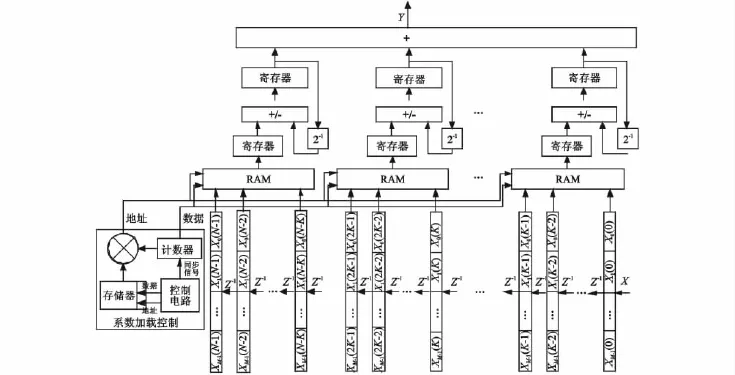

另一方面,DA算法通过将数据流的串行运算变为数据位的串行计算,在需要较高精度时,位宽一般很长,仍然会导致滤波器工作速度的大幅下降。这可以通过增加DA算法的并行度来解决。图2为采用全并行的方式实现DA算法,将滤波器所有抽头对应的数据位同时作为查找表的输入地址,将输出结果进行移位相加,同时加入流水线寄存器,理论上可实现一个时钟输出结果。这只是实现DA算法时追求计算速度的一种极端情况,实际设计需根据对速度的具体要求增加DA算法的并行度以提高运算速度。这也体现了程序设计中的资源与速度互换原则。

图2 全并行DA算法实现原理Fig.2 Principle of distributed arithmetic in parallel

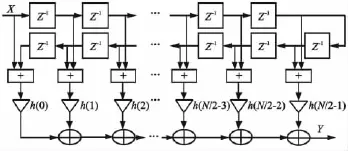

1.3 滤波器结构

FIR滤波器不含反馈环节具有稳定性,且能够保证线性相位关系,因而应用十分广泛。滤波器实现结构如图3所示。

图3 FIR滤波器实现结构Fig.3 FIR filter structure

在通过查找表实现滤波器系数与输入数据的乘法运算之前,先将具有相同滤波器系数的数据相加,然后乘以滤波器系数。此处利用了滤波器系数的对称性,增加一个数据位以及N/2个加法器,却减少N/2个乘法器。滤波器结构中的乘累加结构采用分布式算法实现。

2 通用实时滤波器

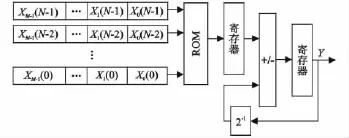

文中采用改进的分布式算法,以有效降低实现FIR滤波器占用的资源。首先将分布式算法中存储系数所有乘积结果的只读存储器变换为随机存储器并配以系数加载电路,实现滤波器的通用性;然后通过乒乓操作方式解决系数加载引起的实时性问题,以便在实时系统中应用。

2.1 通用滤波器

FIR滤波器系数决定其实现的滤波特性,因此通过对同一个滤波器结构加载不同的滤波器系数即可实现滤波功能的改变[5]。如图4所示,将DA算法实现滤波器乘法中的ROM变换为RAM,同时开放RAM的写数据端与写地址端给数据加载电路,可实现滤波器系数的加载,进而实现通用滤波器。

图4 通用FIR滤波器实现原理Fig.4 Principle of universal FIR filter

从图4中可以看到,系数加载控制电路中需要配置存储器用以存储滤波器系数,而存储器容量的大小直接影响滤波器能够实现多少种滤波特性。如果仍然按照DA算法需要的所有二进制结果进行存储,将会占用大量的存储资源。此处通过加入乘法器与计数器,令计数器的输出只同时作为乘法器的输入值和RAM的地址,在对存储的滤波器系数与数据的所有乘积结果计算出来的同时存入相应地址的RAM中,从而实现对DA算法中RAM数据的加载,这样可以在实现通用滤波器的同时极大地降低对存储器的需求。如果需要提高数据加载的速度,可以通过增加乘法器的数量来实现。

2.2 提高滤波器的实时性

对于上述通用滤波器,虽然可以通过增加系数加载控制电路的并行度来提高系数加载的速度,但是在系数加载的过程中仍然不能进行数据处理。对于N阶滤波器,每次加载系数需要向查找表中存入2N个计算结果,将上述数据存入一个查找表至少需要2N个时钟。滤波器阶数越高,改变滤波特性时需要等待的时间越长,极大地限制了通用滤波器在实时系统中的应用。参考对数据采样处理时使用的方法,在这里可以使用乒乓操作[6]以提高滤波器的实时性。乒乓操作是一个常用于数据流控制的处理技巧,通过两个数据缓冲区将数据输入缓冲区与从缓冲区输出数据两个操作分开,在输入选择器和输出选择器相互配合下将经过缓冲后的数据连续不断地送入数据处理单元。

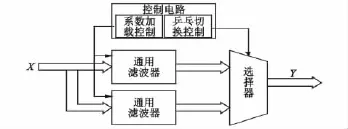

如图5所示,同时采用两个通用滤波器,通过选择器对输出的滤波器结果进行切换输出。由于两个通用滤波器在任何时刻都会有一个滤波器工作,因而可以对数据进行实时处理,滤波器功能切换只需要一个时钟即可完成;同时每次都只有一个滤波器进行数据加载,因而使两个通用滤波器共用一个系数加载控制电路,这样可以减少一个系数加载控制电路占用的逻辑资源。

图5 实时FIR滤波器实现原理Fig.5 Principle of real-time FIR filter

3 实验验证

选用DSP Development Kit作为实验平台,其中FPGA芯片型号为EP2C70F672C6;使用嵌入在Matlab中的DSP builder软件搭建电路模型,采用硬件回环测试方法进行实验验证。首先进行电路模型仿真,然后对模型编译实现电路,在JTAG模式下通过USBblaster将程序下载到FPGA芯片中,仿真源信号由Matlab提供,测试结果再通过USBblaster传回到Matlab中进行显示。硬件回环测试方法可很好地利用Matlab众多的仿真源以及友好的显示界面。

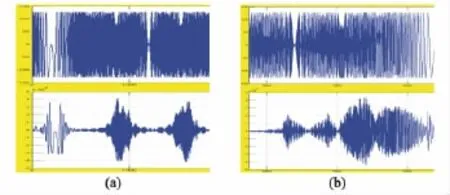

存储器中存储多组滤波器系数,位宽为8位,分别实现64阶的低通、高通、带通以及带阻滤波器,由控制电路通过依次加载4组系数来实现上述4种功能。当滤波器的RAM中加载入不同的系数时,滤波器选通的频带也随之发生变化。Matlab提供的仿真信号为线性调频信号,频率变化范围为0~20 MHz,重复周期为5μs。

如图6所示,(a)、(b)上半部分为周期性变化的线性调频信号,频率调制规律为三角波调制;(a)、(b)下半部分为通用实时滤波器的输出结果。从图6(a)中可以看到,滤波器开始为低通滤波器,将线性调频信号的低频部分输出;然后转变为带通滤波器,输出频率更高的信号。由于调频信号为三角波调制,带通滤波器输出结果具有对称性。图6(b)显示的结果表明滤波器从高通滤波器变为带通滤波器,然后再转变为低通滤波器;在转变为低通滤波器时,输出结果快速转变,不存在时间差。相比于传统DA算法实现的FIR滤波器,文中设计的通用滤波器不需要为每一种滤波器特性重复耗费存储乘积结果的查找表,极大地节省了实现滤波器的资源;随着滤波器系数的增加,这种效果将更加明显。

图6 硬件回环测试结果Fig.6 Results of test with hardware in loop

4 结论

本文在对DA算法研究的基础上,设计了基于分布式算法的有限长单位冲激响应滤波器。文中提出将实现算法中的ROM变换为RAM,通过加载不同的滤波器系数实现通用滤波器的设计;并采用乒乓操作的方法,解决了滤波器由于加载系数需要时间而造成的难以实时工作问题。硬件回环测试结果表明:滤波器能以较少逻辑资源实现多种滤波器特性及对数据处理的无缝交接,满足系统的实时性要求。

[1]戴敬,王超.基于FPGA多级分布式算法的FIR数字滤波器的设计[J].沈阳建筑大学学报(自然科学版),2010,26(1):196-200.DAI Jing,WANG Chao.The design of multi-channels distributed arithmetic algorithm FIR ailter based on FPGA[J].Journal of Shenyang Jianzhu University,2010,26(1):196-200.

[2]FREENY S L.Special purpose hardware for digital filtering[J].Proc IEEE,1975,4(6):633-648.

[3]Meyer Baese U.Digital Signal Processing with Field Programmable Gate Arrays[M].Third Edition.US:Springer,2007.

[4]陈亦欧,李广军.采用分布式算法的高速FIR滤波器ASIC设计[J].微电子学,2007,37(1):144-146.CHEN Yiou,LI Guangjun.Design of a high speed FIR filter ASIC using distributed arithmetic[J].Microelectronics,2007,37(1):144-146.

[5]高西全,丁玉美.数字信号处理[M].第二版.北京:电子工业出版社,2010.

[6]吴继华,王诚.Altera FPGA/CPLD设计[M].高级篇.北京:人民邮电出版社,2005.