基于锁相环的频率合成器设计和显示

2012-11-26张启军

程 伟,张启军

(湖北科技学院 电子与信息工程学院,湖北 咸宁 437100)

0 引言

众所周知,频率合成技术在电子设计领域里扮演着非常重要的角色。在一些高端电子设备系统如通信、雷达、测控、仪器表等电子系统都包含有频率合成技术。如果没有频率合成技术,微处理器处理数据的能力至少要慢几十个甚至上百个节拍,远远达不到现代社会对处理数据高标准的要求,也无法实现高速信息化产业的建设[1]。

1 系统方案设计与论证

频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。并且输出频率的准确度不逊于前两种,因此采用锁相频率合成。

晶体振荡器输出的信号频率f1,经分频后(M分频)得到基准频率,输入锁相环的相位比较器(PC)。锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f2/N,当N变化时,或者N/M变化时,就可以得到一系列的输出频率f2。然后把f2输入到单片机的管脚,采用外部中断的方式进行脉冲,把数据显示在数码管上[2]。系统原理框图如下:

图1 系统原理框图

2 主要电路设计

2.1 1K信号源的设计

在信号源设计中,采用了16M的有源晶振。16M有源晶振在压电效应下产生频率为16M的正弦波,然后经74hc04缓冲,再经CD4060分频8000次,从而得到了2K的信号源。

图2 信号源线路图

2.2 频率合成电路设计

锁相环CD4046的工作原理简介:输入信号fi从CD4046的14脚输入后,经内部放大器进行放大、整形后加到相位比较器的输入端,而相位比较器将从3脚输入的比较信号f0与输入信号fi作相位比较,从相位比较器输出的误差电压则反映出两者的相位差φ经R1、R2及C1滤波后得到控制电压Ud加至压控振荡器VCO的输入端9脚,从而调整VCO的振荡频率f1,使其接近fi。

在频率合成部分中,将CD4017的RESET(15脚)分别接“2”、“3”,……“9”,则4017就成为“二”、“三”、……“九”等分频器,将VCO的振荡频率经可预置分频器CD4017,就可以组成了2~9KHz的频率合成器。

图3 频率合成线路图

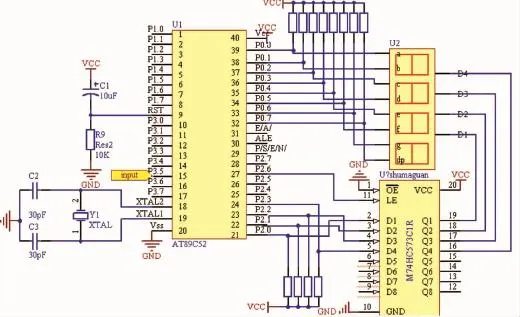

2.3 单片机显示电路设计

经锁相环CD4046的4管脚出来的脉冲信号直接输入到单片机的外部计数器T1,用T0做定时器定时1秒计外部脉冲个数,再把得到的数据用数码管显示出来[3]。

图4 单片机显示电路设计图

3 系统软件工作流程图

系统的软件设计采用C语言,对单片机进行编程实现测量和显示功能。

图5 软件工作流程图

4 系统调试

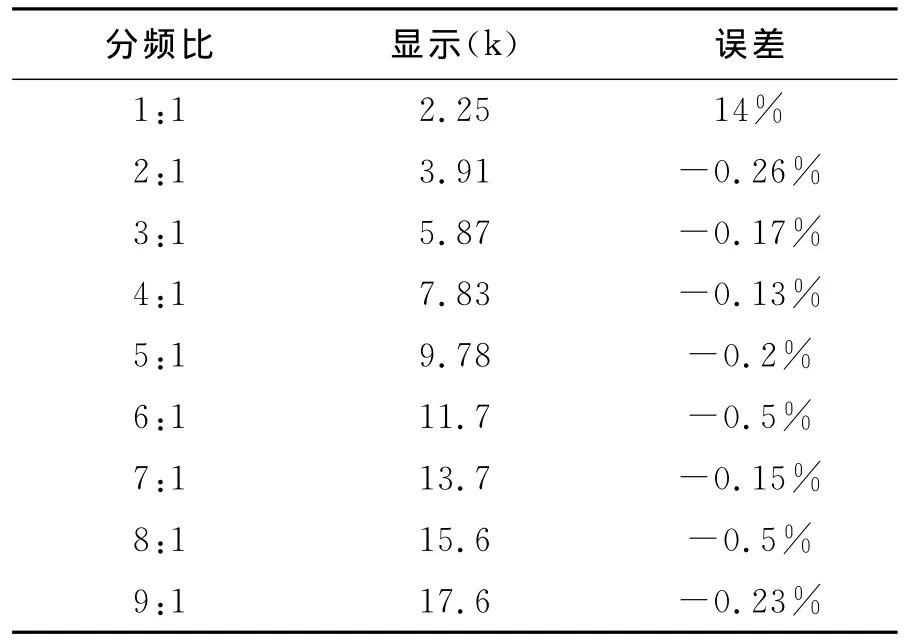

用示波器测得信号源的频率为1.96K幅值为5.0v的稳定方波信号。切换分频比,得到的显示数据如下:

分频比 显示(k) 误差1:1 2.25 14%2:1 3.91 -0.26%3:1 5.87 -0.17%4:1 7.83 -0.13%5:1 9.78 -0.2%6:1 11.7 -0.5%7:1 13.7 -0.15%8:1 15.6 -0.5%9:1 17.6 -0.23%

从以上数据可以分析,通过切换CD4017的分频比,基本上得到了设计的要求,不足之处在于显示的数据和理论值之间稍微有点偏差,究其原因,一是经分频得到的信号源频率不是特别精确,二是锁相环CD4046输出频率的准确度及分辨率不是很高。

[1]王福昌.锁相技术[M].武汉:华中大学出版社,2009.

[2]杨 阳,罗 马.基于锁相环的十二脉冲整流触发电路[J].青岛大学学报(工程技术版),2012,27(3):12-15.

[3]郭天祥.新概念51单片机C语言教程[M].北京:电子工业出版社,2009.